Fターム[5F152LN22]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 熱処理 (195) | 高温 (57)

Fターム[5F152LN22]に分類される特許

1 - 20 / 57

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板

【課題】GaN結晶インゴットを含む窒化物系化合物半導体結晶から自立基板を切り出す際のクラックの発生を抑制した窒化物系化合物半導体結晶及びその製造方法並びにIII族窒化物半導体デバイス用基板を提供する。

【解決手段】窒化物系化合物半導体結晶としてのGaN結晶インゴット100は、厚さ方向に沿って外周領域100aとその内側の中心領域100bとを有し、外周領域100aの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最大値が、中心領域100bの厚さ方向に垂直な面(Ga極性のc面101)の転位密度の最小値の2.0倍以上20倍以下となる転位密度分布を有する。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

エピタキシャル成長用基板およびエピタキシャル成長用基板の製造方法

【課題】平坦性、結晶性および配向性に優れ、厚さ方向の熱伝導率が高く放熱性に優れたエピタキシャル成長用基板およびその製造方法を提供する。

【解決手段】炭素基板の少なくとも一方の主表面に、算術平均表面粗さRaが0.05μm以下で、表面粗さの最大値Ryが0.5μm以下であり、X線回折法による(0002)面のロッキングカーブの半値幅が1.5度以下であり、ラマンスペクトルにおけるGバンドのピーク強度に対するDバンドのピーク強度の比が0.01以下である高結晶グラファイト層を形成してなることを特徴とするエピタキシャル成長用基板である。

(もっと読む)

化合物半導体基板

【課題】基板の反りの低減とデバイスの高速性を高いレベルで実現することのできる化合物半導体基板を提供する。

【解決手段】

Si単結晶の基板と、基板の主面上に形成された窒化物半導体の中間層と、中間層の主面上に形成された窒化物半導体の化合物半導体層からなり、基板の酸素濃度が0.2×1018atoms/cm3以上1.4×1018atoms/cm3以下であり、抵抗値が1000Ωcm以上であり、前記中間層と前記化合物半導体層を合計した、主面と垂直方向の膜厚が450nm以上4500nm以下であることを特徴とする化合物半導体基板。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法及び半導体基板を提供すること。

【解決手段】シリコン基板11の上面に多孔質な多孔質シリコン層12を形成する工程と、水素ガス及び炭化水素系ガスの混合ガスまたは炭化水素系ガスを供給し、多孔質シリコン層12の表面を結晶化及び炭化して炭化珪素膜13を形成する工程と、を備える。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

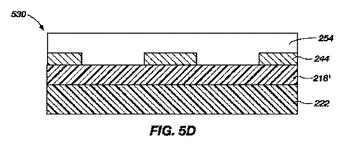

低減した格子ひずみを備えた半導体材料、同様に包含する半導体構造体、デバイス、および、加工された基板を製造する方法

半導体装置を製作する方法または構造体は、従順な材料の層の上に横たわっている半導体材料の構造体を形成することを含み、その後半導体材料構造体を緩和させる従順な材料の粘性を変えて、緩和した半導体材料の連続層を形成する際の種子層として、緩和した半導体材料構造体を利用する。ある実施形態では、半導体材料の層は、III-Vタイプ半導体材料(例えばインジウム窒化ガリウム)から成る。新しい中間構造体が、この種の方法の間、形成される。加工された基板は、緩和した格子の構造体を有する半導体材料の連続層を含む。  (もっと読む)

(もっと読む)

エピタキシャル基板用シリコンウェハの製造方法及びエピタキシャル基板の製造方法

【課題】エピタキシャル成長時のオートドーピングおよびミスフィット転移発生を抑制するエピタキシャル基板用シリコンウェハの製造方法を提供する。

【解決手段】エピタキシャル基板用シリコンウェハの製造方法は、1E19atoms/cm3以上のボロンを含有するシリコンウェハ101を熱酸化処理し、シリコンウェハ101の表面にシリコン酸化膜102を形成する第一の工程S101と、シリコン酸化膜102を剥離する第二の工程S102と、シリコンウェハ101を、水素雰囲気中において熱処理する第三の工程S103とを備える。これにより、シリコンウェハ101内部の不純物濃度を高濃度に保持したまま、表層の不純物濃度を著しく低減させられる。したがって、不純物濃度プロファイルに優れ、かつミスフィット転位の少ないエピタキシャル成長膜を成長させられる基板用シリコンウェハを製造することができる。

(もっと読む)

選択した格子定数または制御した格子定数を有する半導体材料の層を使用する半導体構造または半導体デバイスを製造する方法

半導体構造または半導体デバイスを製造する方法は、ある温度で半導体材料の層をもう1つの材料にボンディングすること、および半導体材料の層の温度をその後で変化させることを含む。もう1つの材料を、ある熱膨張係数を示すように選択することができ、半導体材料の層の温度が変化するときに、制御した格子定数および/または選択した格子定数が半導体材料の層に与えられるまたはその中に保持される。ある実施形態では、半導体材料の層は、例えば、窒化インジウムガリウムなどのIII−V型半導体材料を含むことができる。新規な中間構造が、かかる方法の間に形成される。エンジニアド基板は、高温で前に得た半導体材料の層の平均格子定数に近い室温における平均格子定数を有する半導体材料の層を含む。  (もっと読む)

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】格子緩和又は一部格子緩和した歪緩和SiGe層の形成を可能にし、これによって転位欠陥を少なくするようにした半導体基板の製造方法及び半導体基板を提供する。

【解決手段】Si基板10上に絶縁層11を介してSiGe層を備えた半導体基板の製造方法である。Si基板上に前記絶縁層11を介してSi層12を備えたSOI基板13のSi層12上に、第1のSiGe層14を形成するSiGe成膜工程と、SiGe成膜工程後、熱処理を施し、第1のSiGe層14中のGeをSi層12中に拡散・濃縮させ、SiGe層となる第2のSiGe層16を形成する拡散工程と、を有する。第1のSiGe層形成工程では、第1のSiGe層14中のGe濃度を5%以下にする。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

窒化物系III−V族化合物半導体装置の製造方法

【課題】バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

(もっと読む)

単結晶薄膜を有する基板の製造方法

【課題】特別な基板を用いなくても結晶欠陥がほとんど無い単結晶薄膜を有する基板を容易に製造することができる方法を提供することを目的とする。

【解決手段】少なくとも、ドナー基板とハンドル基板を準備する工程Aと、前記ドナー基板上に単結晶層を積層成長させる工程Bと、前記単結晶層が形成されたドナー基板の単結晶層中にイオン注入してイオン注入層を形成する工程Cと、前記イオン注入されたドナー基板の単結晶層の表面と前記ハンドル基板の表面を貼り合わせる工程Dと、前記貼り合わせられたドナー基板の前記単結晶層中のイオン注入層で剥離する工程Eとにより前記ハンドル基板上に単結晶薄膜を形成し、少なくとも、前記単結晶薄膜が形成されたハンドル基板をドナー基板として前記A〜Eの工程を繰り返すことを特徴とする単結晶薄膜を有する基板の製造方法を提供する。

(もっと読む)

1 - 20 / 57

[ Back to top ]