Fターム[5F152NP08]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 半導体 (836) | 3−5族 (413) | InGaAs (25)

Fターム[5F152NP08]に分類される特許

1 - 20 / 25

半導体装置、半導体装置の製造方法

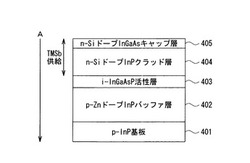

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

半導体基板の製造方法

【課題】選択エッチング層のエッチング時の自然酸化による影響で化合物半導体層の損傷、結晶の転移が発生せず、信頼性の高い半導体基板の製造方法を提供する。

【解決手段】化合物半導体基板8上に、選択エッチング層3、応力緩和層9および応力緩和層9より大きいヤング率を有するIII−V族化合物半導体から成る化合物半導体層4をエピタキシャル成長法により順次積層させる積層工程と、選択エッチング層3、応力緩和層9および化合物半導体層4を所定パターンとなるようにエッチング除去するエッチング工程と、Si基板5の主面に化合物半導体層4の上面を直接接合法により接合させて、選択エッチング層3、応力緩和層9および化合物半導体層4が積層された化合物半導体基板8を貼りあわせる接合工程と、前記エッチング工程で残った選択エッチング層3をさらにエッチング除去することにより、Si基板5と化合物半導体基板8とを分離する分離工程とを含む。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

センサ、半導体基板、および半導体基板の製造方法

【課題】効率よく光電変換ができる光吸収体を有する半導体基板、半導体基板の製造方法、および当該半導体基板を含む光センサを提供する。

【解決手段】シリコンを含むベース基板と、ベース基板上方に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備え、光熱吸収体が、光熱吸収体に入射する入射光または光熱吸収体に加わる熱に応じて電気信号を出力するセンサを提供する。また、シリコンを含むベース基板と、ベース基板の上方に形成され、ベース基板の表面を露出する開口を有し、結晶成長を阻害する阻害体と、開口の内部に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備える半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

磁性半導体素子

【課題】基板と格子整合し、キュリー温度Tcが室温であるII−IV−V2族化合物磁性半導体材料で量子井戸層あるいは強磁性電極を構成した磁性半導体素子を提供する。

【解決手段】

磁性半導体素子10は、InPからなる基板11と、Mnが添加されたZnSnAs2からなりかつ基板11の上に結晶成長された量子井戸層13と、InAlAs及び/又はInGaAsからなり基板11の上に結晶成長されかつ量子井戸層13を挟持する一組の障壁層12,14と、を備える。障壁層12,14にInAlAsを採用した場合、Al組成は0.43〜0.53%であることが好ましくは、InGaAsを採用した場合、Ga組成が0.42〜0.52%であることが好ましい。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

半導体基板およびその製造方法、ならびに半導体装置

【課題】圧縮歪層と引張歪層とを利用して、InP系半導体デバイスを成長させるメタモルフィック基板の欠陥(例えば転位)の低減を可能にする。

【解決手段】ガリウムヒ素基板100と、前記ガリウムヒ素基板100上に形成されたバッファ層101と、前記バッファ層101上に、前記バッファ層101よりも面内方向の格子定数が小さい材料からなる引張歪層105aと、前記バッファ層101よりも面内方向の格子定数大きい材料からなる圧縮歪層105bとを積層して形成された歪補償構造層105とを有することを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置および電子機器

【課題】InP基板に擬似格子整合もしくは格子整合させたデバイス層を形成し、そのデバイス層よりInP基板を剥離して、InP基板の再利用を可能とする。

【解決手段】インジウムリン(InP)基板11上に擬似格子整合もしくは格子整合する犠牲層12を形成する工程と、前記犠牲層12上にデバイス層13を形成する工程と、前記犠牲層12を除去することで前記InP基板11と前記デバイス層13とを分離する工程とを備えたことを特徴とする。

(もっと読む)

半導体ヘテロ構造

【課題】より小さな表面凹凸をもつ半導体ヘテロ構造を提供すること。

【解決手段】本発明は、第1の面内格子定数をもつ支持基板と、該支持基板上に形成されていて、上部に格子緩和状態おいて第2の面内格子定数をもつ緩衝構造と、および該緩衝構造上に形成された組成非傾斜層の多層積層とを備えた半導体ヘテロ構造に関するものである。表面凹凸の少ない、前記のタイプの半導体ヘテロ構造を提供することが本発明の目的である。前記の目的は、該組成非傾斜層が歪み層であり、かつ、該歪み層が前記第1および第2の格子定数の中間の第3の面内格子定数を格子緩和状態において有する半導体材料の、歪を有する平坦化層を少なくとも1つ含んで構成されることを特徴とする、前記のタイプのヘテロ構造によって達成される。

(もっと読む)

歪み薄膜の緩和方法

本発明は、歪み薄膜を緩和するための方法に関する。歪み薄膜は、初期支持体の第一の主面によって固定され、薄膜の第二の主面は接触面として知られ、この方法は、以下の連続するステップを有している:

---接触面として知られている主自由面を具備し、ポリマーの熱膨張率が薄膜のそれよりも大きいポリマー層を有する中間支持体を提供するステップと、

---歪み薄膜の接触面とポリマー層の接触面とを接着して接触させるステップと、

---初期支持体(9)を取り除くことによって、しわの形成によって薄膜(8)の緩和を引き起こし、薄膜の第一の主面を露呈させるステップと、

---緩和させられた薄膜(8)を伸ばして、しわを取り除くために、ポリマー層(2)の温度を増加させるステップと、

---受け入れ基板(10)の一つの面で薄膜(8)の第一の主面を固定するステップと、

---受け入れ基板と一体になった緩和させられた薄膜を得るために、中間支持体を取り除くステップ。  (もっと読む)

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 熱伝導性が改善された、メタモルフィックバッファ層を有するヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にエピタキシャル成長法によって、メタモルフィックバッファ層2を形成し、その上にコレクタ層3、ベース層4、エミッタ層5、およびエミッタキャップ層6を順次積層し、コレクタ電極7をメタモルフィックバッファ層2の上部層2cに接して設ける。メタモルフィックバッファ層2には、結晶成長中における不純物ドープ法によって、従来のサブコレクタ層と同等またはそれ以上の不純物を導入し、メタモルフィックバッファ層2がコレクタ電流をコレクタ電極7へ導く役割を果たすことができるようにする。熱抵抗の大きい三元混晶などで形成されることの多いサブコレクタ層を省略できるので、半導体装置内で発生した熱を速やかに基板1へ放熱することができる。

(もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

1 - 20 / 25

[ Back to top ]