Fターム[5H420NC33]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 基準生成部、出力部以外/全体の構成 (1,615) | その他の特徴 (129) | 集積化 (37)

Fターム[5H420NC33]に分類される特許

1 - 20 / 37

半導体集積回路、および、半導体記憶装置

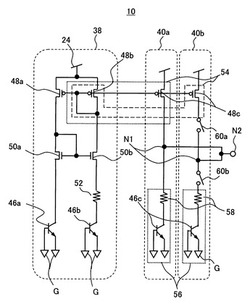

バンドギャップ参照電源回路および非接触型デバイス

【課題】バンドギャップ参照電源回路の応答を速くすること。

【解決手段】温度係数が正の絶対温度比例電流を生成する絶対温度比例電流生成回路と、前記絶対温度比例電流のミラー電流を生成するミラー電流生成部と、前記ミラー電流に基づいて生成される温度係数が正の絶対温度比例電圧及び係数が負の相補的電圧から温度係数の絶対値が前記絶対温度比例電圧より小さいバンドギャップ参照電圧を生成するバンドギャップ参照電圧生成部とを有し、前記ミラー電流生成部と前記バンドギャップ参照電圧生成部の間の接続ノードから共通の出力ノードに接続され、当該出力ノードから前記バンドギャップ参照電圧を出力する複数のバンドギャップ参照電圧出力回路とを有し、前記複数のバンドギャップ参照電圧出力回路のうちの一部の回路は、前記ミラー電流生成部と前記接続ノードの間及びバンドギャップ参照電圧生成部と前記接続ノードの間それぞれに設けられた1及び第2のスイッチ回路を有すること。

(もっと読む)

半導体集積回路

【課題】電源回路が発熱により破壊されることを抑制する、電源回路の発熱による破壊を抑制する保護回路を提供する、占有面積の小さい保護回路及び電源回路を得る、作製コストの低い保護回路及び電源回路を得る。

【解決手段】電圧変換回路と、分圧回路及び保護回路を有する制御回路とを有し、保護回路は、温度が上昇するとオフ電流が増大する第1の酸化物半導体トランジスタと、オフ電流を電荷として蓄積する容量素子と、第2の酸化物半導体トランジスタと、非反転入力端子に参照電圧が入力されるオペアンプとを有し、第1の酸化物半導体トランジスタは、電圧変換回路又は制御回路の発熱する素子に隣接して配置される電源回路に関する。

(もっと読む)

低電圧参照回路

【課題】低電圧で動作する参照回路を提供すること。

【解決手段】低電圧参照回路は、一対の半導体装置を有し得る。各半導体装置は、n型半導体領域と、n型半導体領域におけるn+領域と、メタルゲートと、ゲート絶縁体とを有し得る。ゲート絶縁体は、メタルゲートとn型半導体領域との間に挿入され、メタルゲートとn型半導体領域とを通りキャリアはトンネリングする。メタルゲートは、p型ポリシリコンの仕事関数と整合する仕事関数を有し得る。ゲート絶縁体は、約25オングストロームより薄い厚さを有し得る。メタルゲートは、第一の端子を半導体装置に対して形成し得る。n+領域およびn型半導体領域は、第二の端子を半導体装置に対して形成し得る。第二の端子は、接地に結合され得る。バイアス回路は、異なる電流を半導体装置に供給するために第一の端子を用い得、対応する参照出力電圧を1ボルト未満の値で提供し得る。

(もっと読む)

特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器

【課題】特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器を提供する。

【解決手段】電圧調整器は、電流ミラーとして接続されていて、電源Vddに接続可能な3個のトランジスタP1、P2、P3の第1組41と、電流ミラーとして接続された2個のトランジスタN1、N2の第2組であって、各トランジスタが第1組のトランジスタに直列に接続されているトランジスタの第2組とを含み、第2組の第1トランジスタN1が、第1組の最後のトランジスタP3に直列に接続されたトランジスタN4に電流ミラーとして接続されたトランジスタN3Rに直列に接続されている。トランジスタN3Rは自身の線形領域で動作し、発生される電流の値は当該トランジスタの等価抵抗に依存し、2個のトランジスタが超長チャネルを有することにより比率L/Wが極めて大きい。

(もっと読む)

基準電流源回路

【課題】従来技術に比較して、回路面積を削減し、出力電流の温度特性が室温においてゼロになるように制御することができる基準電流源回路を提供する。

【解決手段】基準電流源回路1において、追加バイアス電圧生成回路10は、出力電流IREFが温度変化に対して一定となるように追加バイアス電圧VSRを生成する。ドレインバイアス電圧生成回路DB1は、サブスレッショルド飽和領域で動作するnMOSトランジスタMN21及びMN22を備え、ドレインバイアス電圧を生成し、当該ドレインバイアス電圧に追加バイアス電圧VSRに加算して、加算結果の電圧をMOS抵抗MRのドレインに印加する。

(もっと読む)

半導体集積回路、該回路を備えるスイッチング電源及び該電源を備える制御システム

【課題】寄生素子の動作を起因とする不安定動作を防ぐことができる、半導体集積回路を提供すること。

【解決手段】入出力を異なる電流値にする入出力比特性を有するカレントミラーを構成する一対のトランジスタ(63,65)と、前記カレントミラーの出力電流に応じて基準電圧を生成する出力トランジスタとを備える半導体集積回路であって、一対のトランジスタ(63,65)のうち前記電流値が小さい方のトランジスタ63側のコレクタ領域85Aの総面積と一対のトランジスタ(63,65)のうち前記電流値が大きい方のトランジスタ65側のコレクタ領域82と88とを合わせた総面積とが等しくなるように構成されたことを特徴とする、半導体集積回路。

(もっと読む)

低電力基準電圧およびバイアス電流発生器のための方法および回路

低電力で動作可能であり、プロセスばらつきの影響を受けにくく、占有するシリコン面積が少なく、ノイズが少ない、抵抗器無しのPTATセルを得るためのシステムおよび方法が提供される。さらに、カスケード接続のユニットセルによって基準電圧および基準電流を一定比率で増大させるためのシステムおよび方法が提供される。さらに、PTAT構成要素が微調整されるシステムおよび方法が提供され、有利なことにプロセスばらつきが少なくなり、温度の影響を受けにくくなる。  (もっと読む)

(もっと読む)

基準電圧発生回路装置

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

電源回路及び電源安定化方法

【課題】基準電位の変動を抑制し、生成すべき内部電位の安定化を図る。

【解決手段】基準電位を生成する基準電位回路と、電源電位を昇圧して所望の内部電位を生成する昇圧回路とを備え、該昇圧回路は、内部電位に対応する電位と基準電位との比較結果を動作制御信号として出力する比較回路と、動作制御信号によって動作オン/オフが制御されると共に基準電位を一方の入力とする差動増幅回路と、動作制御信号に応じてオン/オフし差動増幅回路の出力電位をリセットするスイッチ素子とを含む電源回路であって、前記差動増幅回路及びスイッチ素子のオン期間が長くなるように前記動作制御信号の信号幅を変換する信号幅変換回路を備える。

(もっと読む)

半導体装置及びRFIDタグチップ

【課題】トリミングを要すことなく、かつ、バンドギャップリファレンス回路のデッドロック発生を防止する参照電源回路を提供する。

【解決手段】本発明に関連するRFIDタグチップはバンドギャップリファレンス回路10とVth差リファレンス回路11を切り替えるスイッチ12を有する参照電源100を有する。バンドギャップリファレンス回路10のバンドギャップリファレンス内基準電位とVth差リファレンス回路11の出力とを比較器で対比し、スイッチとして動作するトランジスタ14を制御することで、バンドギャップリファレンス内基準電位を上昇させ、バンドギャップリファレンス回路10の立ち上がりを早めると共に、バンドギャップリファレンス回路のデッドロック発生を防止する。

(もっと読む)

電源遮断制御回路および電源遮断制御方法

【課題】リーク電流の大きさに基づいた集積回路の電源遮断の制御をする電源遮断制御回路および電源遮断制御方法を提供する。

【解決手段】集積回路の基本回路をモデル化したモデル回路を含むモデル回路部と、前記モデル回路で生じたリーク電流によって充電される出力電圧と予め設定された基準電圧とを比較する電圧比較回路部と、前記比較結果から前記出力電圧が前記基準電圧に達するまでの到達時間を計測し、該計測結果から前記リーク電流の大きさを判定する判定回路部と、前記判定されたリーク電流の大きさに基づいて、前記集積回路の電源遮断を制御する電源遮断制御回路部と、を備える、電源遮断制御回路。

(もっと読む)

低電圧検出回路および電源制御用半導体集積回路

【課題】電源電圧のリニアな変化に対して階段波形状に変化するような参照電圧を発生する定電圧回路を備えた低電圧検出回路において、誤って検出信号が出力されてしまうのを回避できるようにする。

【解決手段】所定の電位の参照電圧を発生する定電圧回路(33)と、電源電圧に比例した電圧と前記参照電圧とを比較して電源電圧が所定の電位よりも高いか低いかを判定して高い場合には第1のレベルのまた低い場合には第2のレベルの検出信号を出力する電圧比較手段(32)と、を備え、定電圧回路は電源電圧のリニアな変化に対して階段波形状の特性の参照電圧を発生し、電圧比較手段は電源電圧が所定の電位よりも低い領域で誤検出信号を出力するおそれがある低電圧検出回路において、電源電圧が誤検出信号の生じる範囲にあることを検出可能な誤動作範囲検出回路(34)を設け、電圧比較手段からの検出信号の出力を禁止可能に構成した。

(もっと読む)

充電制御用半導体集積回路

【課題】電流制御用MOSトランジスタに流れる電流をカレントミラー方式で検出して制御する充電制御用ICにおいて、トランジスタのサイズ比がばらついても電流検出精度を向上させることができるようにする。

【解決手段】カレントミラー方式の電流検出回路(13)に、バイアス状態制御用トランジスタ(Q3)と、電流制御用トランジスタ(Q1)と電流検出用トランジスタのドレイン電圧を入力とする演算増幅回路(AMP1)とを設け、該演算増幅回路の出力に基づいて電流検出用MOSトランジスタのバイアス状態が、電流制御用MOSトランジスタのバイアス状態と同一になるように構成するとともに、電流制御用トランジスタと電流検出用トランジスタの各ドレイン電極から演算増幅回路の対応する入力点までの配線の寄生抵抗による電圧降下が同一となるように、電流検出用トランジスタのドレイン配線の長さを調整するようにした。

(もっと読む)

カレントミラー回路

【課題】 プロセスの変動があったとしても、ヒューズトリミングを用いてミラーされた出力電流量を微調整することで精度の良いカレントミラー比が得られるカレントミラー回路の構成を提供する

【解決手段】 ミラー比1:100のカレントミラー回路において第2のMOSトランジスタのゲート幅を第1のMOSトランジスタの90倍で構成し、第1のMOSトランジスタの20倍分を細かく分割して第3のMOSトランジスタ群として第2のMOSトランジスタに並列に接続し、第3のMOSトランジスタ群に直列にトリミング工程にて切断可能なヒューズを接続することを特徴とする。

(もっと読む)

電圧発生回路

【課題】安定化キャパシタの容量を削減しながら、降圧トランジスタのゲート電圧変動を抑制する。

【解決手段】電圧発生回路30には、差動増幅回路1、ゲート電圧安定化回路2、Nch MISトランジスタNT1、Nch MISトランジスタNT2、Nch MISトランジスタNT11乃至13、Nch MISトランジスタNTT1、Nch MISトランジスタNTT2、Pch MISトランジスタPT11乃至13、Pch MISトランジスタPTT1、Pch MISトランジスタPTT2、抵抗RA1乃至RA4、抵抗RS1乃至RS4、及びキャパシタC1が設けられる。ゲート電圧安定化回路2は、スタンバイ状態からアクティブ状態、或いはアクティブ状態からスタンバイ状態に変化するとき降圧トランジスタであるNch MISトランジスタNTT1のゲート電圧の変化を抑制する。

(もっと読む)

電源回路及びそれを用いた内部電源電圧発生方法

【課題】電源電圧が低下しても所定の基準電圧を生成する。

【解決手段】電源回路40には、パワーオン/オフ回路1、BGR回路用電源電圧発生部2、バンドギャップリファレンス回路3、VINT発生回路4、VPP発生回路5、VAA発生回路6、及び1/2VAA発生回路7が設けられる。BGR回路用電源電圧発生部2には、参照電圧発生回路2a及びBGR回路用電源電圧発生回路2bが設けられる。参照電圧発生回路2aは、パワーオン信号Spwonが入力され、参照電圧Vsn1及び制御電圧Vcmbを生成する。参照電圧Vsn1は、外部高電位側電源Vdd電圧が0.8Vから4Vの範囲で、低温から高温領域まで、外部高電位側電源Vdd電圧依存性がなく、略一定な電圧である。BGR回路用電源電圧発生回路2bは、参照電圧Vsn1及び制御電圧Vcmbが入力され、参照電圧Vsn1を昇圧した、例えば2VのBGR回路用電源電圧Vsn2を生成する。

(もっと読む)

定電流源回路

【課題】出力電圧の変化に伴う出力電流の変動がなく、かつ出力電圧が低い場合においても、より低い電圧まで動作可能な定電流源回路を提供する提供する。

【解決手段】本発明の定電流源回路は、出力電流を出力する出力端子の電圧を検出し、該検出した電圧から制御電圧を生成する制御電圧生成部と、制御電圧により基準電流の電流量を調整する基準電流調整部と、調整された基準電流に応じた出力電流を出力するカレントミラー部とを有する。

(もっと読む)

電圧供給回路および半導体メモリ

【課題】 半導体メモリのスタンバイ状態での消費電力を増大させることなく、出力電圧の変動に対する応答速度および発振に対する安定性を確保したうえで、半導体メモリの動作状態に応じてプリチャージ電圧用の電圧供給回路の駆動能力を制御する。

【解決手段】 第1電圧供給部にて、第1差動増幅器は、出力ノードの電圧が第1電圧より低いときに出力信号を活性化させ、第2差動増幅器は、出力ノードの電圧が第2電圧より高いときに出力信号を活性化させ、第1駆動回路は、第1差動増幅器の出力信号の活性化に応答して出力ノードを高電源線に接続し、第2差動増幅器の出力信号の活性化に応答して出力ノードを低電源線に接続する。第2電圧供給部にて、第3差動増幅器、第4差動増幅器および第2駆動回路は、駆動能力制御信号の活性化期間にのみ、第1差動増幅器、第2差動増幅器および第1駆動回路と同様に動作する。

(もっと読む)

バンドギャップ基準電圧発生回路

【課題】光照射による電圧変動が低減されたバンドギャップ基準電圧発生回路を提供する。

【解決手段】第1導電型の半導体からなる基板と、前記基板上に形成された第1のトランジスタと、前記基板上に形成され、前記第1のトランジスタに対してベースが共通に接続された第2のトランジスタと、前記基板上に形成され、第2導電型を有し、前記第2のトランジスタのコレクタ層と前記基板との間に並列に接続された光吸収領域と、前記第1及び第2のトランジスタの前記ベースに共通接続された基準電圧出力端子と、を備え、前記第1のトランジスタのコレクタ層の面積は、前記第2のトランジスタの前記コレクタ層の面積よりも大きいことを特徴とするバンドギャップ基準電圧発生回路が提供される。

(もっと読む)

1 - 20 / 37

[ Back to top ]