Fターム[5H430EE07]の内容

トランジスタを用いた連続制御型電源 (9,660) | 主制御部 (1,336) | 複数の主制御回路あり (185)

Fターム[5H430EE07]の下位に属するFターム

直列接続されているもの (62)

並列接続されているもの (92)

Fターム[5H430EE07]に分類される特許

1 - 20 / 31

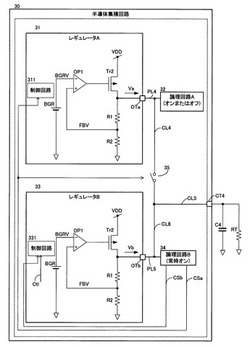

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

電源装置

【課題】電源入力電圧の不足による出力電圧の低下を極力抑える。

【解決手段】電源入力電圧VBがしきい値電圧Vthより高い場合、コンパレータ20はLの比較信号Scを出力し、トランジスタ16、23はオフする。電源入力電圧VBがしきい値電圧Vthよりも低下すると、コンパレータ20はHの比較信号Scを出力し、トランジスタ16、23はオンする。その結果、出力電圧VoはVB−1VからVB−VCE(sat)に引き上げられる。この間、オペアンプ7はトランジスタ4に対しオン駆動信号を出力し続けるので、電源入力電圧VBが上昇してトランジスタ16がオフした時にトランジスタ4が直ちにオンする。

(もっと読む)

半導体装置

【課題】外部から供給される電源電圧に依存しない定電圧で動作する内部回路と電源電圧で動作する内部回路とを備え、外部から供給される電源電圧が大きく変動した場合の誤動作の発生を抑制する半導体装置を提供する。

【解決手段】内部回路と、外部から供給される電源電圧の変動に対して安定化された内部電圧を発生し、内部回路に供給する内部電圧発生回路と、を備え、内部電圧発生回路は、電源電圧が所定値を超えて上昇した場合に、内部電圧に対する安定化動作を停止し、内部電圧が電源電圧の上昇に伴い大きくなるように制御する。

(もっと読む)

電源回路

【課題】回路規模を増大させることなく、要求に応じた複数の電源を選択的に生成すること。

【解決手段】本発明にかかる電源回路は、出力電圧VOUTAを分圧する第1のフィードバック回路と、出力電圧VOUTBを分圧する第2のフィードバック回路と、第1及び第2のフィードバック回路から出力される分圧電圧のいずれかを切替制御信号に基づいて選択し、出力する第1の選択回路と、第1の選択回路によって選択された分圧電圧と、基準電圧と、を比較し、比較結果に応じた電圧を出力するオペアンプ1と、オペアンプ1の出力電圧に応じた出力電圧VOUTAを生成するトランジスタMN1と、オペアンプ1の出力電圧に応じた出力電圧VOUTBを生成するトランジスタMN2と、切替制御信号に基づいて選択されたトランジスタMN1、MN2のいずれかのゲートに対し、オペアンプ1の出力電圧を出力する第2の選択回路と、を備える。

(もっと読む)

半導体回路装置

【課題】

半導体回路装置に内蔵された内部回路に供給する動作電圧について、内部回路に対する動作モードの変更に伴う動作電圧の安定期間を待つことなく、動作モード変更時でも動作開始時刻を速くすることが可能な構成を有する半導体回路装置を提供する。

【解決手段】

上記の課題を解決するため、外部電源から電圧供給を受ける電源線と、回路群と、回路群の動作電圧が異なる複数の動作モードに応じた制御信号を出力する制御回路と、回路群と、電源線とに電気的に接続し、回路群に前記電源線の電圧以下の電圧を供給する電源供給回路と、を備え、動作モードの変更後において、高い動作電圧を回路群が必要とする場合、電源供給回路は、高い動作電圧より高い電圧を回路群に供給した後、制御信号に応じて、変更後の動作モードに必要な動作電圧を供給する半導体回路装置を提供する。

(もっと読む)

安定化電源回路

【課題】簡単な構成で部品バラツキの影響を抑えて所定電圧を出力する高精度の安定化電源回路を提供すること。

【解決手段】電圧検知部11の出力電圧が電圧調整部12のリファレンス電圧より低い場合には電圧調整部12は出力電圧Voを上げ、の出力電圧が電圧調整部12のリファレンス電圧より高い場合には電圧調整部12は出力電圧Voを下げることで安定化電源回路の出力電圧が第1の所定電圧となるように安定化電源回路の出力電圧調整を行う。

(もっと読む)

電圧調整系

【課題】上流の電圧発生手段から引き出す電流の量を制限し、これにより回路の占有面積を減らす事ができる電圧調整系を提供する。

【解決手段】電圧を調整するための回路、系、および方法が含まれる。電圧調整系に関する或る実施形態には、出力を有する電圧調整手段430と、その電圧調整手段の出力と並列に接続された複数のステージ442と、が含まれる。各ステージには、ソースフォロワー回路450と、電圧調整手段の出力とそのソースフォロワー回路の入力とのあいだに直列に接続されたサンプルアンドホールド回路446と、が含まれる。

(もっと読む)

レギュレータ

【課題】レギュレータ回路の突入電流を抑制しチップを小型化すると共に、負荷回路の異常発生時の過大発熱を防止する。

【解決手段】基準電圧値Aと基準電圧値Bを出力する基準電圧発生回路5と、電流供給能力が異なる第1のトランジスタT1および第2のトランジスタT2と、抵抗素子R5と容量素子C2とからなる遅延回路8と、出力端子3と接地電位との間に接続された第1の電圧検出回路6および第2の電圧検出回路7と、第1のトランジスタT1および第2のトランジスタT2を動作させる動作電圧を出力する増幅器10と、第2のトランジスタT2へ供給するゲート電圧を切替えるスイッチ素子SWと、検出電圧Dと基準電圧Bとを比較する比較器11と、遅延回路8から検出される検出電圧Eと比較器11からの電圧信号COMPoとに基づいて、スイッチ素子SWを動作させる電圧信号2ANDoを出力する論理ゲート12と、でレギュレータ回路を構成する。

(もっと読む)

電源回路

【課題】 CPUコア部からI/F回路部へI/O初期設定(設定用レジスタを通常入力指定)が確実に実施され、ポートへの保護抵抗の介そうを不要とすることができる電源回路を提供すること。

【解決手段】 外部との入出力を行うI/F回路部22への電源供給を行う第1電源部11と、I/F回路部22を含む装置内各部の制御や演算を行うCPUコア部21への電源供給を行う第2電源部12を有する電源回路1において、第1電源部11を起動する動作の基準電圧を第2電源部12の出力する電源電圧にするVREF回路111、トランジスタTR2,TR3、抵抗R2を備えた。

(もっと読む)

ASICコアのためのマルチレギュレータ電力供給システム

電子製品と操作方法を開示する。電子製品は特定用途向け集積回路(ASIC)装置を含み、ASIC装置は、任意の外部キャパシタンスへ結合されるように構成された線形レギュレータモジュールと、電子製品の内部キャパシタンスへ結合されるように構成されたキャップレスレギュレータモジュールの両方を含む。ASIC装置の制御ロジックはレギュレータ選出信号に応答し、線形レギュレータモジュールとキャップレスレギュレータモジュールとのうち、ASIC装置の給電に用いるいずれか一方のモジュールを選出する。制御ロジックは、ある特定の動作期間中に線形レギュレータモジュールとキャップレスレギュレータモジュールとのうち、いずれか一方を選出できる。  (もっと読む)

(もっと読む)

電源回路

【課題】 CPUコア部とI/F回路部に供給する電源間で、CPUコア部の電源立上りが先になるように制御されることで、CPUコア部からI/F回路部へI/O初期設定(設定用レジスタを通常入力指定)が実施されるため、ポートへの保護抵抗の介そうを不要とすることができる電源回路を提供すること。

【解決手段】 第1電源部11の出力を放電して電源供給を開始させない放電回路131と、第2電源部12の電圧が所定閾値に達するまでは、放電回路131が放電を行う状態にし、第2電源部12の電圧が所定閾値を越えると、放電回路131が放電を停止し第1電源部11の電圧の立上げを許可するタイミング制御部13を備えた。

(もっと読む)

線形電圧調整器および線形電圧調整器を使用して電圧を調整するための方法

【課題】 線形電圧調整器を提供することにある。

【解決手段】 この線形電圧調整器は、電圧源から第1の電圧を受け取り、第1の周波数範囲内の第1の電圧の周波数成分を除去して、1次出力ノードで出力電圧を得るように構成された第1の回路を含む。この線形電圧調整器は、第1の回路の1次出力ノードに電気的に結合された第1および第2のインバータを有する第2の回路をさらに含む。第2の回路は、出力電圧を受け取り、第2の周波数範囲内の出力電圧の周波数成分を除去するように構成されている。第2の周波数範囲は第1の周波数範囲より大きい。

(もっと読む)

内部電圧発生回路

【課題】チャージポンプ動作により生成される昇圧電圧から必要な電圧レベルの内部電圧を、小占有面積かつ低消費電流で安定に生成することのできる内部電圧発生回路を実現する。

【解決手段】出力ノード(50)の出力電圧(Vcpr)と基準電圧(Vref)との比較結果に従って、出力ノード(50)を駆動するドライブトランジスタ(46)の駆動電流量を調整する。出力ノードに対しては、チャージポンプ回路の出力電圧線(38)から電流が供給される。チャージポンプ回路の出力電圧線(38)と差動増幅回路(44)の間および出力電圧線(38)と出力ノード(50)の間に、耐圧緩和回路(52,53)を設ける。また、ドライブトランジスタと出力ノードの間にも耐圧緩和回路(54)を設ける。

(もっと読む)

電源回路

【課題】少ないピン数で複数の基準電圧を得る。

【解決手段】第1基準電圧をオペアンプ10の正入力端に入力し、このオペアンプ10の出力によって出力トランジスタ14を駆動する。出力トランジスタ14の出力端に接続した第1出力ピン18から第1基準電圧を出力し、これを20および外付け抵抗22で第1外部基準電圧に変換する。第1外部基準電圧は第1入力ピンから入力され、オペアンプ10の負帰還される。出力トランジスタ14の出力端に抵抗50を介し定電流源52が接続され、この定電流源52と抵抗50の接続点がオペアンプ30の正入力端に接続される。オペアンプ30の出力により出力トランジスタ34が駆動され、出力トランジスタの出力を電圧変換した電圧が第2出力ピン32から出力され、これをオペアンプ30に負帰還する。第2出力ピンの出力により外付けトランジスタ40の駆動し、その出力を抵抗42で電圧変換して第2外部基準電圧とする。

(もっと読む)

電源装置

【課題】出力電圧のドロップを抑制し、所定の設定電圧を出力することが可能な電源装置を提供する。

【解決手段】電源装置100の制御回路4は、第1の活性化制御信号S1を出力して、第1の低飽和レギュレータ2の活性化を制御するようになっている。また、制御回路4は、第1の設定電圧制御信号S3を出力して、第1の低飽和レギュレータ2の出力電圧を予め設定された設定電圧よりも高くし、その後、もとの設定電圧に戻すよう制御するようになっている。

また、制御回路4は、第2の活性化制御信号S2を出力して、第2の低飽和レギュレータ3の活性化を制御するようになっている。また、制御回路4は、第2の設定電圧制御信号S4を出力して、第2の低飽和レギュレータ3の出力電圧を予め設定された設定電圧よりも高くし、その後、もとの設定電圧に戻すよう制御するようになっている。

(もっと読む)

電圧安定器を外付けせずとも電圧安定効果を具えるチャージポンプ回路

【課題】電圧安定器を外付けせずとも電圧安定効果を具えるチャージポンプ回路ノ提供。

【解決手段】主にインプット調節トランジスタをインプット電圧とチャージポンプ回路間に設置し、マイナスフィードバックメカニズムを利用し、該チャージポンプ回路のアウトプット電圧変化を検知する。これにより該チャージポンプ回路にインプットしようとする電圧を調節し、安定的に電圧をアウトプットする効果を達成する。またこうして、インプット電圧はアウトプット電圧を決定せず、このインプット調節回路により決定されるため、ロードに従いインプット電圧が変化することのないアウトプット電圧を獲得することができる。

(もっと読む)

複合型システム電源回路

【課題】外部から供給される直流電源電圧に基づいて複数種類の電源電圧を安定化して出力する複合型システム電源回路において、回路面積をあまり大きくすることなく、複合型システム電源回路全体としての突入電流を低減する。

【解決手段】この複合型システム電源回路は、外部から供給される直流電源電圧と基準電圧とに基づいて第1の電源電圧を生成すると共に、第1の電源電圧に基づいて第1のイネーブル信号を生成する第1のレギュレータと、第1の電源電圧を平滑すると共に、第1のイネーブル信号の活性化を遅延させる第1のコンデンサと、第1のイネーブル信号が活性化されることによって動作を開始し、外部から供給される直流電源電圧と基準電圧とに基づいて第2の電源電圧を生成する第2のレギュレータと、第2の電源電圧を平滑する第2のコンデンサとを具備する。

(もっと読む)

外部負荷インタフェース回路、電子制御装置、および外部負荷インタフェース回路における駆動電圧切替方法

【課題】移動体内のマイクロコンピュータから入力される制御コマンドに従ってホール効果素子センサ等の外部負荷を駆動するための駆動電圧を供給する外部負荷インタフェース、電子制御装置、および外部負荷インタフェースにおける駆動電圧切替方法に関し、ASICの占有面積や製造コストを増大させずに、ECUの外部に設けられた複数種の外部負荷に対応することを目的とする。

【解決手段】外部負荷SE1〜SE3の種類に応じて複数の駆動電圧を切り替えるように構成され、外部負荷インタフェース回路の内部で生成される基準電圧と、外部端子に印加される任意の外部電圧との間で切り替えを行うことによって、それぞれ対応する駆動電圧を出力するようになっている。

(もっと読む)

レギュレータ回路及び集積回路装置

【課題】負荷回路への効率的な電流供給を実現できるレギュレータ回路の提供。

【解決手段】レギュレータ回路は、電圧生成回路51a〜51nと、入力端子IT1に電圧生成回路51a〜51nの内の1つによって生成された基準電圧VREFが入力され、入力端子IT2に調整電圧VRGが入力され、基準電圧VREFと調整電圧VRGの電圧差を増幅する差動増幅回路30と、差動増幅回路30の出力端子DQが接続され、調整電圧VRGを出力する出力回路40を含む。出力回路40は、レギュレータ回路の出力端子RQと電源VSSとの間に設けられ、そのゲートに差動増幅回路30の出力端子DQが接続されるN型出力トランジスタTQ1と、電源HVDDとレギュレータ回路の出力端子RQとの間に設けられ、そのゲートに差動増幅回路30の出力端子DQが接続されるP型出力トランジスタTQ2を含む

(もっと読む)

半導体装置及び半導体装置の動作制御方法

【課題】 電源を供給する回路では消費電流が増加してしまう場合があった。

【解決手段】 半導体装置は、外部電源電圧から第1の所定電圧を生成し、内部回路が通常動作の場合には活性化され、前記内部回路が待機動作の場合には非活性化される第1のレギュレータと、前記外部電源電圧から第2の所定電圧を生成する第2のレギュレータと、動作状態に基づいて前記第1の所定電圧あるいは前記第2の所定電圧に基づいて動作する前記内部回路とを有する。

(もっと読む)

1 - 20 / 31

[ Back to top ]