Fターム[5H730BB02]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 充放電型(直並列切換) (1,313) | 昇圧型 (836)

Fターム[5H730BB02]に分類される特許

821 - 836 / 836

半導体回路装置

【課題】

チャージ・ポンプ回路の電流能力のばらつきを低減する。

【解決手段】

チャージ・ポンプ回路110の押し上げ容量素子C1と発振回路123の容量素子の容量膜(酸化絶縁膜)が実質的に同一となるように、チャージ・ポンプ回路110の押し上げ容量素子C1と発振回路123の容量素子が形成される。さらに好ましくは、容量素子C1と容量素子C2は、同一プロセスにおいて同時に形成される。各容量素子の容量膜をこのように形成することによって、容量素子C1と容量素子C2の容量膜のばらつきに起因する容量比のばらつきを大きく低減し、チャージ・ポンプ回路110の電流能力Icpのばらつきを低減することができる。

(もっと読む)

チャージポンプ回路及びこれを備えた電子回路並びにチャージポンプ回路の駆動方法

チャージポンプ回路の動作を停止する際において、接続された負荷における不具合の発生を確実に回避することが本発明の目的である。チャージポンプ回路は、電源に接続される第1のスイッチング素子S1、負荷102に接続される第2のスイッチング素子S2及び第1のスイッチング素子S1と第2のスイッチング素子S2との間に接続されるコンデンサ素子Cpを備え、通常動作時に第1のスイッチング素子S1、第2のスイッチング素子S2及びコンデンサ素子Cpに印加されるクロック信号のいずれかの位相を反転することで通常動作時における電荷の移動方向と逆方向に電荷を移動させる。  (もっと読む)

(もっと読む)

レギュレータ回路及びその使用法

本発明は、レギュレータ回路及びその使用法に関するものである。このレギュレータ回路は、少なくとも2つの入力端子、少なくとも2つのリアクタンスを有する1つまたはいくつかのリアクタンス群、少なくとも2つの出力端子、前記リアクタンスを互いに接続するのに適し、かつ前記リアクタンスの少なくとも1つを前記入力及び出力端子に接続するのに適した複数の相互接続を具えている。これらの相互接続は、前記リアクタンスの直列接続を並列接続に切り換えることを可能にするミニチュアリレーで構成される。前記回路は追加的に、電圧監視手段、電源モジュール、入力及び出力保護手段、基準信号モジュール、制御モジュール、等を具えることができる。前記レギュレータ回路は多数の用途、例えばチャージポンプ、電源、DC/DCコンバータ、AC/DCコンバータ、D/A変換器、A/D変換器、電力増幅器、等を有する。  (もっと読む)

(もっと読む)

開回路電圧調整を備える電子バラスト

開回路電圧調整を有する電子バラストは、該電子バラストの出力へ動作可能な状態で接続され、検知出力電圧信号を発生させるフィラメント電流検知回路224と、前記検知出力電圧信号を受信し、当該電子バラストの出力での電圧を制御するよう動作可能な状態で接続された調整パルス幅変調器U3とを有する。調整パルス幅変調器U3は、出力電圧閾値限界を有する。調整パルス幅変調器U3は、検知出力電圧信号が出力電圧閾値限界を超える場合に、電子バラストの出力での電圧を制限する。調整パルス幅変調器U3は、高電圧ドライバ及び共振ハーフブリッジへのパルス幅を制限することによって、出力電圧を制限することができる。フィラメント電流検知回路224は、例えばタンク電流を検知することによって、間接的に出力電圧を検知することができ、あるいは、出力電圧を直接的に検知することもできる。  (もっと読む)

(もっと読む)

DC/DCコンバータを区分化スイッチングで調整するためのデジタル・ループ

区分化されたスイッチ、フライイング・キャパシタ、出力電圧端子、フィードバック・ループ、及び、デジタル電圧調整器ブロックを含むスイッチ・アレイ、を含む電力制御回路が提供される。デジタル電圧調整器ブロックは、A/Dコンバータ、エンコーダ、加減算器、及び、ゲート・ロジックを含む。これらの電力制御回路は、パス・トランジスタを含まない。電力制御回路の荷電ポンプが、荷電フェーズ、及び、ポンピング・フェーズを含む2フェーズ周期で作動する方法もまた提供される。電力制御回路は、これらのフェーズの双方で制御され、それによって、出力電圧のリップルを削減する。  (もっと読む)

(もっと読む)

電圧ポンプを有するマイクロホン

第2マイクロホン部材に関連して可動な第1マイクロホン部材によって発生された入力信号を受け取るために結合された前置増幅器(108)と、どちらのマイクロホン部材にもバイアス電圧を供給する電圧ポンプ(104)とを備えた、マイクロホン出力信号を供給するように構成された集積回路(102)。

(もっと読む)

(もっと読む)

電流調節充電ポンプドライバにキャパシタ比例電流を与える集積デバイス

集積回路(10)は、外部電流検出抵抗を必要とすることなく、バッテリ(18)から負荷へ流れる電流を調節する。そのICは、主充電ポンプ(12)、モデル充電ポンプ(14)、電流検出回路(U3,M2)、モデル充電ポンプの出力部での電圧レベルを主充電ポンプの出力部での電圧に等しくさせる第1の制御回路と、および、モデル充電ポンプによるモデル電流出力を、バッテリ電源の電圧変化に拘わらず、外部フライイングキャパシタ(Cp)のキャパシタンス値により確立されたレベルに調節させるための第2の制御回路とを備える。 (もっと読む)

全体的フィードフォワードスイッチング電源制御

【課題】

【解決手段】開示された電源は、制御信号によって制御可能でありDC入力電圧から所望の出力を供給するスイッチング式変換器と、スイッチング式変換器のスイッチのゲート駆動電圧,温度測定値などをアナログ入力として受信し、アナログ入力をデジタル入力信号に変換するアナログデジタル変換器と、デジタル入力信号を受信して、スイッチを駆動する制御信号を生成するデジタルプロセッサと、デジタル入力信号をスイッチング式変換器の所望の出力に関連付けるデータを記憶して、制御信号の生成に用いるメモリ出力信号をデジタルプロセッサに提供するメモリとを備える。

(もっと読む)

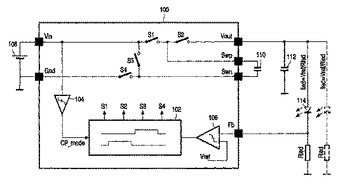

ブーストコンバータ

本発明は、容量性モード及び誘導性モードの両方において動作することができるブーストコンバータ(100)に関する。容量性モードにおいて、コンバータは、スイッチの集合(S1、S2、S3及びS4)とコンデンサの集合(110、112)とを利用して、チャージポンプ回路として動作する。誘導性モードにおいて、コンバータは、昇圧回路として動作し、スイッチの部分集合(S2及びS4)とインダクタとを用いる。モードは、容量性モードにおいて、バッテリ(108)をブーストコンバータ(100)へ結合するのにも使用される選択端子(Vin)を用いて選択される。  (もっと読む)

(もっと読む)

多数のスイッチング電圧レベルをスイッチングするためのコンバータ回路

多数のスイッチング電圧レベルをスイッチングするためのコンバータ回路が規定される。このコンバータ回路は、各相(R,Y,B)のためのn個の第一スイッチング・グループ(1.1, ..., 1.n)を有している。ここで、第n番目の第一スイッチング・グループ(1.n)は、第一電力半導体スイッチ(2)及び第二電力半導体スイッチ(3)により構成され、第一番目の第一スイッチング・グループ(1.1)から第(n−1)番目の(第一)スイッチング・グループ(1.(n-1))までは、それぞれ、第一電力半導体スイッチ(2)及び第二電力半導体スイッチ(3)、並びに第一及び第二電力半導体スイッチ(2,3)に接続されたキャパシタ(4)により構成されている。n個の第一スイッチング・グループ(1.1, ..., 1.n)のそれぞれは、それぞれ隣接する 第一スイッチング・グループ(1.1, ..., 1.n)に直列に接続され、第一番目の第一スイッチング・グループ(1.1)の中の第一及び第二電力半導体スイッチ(2,3)は、互いに接続されている。前記コンバータ回路に蓄えられる電気的エネルギーの量を少なくするため、n≧1 であり、且つ、p個の第二スイッチング・グループ(5.1, ..., 5.p)及びp個の第三スイッチング・グループ(6.1, ..., 6.p)が設けられ、それらは、それぞれ、第一電力半導体スイッチ(2)及び第二電力半導体スイッチ(3)、並びに第一及び第二電力半導体スイッチ(2,3)に接続されたキャパシタ(4)により構成されている。ここで、p≧1 であり、且つ、p個の第二スイッチング・グループ(5.1, ..., 5.p)のそれぞれは、それぞれ隣接する第二スイッチング・グループ(5.1, ..., 5.p)に対して直列に接続され、p個の第三スイッチング・グループ(6.1, ..., 6.p)のそれぞれは、それぞれ隣接する第三スイッチング・グループ(6.1, ..., 6.p)に対して直列に接続されている。第一番目の第二スイッチング・グループ(5.1)は、第n番目の第一スイッチング・グループ(1.n)の中の第一電力半導体スイッチ(2)に接続され、第一番目の第三スイッチング・グループ(6.1)は、第n番目の第一スイッチング・グループ(1.n)の中の第二電力半導体スイッチ(3)に接続されている。更に、第p番目の第二スイッチング・グループ(5.p)の中のキャパシタ(4)は、第p番目の第三スイッチング・グループ(6.p)の中のキャパシタ(4)に対して直列に接続されている。 (もっと読む)

コモンモード制御を備えた差動チャージポンプ

入力信号によってフィルタを充電及び放電するための出力電流を供給するチャージポンプであって、前記チャージポンプは、第1の電流源であって、該電流源を駆動するための前記入力信号と接続可能であり、定電流I0に可変電流Δxを加えたものに等しい第1の電流を供給するように構成された第1の電流源を有し、前記可変電流Δxは前記入力信号に正比例し、前記チャージポンプは更に、第2の電流源であって、該電流源を駆動するための前記入力信号に接続可能であり、定電流I0から可変電流Δxを減じたものに等しい第2の電流を供給するように構成された第2の電流源と、前記出力電流を供給する出力部と、を有し、前記出力部は、前記出力電流が前記第1の電流と前記第2の電流との差に等しくなるように、前記第1及び第2の電流源の両方に接続されたチャージポンプ。  (もっと読む)

(もっと読む)

面積効率の高い電荷ポンプ

第1の電荷ポンプが電圧加算器段を複数備える。第1の電圧加算器段は、入力電圧信号VCCを受け取り、クロック信号に応答して2* VCCとVCCとの間を交番する第1の電圧信号を出力する。N番目の電圧加算器段は先行段から入力電圧信号VCCと第1の電圧信号を受け取り、N* VCCとVCCとの間で交番する第2の電圧信号を出力する。個々の加算器段内に設けられるコンデンサはVCCの最大使用電圧を維持するように要求される。別の実施形態では、第1の電荷ポンプを1以上の倍電圧器段と組み合わせて、さらに高い出力電圧の発生を図るようにしてもよい。  (もっと読む)

(もっと読む)

低電力チャージポンプ

低電力チャージポンプ(300)が開示される。第1のポンプステージのポンプ駆動ノード(270)が、次のポンプステージのポンプ駆動ノード(271)に選択的に結合される。第1のポンプステージから次のステージへの電荷の移動後、第1(270)および次(271)のポンプ駆動ノードが結合される。それによって、第1のステージポンプ駆動ノード(270)に残留する電荷が、次のポンプ駆動ノード(271)に移動する。第1のポンプ駆動ノード(270)から第2のポンプ駆動ノード(271)への電荷の移動後、ノードは切り離される。第1のポンプステージを次のポンプステージのポンプ駆動ノード(271)へ選択的に結合することによって、第1のポンプ駆動ノード(270)は、次のポンプ駆動ノード(271)を予備充電することができ、駆動クロックを正の向きに遷移させるために、クロック駆動回路(700)が与えられなければならないエネルギーを低減する。第1のステージから予備充電エネルギーが引き出され、負の向きのクロック信号の遷移中にクロック駆動回路によってこれまで消失していたエネルギーを低減するので有利である。この新規の方法で、チャージポンプデバイスの効率が有益に高められ、低電力性能が高められる。  (もっと読む)

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

チャージポンプ回路

【課題】高効率で大出力電流のチャージポンプ回路を提供する。

【解決手段】前段2つの電荷転送用MOSトランジスタM1、M2をNチャネル型で構成し、後段2つの電荷転送用MOSトランジスタM3、M4をPチャネル型で構成する。また、中間電位の出力を可能にした反転レベルシフト回路S1とS2、非反転レベルシフト回路S3とS4を設けた。これらの構成により、高効率で大出力電流のチャージポンプ回路を実現できると共に電荷転送用トランジスタM1〜M4のゲート・ソース間電圧Vgs(トランジスタがオン状態の時)を2Vddに揃えることができる。

(もっと読む)

半導体集積回路装置

【課題】 電源電圧が低下しても安定してワード線電位に用いられる昇圧電圧を供給する。

【解決手段】 第2昇圧回路16は、第1昇圧回路15が生成するワード線電位となる昇圧電源VPPよりも高いレベルの昇圧電圧VPP+αを生成し、静電容量素子17に電荷が蓄積される。電源電圧VCCの低下によって昇圧電圧VPPがしきい値よりも低くとなると、制御信号出力部18から制御信号Cがスイッチング部19に出力され、静電容量素子17に蓄積されていた電荷が電源電圧VPPとして補給される。電源電圧VPPがしきい値よりも高くなると制御信号Cが停止され、スイッチング部19がOFFとなる。昇圧電圧補償制御部SHCがこれらの制御を繰り返すことにより、電源電圧VCCが変動しても昇圧電圧VPPを安定して供給することができる。

(もっと読む)

821 - 836 / 836

[ Back to top ]