Fターム[5H740JA01]の内容

Fターム[5H740JA01]に分類される特許

121 - 140 / 617

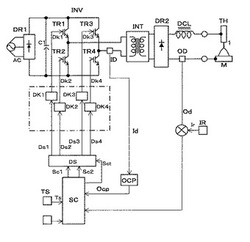

アーク加工用電源装置

【課題】 電源装置のインバータ回路を駆動するスイッチング素子駆動回路の逆バイアス電圧が低くなると、ターン・オフ損失が増加しスイッチング素子の劣化に繋がる。

【解決手段】 直流変換回路と、直流電圧を高周波交流電圧に変換するフルブリッジのインバータ回路と、インバータ回路を制御すると共に変圧器の入力電流が基準電流以上になると所定時間インバータ回路を停止する出力制御回路と、出力制御信号に応じてスイッチング素子を駆動すると共に逆バイアスコンデンサに電流を供給するスイッチング素子駆動回路とを備え、インバータ回路が停止しているとき、第1のスイッチング素子及び第4のスイッチング素子が0から1/2周期の間で重ならないようにオンし、第2のスイッチング素及び第3のスイッチング素子が1/2から1周期の間で重ならないようにオンするスイッチング制御回路、を備えたことを特徴とするアーク加工用電源装置である。

(もっと読む)

負荷駆動装置の製造方法

【課題】負荷駆動装置において負荷を駆動するためのスルーレートが狙い値となるように負荷駆動装置を製造する。

【解決手段】まず、半導体基板に第1基準電源32、スイッチング素子34、電流生成部35、およびオペアンプ33を備えた駆動回路30を形成する。この場合、第1基準電源32の第1基準電圧を調整することにより、負荷10に流す定電流の大きさを調整する。続いて、電流生成部35で生成されるテール電流が大きくなるようにテール電流のトリミングを行うことでオペアンプ33のスルーレートを調整する。これにより、オペアンプ33がスイッチング素子34を駆動したときに負荷10に流れる定電流が一定値に達するまでの定電流の立ち上がりの傾きを狙い値に調整することができる。

(もっと読む)

負荷駆動装置

【課題】負荷を駆動するための定電流のばらつきを低減することができる負荷駆動装置を提供する。

【解決手段】シャント抵抗20の一端側をオペアンプ34の反転入力端子に接続し、シャント抵抗20の他端側を基準電源32を介してオペアンプ34の非反転入力端子に接続する。シャント抵抗20に流れる電流は、駆動回路30内の第1スイッチング素子35を介して負荷10であるIGBTのゲートに流れるようになっている。これにより、基準電源32の基準電圧の値をVrefとし、シャント抵抗20の抵抗値をRoutとし、負荷10に流れる定電流の値をIcとすると、Vref=Rout×Icとなるようにオペアンプ34が第1スイッチング素子35のゲートをフィードバック制御する。これにより、シャント抵抗20に流れる電流の大きさが一定に制御され、ひいては負荷10に流す定電流のばらつきが低減される。

(もっと読む)

情報処理装置、これを用いたモータ駆動装置、及び、情報処理方法

【課題】 上下アームのスイッチング素子を駆動するとともに、上下アームの異常を検出して異常信号を出力するゲート駆動回路を備える情報処理装置において、異常信号の通知機能が正常であるか否かを判定する。

【解決手段】 情報処理装置(ECU)において、ブートストラップ式のゲート駆動回路は、ゲート駆動の開始前に、通常駆動時ならば先に下アーム駆動信号を出力すべきところ先に上アーム駆動信号D1を出力し(S10)、ダミー異常信号Edを意図的に発生させる(S20)。ここで異常信号通知機能が正常であれば、ダミー異常信号Edは、異常信号出力部から出力され、異常信号線を経由して伝達され、異常信号受信部に受信される。そこで、異常信号受信部がダミー異常信号Edを受信したか否かを確認することで、異常信号通知機能が正常であるか否かを判定する(S30)ことができる。

(もっと読む)

電力変換装置

【課題】2段フィルタの減衰特性悪化を防止することにより、小型なフィルタでノイズ規格をクリアできるようにする。

【解決手段】コモンチョークコイルL1,L2にアース電位相当の冷却フィン3を近接させる構成とすることにより、コモンチョークコイルL1,L2とアースとの静電結合を大きくし、コモンチョークコイルL1とL2間の静電結合を小さくし得るようにする。これにより、2段以上のフィルタの減衰特性悪化を防止できるようにし、小型なフィルタでノイズ規格をクリアできるようにする。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

ドライバ回路

【課題】 絶縁電源を別に設けることなくハイサイド側の回路に負のゲート電圧を供給することが可能なゲートドライバ回路を実現する。

【解決手段】

第1トランジスタ21と第2トランジスタが直列に接続されたハーフブリッジ回路において、ハイサイド側の第1トランジスタ21に負のゲート電圧を第1の制御回路11を介して供給するためのコンデンサ13、及び、ローサイド側の第2トランジスタ22に負のゲート電圧を第2の制御回路12を介して供給するための制御回路電源14を備え、コンデンサ13の一端をスイッチ素子30を介して制御回路電源14の−端子側の負電圧VEEと接続し、他端を出力端子4の電圧と接続するように構成したドライバ回路1であって、スイッチ素子30は、第2トランジスタ22がオン状態となるタイミングでオンされるように制御される。

(もっと読む)

電力変換回路の駆動装置

【課題】フェール信号を出力するフェール用フォトカプラPCfの2次側を直列接続する場合、その配線長が長くなることから、フェール信号のノイズに対する耐性が低下するおそれがあること。

【解決手段】インバータIV1、コンバータCVおよびインバータIV2を構成する上側アームのスイッチング素子と下側アームのスイッチング素子とは、基板30に対して2列に配置され、その制御端子(ケルビンエミッタ電極KE、センス端子ST、ゲートG)が基板30に差し込まれている。これら2列の間には、フェール用フォトカプラPCfが配置されている。インバータIV1に対応するフェール用フォトカプラPCfは、隣接するもの同士で直列接続され、各列の端部が接続されることでU字型の配線構造を有し、その端部がマイコン20に接続されている。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子のオン故障や誤動作によって発生する、スイッチング素子をオフできない異常状態を検出することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aとオフ駆動用FET122aに電流が流れており、かつ、流れている電流の差が所定値以下であるとき、IGBT110dが異常状態にあると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aのオン故障や誤動作によって発生する、IGBT110dをオフできない異常状態を検出することができ、IGBT110aの熱破壊を防止することができる。

(もっと読む)

フィルタ回路およびそれを用いた照明装置

【課題】コンバータで発生するスイッチングノイズが伝導および輻射するのを抑制可能なフィルタ回路およびそれを用いた照明装置を提供する。

【解決手段】コンバータ44とコンバータ44の入力側の電源あるいは出力側の負荷42との間に設けられるフィルタ回路43であって、高電位側のラインに第1のインダクタL9が設けられるとともに、低電位側のラインに第2のインダクタL10が設けられ、第1のインダクタL9と第2のインダクタL10とのインダクタンス値がそれぞれ異なる。

(もっと読む)

駆動回路及びこれを備える半導体装置

【課題】簡易な構成でスイッチング素子の負バイアス駆動を行う駆動回路及び当該駆動回路を備えた半導体装置の提供を目的とする。

【解決手段】本発明の駆動回路は、ICチップに搭載され、半導体スイッチング素子4aを駆動する駆動回路であって、前記ICチップ外部の単一電源から供給される第1の電圧V1を受け、第1の電圧V1から第2の電圧V2を生成して、これを半導体スイッチング素子4aの基準端子に印加する電源回路8と、前記ICチップ外部からの入力信号に応じて、半導体スイッチング素子4aの制御端子に第1の電圧V1を印加/非印加することにより半導体スイッチング素子4aを駆動する駆動部とを備える。

(もっと読む)

センス機能付きパワー半導体デバイス

【課題】センス機能付きパワー半導体デバイスのメイン領域とセンス領域の電流スイッチタイミングや過渡特性のずれを小さくするようゲート駆動回路で補正して電流検出の精度を向上させるセンス機能付きパワー半導体デバイスを提供する。

【解決手段】ゲートパルス発生回路(21)から出力されるゲート駆動信号が、ゲート抵抗値補正回路1(22)及びゲート抵抗値補正回路2(23)の各補正抵抗を経由してセンスゲート端子Gs 及びメインゲート端子Gm 並びにMPU(24)の入力端へ出力される。各ゲート抵抗値補正回路(22,23)の補正抵抗値は、駆動時の負荷電流値、各ゲート電圧値以外に、電源電圧値および素子温度値のうちいずれかの条件を測定し、測定した条件に応じてMPU(24)で最適な補正抵抗値を計算、または内蔵するメモリから最適な補正抵抗値を呼び出し、各ゲート抵抗値を補正する。

(もっと読む)

半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、バイパスコンデンサの充放電電流を上アーム側スイッチング素子駆動回路と下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

(もっと読む)

スイッチング素子の駆動回路

【課題】誤動作を防止することによって従来よりも信頼性を高めた、スイッチング素子の駆動回路を提供する。

【解決手段】スイッチング素子Q5の駆動回路HVICにおいて、論理回路U15は、内部状態に応じて高電位側のスイッチング素子Q5をオン/オフに切替えるための制御信号を出力する。第1の抵抗部RP1は、第3の電源ノードVBと第1のノードND1との間に設けられる。第2の抵抗部R2は、第1のノードND1と第2のノードND2との間に設けられる。第1の制御用スイッチング素子Q1は、第2のノードND2と第1の電源ノードGNDとの間に設けられ、第1のパルス信号PLS1を受けたときに導通する。第1の比較部U4は、第1のノードND1の電位が第1の閾値以下の場合に活性状態となる第1の信号Sonを出力する。第1および第2の抵抗部RP1,R2の少なくとも一方の抵抗値は、上記の制御信号の変化に基づいたタイミングで変化する。

(もっと読む)

電子装置

【課題】スイッチング素子をオフするように制御しているにもかかわらず、オフできない異常状態を検出することができる電子装置を提供する。

【解決手段】IGBT110dに流れる電流が電流閾値より大きくなると、電流検出回路125は、IGBT110dに電流が流れていると判断する。制御回路128は、駆動信号がIGBT110dのオフを指示しているにもかかわらず、電流検出回路125がIGBT110dに電流が流れていると判断すると、IGBT110dをオフできない異常状態にあると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、駆動信号がIGBT110dのオフを指示しているにもかかわらず、IGBT110dをオフできない異常状態を検出することができ、IGBT110dの熱破壊を防止できる。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障等した場合であっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】オン駆動用抵抗121bとオフ駆動用抵抗122bの抵抗値は、オン駆動用FET121aとオフ駆動用FET122aがともにオンした場合に、IGBT110dのゲート電圧が、オン電圧が増加するオン、オフの閾値電圧付近の所定範囲外であって、オン、オフの閾値電圧より低くなるように設定されている。そのため、オン駆動用FET121aがオン故障等したときにオフ駆動用FET122aがオンしても、オン電圧が増加してIGBT110dの発熱が増大することなく、IGBT110dをオフすることができる。従って、IGBT110dの熱破壊を防止することができる。

(もっと読む)

レベルシフト回路及びそれを用いたスイッチングレギュレータ

【課題】電源電圧を高くしてもトランジスタのゲート耐圧を上げる必要がなく、低電源電圧から高電源電圧まで広範囲に使用できるレベルシフト回路を提供する。

【解決手段】レベルシフトトランジスタ105は、入力トランジスタ101と負荷トランジスタ103との間に、レベルシフトトランジスタ106は、入力トランジスタ102と負荷トランジスタ104との間にそれぞれ接続される。レベルシフトトランジスタ105,106の各ゲートGは共通接続され、その共通接続点にはレベルシフト電圧生成回路120で生成されたレベルシフト電圧Vscが電圧源V1の大きさに応動して印加される。負荷トランジスタ103,104のソース−ゲート間に印加される電圧VSGは、レベルシフト電圧Vscによって、電圧源V1が増減してもほぼ一定になるように設定される。これにより、負荷トランジスタ103,104を低耐圧のトランジスタで構成することができる。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aのゲート電圧がオンしない電圧であるにもかかわらず、ドレイン−ソース間電圧がオンした際の電圧であるとき、オン駆動用FET121aがオン故障していると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aがオン故障してIGBT110dをオフできない異常状態になっても、IGBT110dの熱破壊を防止できる。

(もっと読む)

インバータ駆動装置

【課題】インバータのゲート駆動にソフトターンオフ(Soft Turn Off)を設けてIGBTを安定して保護できるようにしたインバータ駆動装置を提供する。

【解決手段】本発明のインバータ駆動装置は、IGBTのターンオンまたはターンオフを制御し、IGBTで短絡または過電流が検出されればIGBTを強制的にターンオフさせるゲート駆動部と、前記ゲート駆動部から出力されるIGBTのターンオンまたはターンオフ制御電流を増幅させる電流バッファと、前記ゲート駆動部から出力されるIGBTの強制ターンオフ制御電流を遅延させてIGBTのソフトターンオフ時間を長く維持させるフィルタと、を含んで構成される。

(もっと読む)

双方向スイッチおよびそれを用いたスイッチ回路

【課題】高耐圧の双方向スイッチを小型化する技術を提供する。

【解決手段】MOSFETを用いた双方向スイッチにおいて、MOSFETのソース端子とバックゲート端子間を、トランスファゲートTGを介して接続する。MOSFETのバッグゲート端子とトランスファゲートTG間の接続点と、グラウンド電位(上記MOSFETがnチャネルの場合)または電源電位(上記MOSFETがpチャネルの場合)との間にスイッチを用いてもよい。

(もっと読む)

121 - 140 / 617

[ Back to top ]