Fターム[5H740JA01]の内容

Fターム[5H740JA01]に分類される特許

41 - 60 / 617

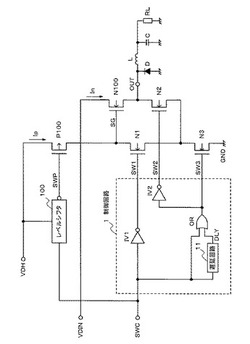

出力回路

【課題】貫通電流の発生を防止することのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力用NMOSトランジスタN100のドレイン端子に入力電圧VDINが印加され、ソース端子OUTにLC回路およびダイオードDが接続される。この出力回路は、NMOSトランジスタN1およびN2が、出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に直列に接続され、NMOSトランジスタN3が、NMOSトランジスタN1とNMOSトランジスタN2の接続点と接地電位端子GNDとの間に接続され、制御回路1が、出力用NMOSトランジスタN100が非導通のときに出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に短絡経路が形成されるようNMOSトランジスタN1〜N3の導通を制御する。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体かなるスイッチング素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続されたコンデンサC1と抵抗R1とからなる並列回路と、並列回路にコンデンサC2とスイッチング素子Q2と抵抗R2からなる直列回路がさらに並列接続され、コンデンサC2とスイッチング素子Q2との接続点にダイオードD1のアノードが接続され、ダイオードD1のカソードとスイッチング素子Q2のゲートはスイッチング素子Q1のソースに接続され、制御信号のオフ信号に対してスイッチング素子Q1ゲートを負電位にバイアスする。

(もっと読む)

電力変換装置

【課題】両極性ブートストラップ回路のキャパシタ充電を短絡電流が流れることがなく安全かつ確実に実施できる電力変換装置を提供する。

【解決手段】各レグ2〜4を構成する上下の各アームのスイッチング素子SuH、SuL、・・・に対しオン/オフ駆動用の正負両極の電圧を印加するアーム駆動回路DRuH、DRuL、・・・を個別に設け、直流電源Vg1〜Vg3からの電力により正負の各電圧を充電する各キャパシタC1u、C2u、・・・を上下の各アームに設け、かつ各レグ2〜4に両極性ブートストラップ回路5〜7を配置し、キャパシタ充電制御を行う制御回路8は、多相交流電源1の各相の電圧の中で最も高い電圧が入力されているレグの上段アーム側のスイッチング素子と、最も低い電圧が入力されているレグの下段アーム側のスイッチング素子のみをオンする制御信号を各相の電圧変化に応じて繰り返し出力する。

(もっと読む)

バスバを含む接続配線及び電力変換器

【課題】バスバを含む接続配線において、比較的簡単な構造で、バスバに電流が流れるときのインダクタンスを効果的に抑制することである。

【解決手段】電力変換器10においてバスバを含む接続配線30は、平滑用コンデンサモジュール12とパワーモジュール14の間を接続する正極側バスバ32と、正極側バスバ32と対をなして平滑用コンデンサモジュール12とパワーモジュール14の間を接続する負極側バスバ34と、絶縁物40を介して正極側バスバ32の外周全体を被覆する正極側導体42と、絶縁物44を介して負極側バスバ34の外周全体を被覆する負極側導体46と、正極側導体42と負極側導体46とを相互に電気的に接続する接続導体50,52を備える。

(もっと読む)

ゲートドライブ回路

【課題】オンデューティが50%以上のパルス信号でもスイッチング素子のゲートをドライブできる安価なゲートドライブ回路。

【解決手段】直流電源Vcc1の両端にトーテムポール接続され且つ各ベースにパルス信号が入力されるトランジスタQ2,Q3と、直流電源Vcc2の両端にトーテムポール接続され且つ各エミッタがスイッチング素子Q1のゲートに接続されるトランジスタQ4,Q5と、一次巻線P1がトランジスタQ2,Q3の各エミッタとトランジスタQ2,Q3の一方のコレクタとにコンデンサC1を介して接続され、二次巻線S1がトランジスタQ4,Q5の各ベースとトランジスタQ4,Q5の各エミッタとに接続されたトランスT1とを有し、パルス信号Vinの最大オンデューティは、トランスT1の一次巻線電圧VpとトランジスタQ4,Q5のベース−エミッタ間順方向電圧とに基づいて決定される。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

インバータ装置およびそれを用いた誘導加熱装置

【課題】スイッチング素子の耐数年数をのばすと共に、駆動電圧を低下させることによるスイッチング素子の損失増加も改善させるインバータ装置およびそれを用いた誘導加熱装置を提供することを目的とする。

【解決手段】交流電圧を直流電圧に変換するコンバータ回路30と、スイッチング素子24で構成され直流電圧を任意の電圧と周波数の電力に変換し、負荷に高周波電流を供給するインバータ回路31と、インバータ回路31のスイッチング素子24にスイッチング信号を供給する駆動回路25と、インバータ回路31の出力電力を検知する電力検知手段26とを備え、電力検知手段26で検知した電力に応じて、インバータ回路31のスイッチング素子24に供給するスイッチング信号の駆動電圧を可変させる駆動電圧可変手段27とを備えた構成とすることで、インバータの出力電力に応じて、スイッチング素子24の駆動電圧を可変させることが可能となる。

(もっと読む)

電力変換装置

【課題】電力変換装置を構成するFETの発熱を低下させ、最大出力電力を高めた改良された電力変換装置を得る。

【解決手段】FET1a、FET1bとFET1a、FET1bに逆並列接続された還流ダイオードD1a、D1bとにより半導体スイッチS1a、S1bを構成し、スイッチング動作を行う2個1組の半導体スイッチS1a、S1bと、平滑コンデンサC1とを有し、半導体スイッチS1a、S1bのFET1a、FET1bの相補的スイッチング動作により電力変換を行う電力変換装置10において、半導体スイッチS1a、S1bに流れる電流の向きを検出する電流センサCS1と、半導体スイッチS1a、S1bに流れる電流の向きが負であるときに、半導体スイッチS1a、S1bのPWMゲート信号のオン信号を間引くゲート生成部11を備えた。

(もっと読む)

ゲートドライブ回路

【課題】ワイドバンドギャップ半導体からなるスイッチング素子の回生動作時の電力損失を抑制し、かつ、安定してターンオン/オフさせることができるゲートドライブ回路。

【解決手段】制御回路とスイッチング素子Q1のゲートとの間に接続され、コンデンサC1と抵抗R1とダイオードD1からなる直列回路と、スイッチング素子のゲートとソースとの間にPNP型トランジスタQ2が抵抗R2を介して接続され、トランジスタQ2のコレクタ・ベース間にダイオードD2が接続され、さらにトランジスタQ2のベースはダイオードD1のアノードに接続され、制御回路からのオフ信号が入力されると、トランジスタの接合電圧とダイオードD2との順方向電圧との差分電圧を残してゲートとソースとの間を短絡する。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

ドライブ回路

【課題】ベース電流による電力損失を低減するドライブ回路を提供する。

【解決手段】BJT21のベース端子にベース電流を供給するドライブ回路1は、BJT21のベース電流を生成するベース回路部30と、制御端子に供給される制御電圧に基づき、ベース電流を生成するための駆動電圧をベース回路部30に供給するドライブ部10と、BJT21のベース端子とBJT21のエミッタ端子との間に発生する第1のベース−エミッタ間電圧Vbeを検出し、検出した第1のベース−エミッタ間電圧Vbeに応じたベース電流をBJT21に供給するように制御電圧を制御して、ドライブ部10に供給するベース電流制御部50とを備える。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

信号伝達装置及びこれを用いたモータ駆動装置

【課題】ドライバチップの異常検出期間が短過ぎると、異常パルス信号のパルス生成が停止された後、異常判定期間の経過前に異常パルス信号のパルス生成が再開されてしまい、コントローラチップでドライバチップの異常を認識することができなくなるおそれがあり、2つの回路を絶縁しつつ一方の異常を確実に他方に伝達することのできる信号伝達装置、及びこれを用いたモータ駆動装置を提供する。

【解決手段】信号伝達装置100は、第1回路110と第2回路120との間を絶縁しながら信号伝達を行うものであり、第1回路110は、第2回路120から伝達される異常パルス信号Sbを監視して第2回路120の異常有無を判定し、第2回路120は、第2回路120で異常が検出されてから少なくとも第1回路110で第2回路120の異常有無が判定されるまで異常パルス信号Sbを異常状態に保持する。

(もっと読む)

ゲート駆動回路

【課題】 リカバリー電流を低減させつつ、出力MOSトランジスタのスイッチング応答性を高くすることができるゲート駆動回路を提供する。

【解決手段】 制御信号Scdの信号レベルが所定の第1レベルLから第2レベルHへ遷移する第1遷移を契機として出力MOSトランジスタ2のゲートへ充電を開始する第1チャージ回路6と、制御信号Scdの第1遷移または第1期間Tp1の経過を契機として出力MOSトランジスタ2のゲートへの充電を開始する第2チャージ回路7と、制御信号Scdの第1遷移から第1期間Tp1より長い所定の第2期間Tp2経過後に出力MOSトランジスタ2のゲートへ充電を開始する第3チャージ回路8とを備え、第2チャージ回路7の単位時間あたりの充電量は、第1チャージ回路6および第3チャージ回路8の単位時間あたりの充電量より少ない。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

半導体装置

【課題】インバータ回路とそれを構成するスイッチ素子を駆動・制御する駆動・制御回路において、追加回路規模が少なく、所望の負電位を動的に印加できる駆動・制御回路、また、インバータ回路における短絡電流を削減し、損失の少ない電力変換回路を提供する。

【解決手段】半導体装置において、第1,第2スイッチ素子(下側アームのスイッチ素子LSW,同様の上側アームのスイッチ素子)を有するインバータ回路と駆動回路(L側ゲート駆動回路LGD,同様のH側ゲート駆動回路)と制御回路とを有し、駆動回路は、スイッチ素子のゲート電極をソース電位に駆動する回路と、スイッチ素子のゲート電極を負電位に駆動する回路とを有し、負電位に駆動する回路の出力ノードとスイッチ素子との間に直列にコンデンサが接続され、制御回路は、スイッチ素子がオフ状態からオン状態になる直前のスイッチ素子のゲート電極の電圧をソース電位と同じであるように制御する。

(もっと読む)

電力変換装置

【課題】複数の電力変換回路を有し、これらの電力変換回路に属する半導体モジュールを積層した電力変換装置において、電力変換回路間のサージ電圧による干渉を低減する。

【解決手段】複数の電力変換回路の正極端子を接続する正極接続プレート66にスリット100,102を設ける。一方、正極接続プレート66が配置される固定台68上にかしめ突起105を設ける。かしめ突起105を、正極接続プレートのスリット100,102に貫通させ、かしめ突起105の先端をつぶして正極接続プレート66をかしめ、固定台68に固定する。正極接続プレートを固定するためのボルト等を用いていないため、負極接続プレート70の面積を広くすることができ、サージ電圧による干渉を低減できる。

(もっと読む)

ゲート駆動回路

【課題】ゲート駆動回路に無駄な電流が流れないようにし、消費電力を低減する。

【解決手段】本発明のゲート駆動回路は、制御電源12と、一次巻線と二次巻線とを有するトランス8と、第1のスイッチング素子21と、第2のスイッチング素子14と、整流素子15と、容量素子20と、を備え、第1のスイッチング素子21は、制御電源12と前記一次巻線の一端との間に接続され、第2のスイッチング素子14は、前記一次巻線の他端に接続され、整流素子15の両端は、前記一次巻線の両端に並列接続され、容量素子20の一端は、前記一次巻線の一端または他端に接続され、第1のスイッチング素子21及び第2のスイッチング素子14のうち一方の導通時に容量素子20が制御電源12により充電され、且つ、第1のスイッチング素子21及び第2のスイッチング素子14のうち他方の導通時に容量素子20が放電されるように構成される。

(もっと読む)

電力用半導体装置

【課題】複数の電力用半導体素子を並列接続する場合において、スイッチング損失を従来よりも低減する。

【解決手段】電力用半導体装置200は、互いに並列に接続された第1および第2の電力用半導体素子Q1,Q2と、駆動制御部100とを備える。駆動制御部100は、外部から繰返し受けるオン指令およびオフ指令に応じて第1および第2の電力用半導体素子の各々をオン状態またはオフ状態にする。具体的には、駆動制御部100は、オン指令に対して、第1および第2の電力用半導体素子Q1,Q2を同時にオン状態にする場合と、第1および第2の電力用半導体素子Q1,Q2の一方をオン状態にした後に他方をオン状態にする場合とに切替え可能である。駆動制御部100は、オフ指令に対して、第1および第2の電力用半導体素子Q1,Q2の一方をオフ状態にした後に他方をオフ状態にする。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

41 - 60 / 617

[ Back to top ]