Fターム[5H740JA01]の内容

Fターム[5H740JA01]に分類される特許

21 - 40 / 617

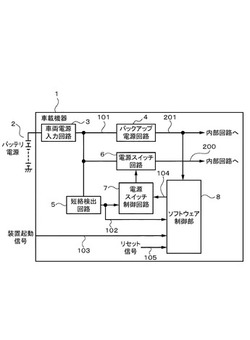

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

ラインフィルタ、ラインフィルタを搭載したスイッチング電源及び画像形成装置

【課題】 スイッチング部からの熱を放熱する放熱部の影響によるノイズを低減し、且つ、Xコンデンサの電荷を放電する放電抵抗による消費電力を低減する。

【解決手段】 スイッチング部の放熱部とトランスの入力側を接続して、前記放熱部に流れる電流をスイッチング手段に還流する第1の電流経路を形成し、整流部と前記トランスとの間のライン間に接続されたコンデンサと、トランスの出力側と、コンデンサを接続した第2の電流経路を形成したラインフィルタ。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

ゲート駆動回路

【課題】ターンオン時のスイッチング特性が変動せず、また、電流回生時の電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲート駆動回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるノーマリオフ型スイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲート駆動回路であって、制御回路とスイッチング素子のゲートとの間に接続され、コンデンサC1と抵抗R1との直列回路と並列にノーマリオン型スイッチグ素子Q2が接続され、スイッチング素子Q2のゲートはGNDに接続され、スイッチング素子Q1のゲート電圧に応じたゲートバイアス電流を供給し、スイッチング素子Q1のオフ時にはゲート・ソース間を短絡する。

(もっと読む)

パワー半導体モジュール

【課題】 電力損失が小さく、発生ノイズが小さいパワー半導体モジュールを実現する。

【解決手段】 ワイドバンドギャップ半導体を利用したユニポーラ型スイッチング素子(ワイドバンドギャップ半導体スイッチング素子)1とシリコン半導体を利用した絶縁ゲート型バイポーラトランジスタ(Si−IGBT)2を並列接続したパワー半導体モジュールで、ワイドバンドギャップ半導体素子1のチップ面積はSi−IGBT2のチップ面積よりも小さいことを特徴とする。

(もっと読む)

電力変換装置

【課題】スイッチング素子を複数並列に接続して逆変換器等を構成した場合にも簡易かつ確実に電流アンバランスを解消することができる電力変換装置を提供する。

【解決手段】ゲート調整回路12は、基準素子ユニット501における直流電流検出器541の直流電流の検出値Id1および、基準素子ユニット501以外の素子ユニット502における直流電流検出器542の直流電流の検出値Id2に基づいて、それぞれ時間γ1および時間γ2から時間差Δtを電流アンバランス量として算出する。ゲート調整回路12は、時間差Δtを次の第1状態におけるターンオフのタイミングで、ゲート駆動回路552uの動作信号S2uに遅延時間として付加する。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

絶縁不良診断装置および絶縁不良診断方法

【課題】高電圧バッテリ10に接続される部材(インバータINV1〜INV4)が増加すると、高電圧バッテリ10と車体との間の浮遊容量が大きくなったり、絶縁抵抗の抵抗値が小さくなったりすることで、これら浮遊容量や絶縁抵抗に起因したインピーダンスが低下し、絶縁不良の診断精度の低下を招くおそれがあること。

【解決手段】製品出荷に先立ち、高電圧バッテリ10にインバータINV1〜INV4が接続され、これらが車体に搭載された後、出力部40から診断信号dsを出力する。そして、これに伴う抵抗体42およびコンデンサ44間の電位の変動量に基づき、絶縁不良の有無を判断する判定値を生成して、不揮発性メモリ48に記憶する。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

ゲート駆動回路

【課題】ワイドギャップ半導体のターンオフの速度を高速化できるゲート駆動回路。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

(もっと読む)

スイッチング回路及びDC−DCコンバータ

【課題】スイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【解決手段】ハイサイドスイッチと、整流要素と、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、高電位端子と出力端子との間に接続されている。前記整流要素は、前記出力端子と低電位端子との間に、前記低電位端子から前記出力端子に向かう方向を順方向として接続される。前記駆動回路は、入力されるハイサイド制御信号に応じて前記ハイサイドスイッチの制御端子に第1の電圧を供給してオンさせ、前記出力端子の電圧が規定値以上に上昇したとき前記ハイサイドスイッチの制御端子に前記第1の電圧よりも高い第2の電圧を供給する。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

ゲート駆動装置

【課題】動作条件が変化しても、損失およびノイズ特性に優れたスイッチング制御を実現できるゲート駆動装置を得ることを目的としている。

【解決手段】定電流駆動回路11Cと、定電圧駆動回路11Vと、スイッチング素子2の動作条件をパラメータとして、定電流駆動回路11Cおよび定電圧駆動回路11Vのそれぞれでスイッチング素子2を駆動させたときの、スイッチング損失および放射ノイズの一方または両方についての情報を保持する回路特性情報保持部15と、スイッチング素子2の動作条件を検出する動作条件検出部14と、検出した動作条件と、保持する回路特性情報に基づき、定電流駆動回路11Cと定電圧駆動回路11Vのうちのいずれか一方をスイッチング素子2の駆動回路として切替える駆動回路切替部12、13とを備えるように構成した。

(もっと読む)

ゲート駆動装置

【課題】ゲート駆動装置で駆動される複数個のスイッチングデバイスにおけるVth、ミラー電圧のバラツキによるスイッチング速度のバラツキを抑え、かつ損失のバラツキを最小限とすることができるゲート駆動装置を得ることを目的とする。

【解決手段】スイッチングデバイス1へのゲート信号を定電流出力で作成する定電流パルスゲート駆動回路2、ゲート信号を定電圧出力で作成する定電圧パルスゲート駆動回路3、および定電流パルスゲート駆動回路2の動作と定電圧パルスゲート駆動回路3の動作との切替を行う判定/切替回路4を備えた。

(もっと読む)

電力変換装置用の駆動回路および電力変換装置

【課題】上側のスイッチング素子の誤動作を抑制できる電力変換装置用の駆動回路を提供する。

【解決手段】第1回路10は、直流電源E1の低電位端と高電位端との間で相互に直列に接続される第1素子11及び第2素子12を有し、第1素子11は高電位端側に設けられ、第2素子12は低電位端側に設けられる。第1素子11及び第2素子12は、その両方がスイッチである。第2回路20は、第2素子12の両端の電圧が所定値よりも大きいときにスイッチング素子Tx1を非導通とし、当該電圧が所定値よりも小さいときにスイッチング素子Tx1を導通させる。スイッチ素子32は、第1素子11と並列に接続され、スイッチング素子Tx1が非導通である状態で導通し、スイッチング素子Tx1が導通する状態で非導通する。

(もっと読む)

低Vf逆導通FET回路及び多機能FET回路用IC

【課題】内部ダイオード又は外部ダイオードを使用せずに、逆方向へ導通可能なMOS−FET回路を提供すること。

【解決手段】MOS−FET(10)と、このMOS−FET(10)のドレインをマイナス入力に接続し、ソースをプラス入力に接続したオペアンプ(15)と、このオペアンプ(15)の出力を一方の入力とし、ゲート端子(14)を他方の入力とした第一OR回路(17)とからなり、前記第一OR回路(17)の出力を前記MOS−FET(10)のゲートに接続した。

(もっと読む)

スイッチング素子用ゲート駆動装置

【課題】同時オン防止回路を有し、かつ3レベル電力変換装置の構成部品を少なくし信頼性を向上した3レベル電力変換装置のゲート駆動装置を提供する。

【解決手段】3レベル電力変換装置は、一対の直流電源端子間に順次直列に接続された第一ないし第四の半導体スイッチング素子4〜7をそれぞれ、第一ないし第四のゲート駆動回路28〜31により駆動し、第一及び第二の半導体スイッチング素子4、5のみをオンしたときプラス出力、第二及び第三の半導体スイッチング素子5、6のみをオンしたとき零出力、そして、第三及び第四の半導体スイッチング素子6、7のみをオンしたときマイナス出力を出力する。その際、第一の駆動回路28と第三の駆動回路29、第二の駆動回路30と第四の駆動回路31をそれぞれ同一の基板に実装し、各基板上において、通信線を介して相互に論理回路に接続し、いずれか一方のゲート駆動回路がオンしている時に他方のゲート駆動回路をオフする。

(もっと読む)

ゲート駆動回路

【課題】従来のゲート駆動回路で高速スイッチングさせる場合、複数の直流電源と、複数の制御用スイッチと、複雑な制御回路が必要で、装置が大型で、高価格となっていた。

【解決手段】制御用スイッチ直列回路の中点にスイッチング素子のゲート端子を、制御用スイッチ直列回路と並列に直流電源を、制御用スイッチ直列回路の正極端子と制御対象となるスイッチング素子のソース端子との間に小さい静電容量のコンデンサとダイオードとの並列回路と十分大きい静電容量を有するコンデンサとの直列回路を、スイッチング素子のソース端子と制御用スイッチ直列回路の負極端子との間に小さい静電容量のコンデンサとダイオードの並列回路を、各々接続する。

(もっと読む)

21 - 40 / 617

[ Back to top ]