Fターム[5H740KK08]の内容

電力変換一般 (12,896) | 主回路スイッチング素子への制御信号の伝達 (818) | 光によるもの (86) | 制御入力に光を用いたもの (16)

Fターム[5H740KK08]に分類される特許

1 - 16 / 16

スイッチング素子用ゲート駆動装置

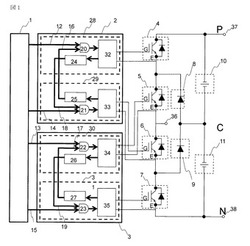

【課題】同時オン防止回路を有し、かつ3レベル電力変換装置の構成部品を少なくし信頼性を向上した3レベル電力変換装置のゲート駆動装置を提供する。

【解決手段】3レベル電力変換装置は、一対の直流電源端子間に順次直列に接続された第一ないし第四の半導体スイッチング素子4〜7をそれぞれ、第一ないし第四のゲート駆動回路28〜31により駆動し、第一及び第二の半導体スイッチング素子4、5のみをオンしたときプラス出力、第二及び第三の半導体スイッチング素子5、6のみをオンしたとき零出力、そして、第三及び第四の半導体スイッチング素子6、7のみをオンしたときマイナス出力を出力する。その際、第一の駆動回路28と第三の駆動回路29、第二の駆動回路30と第四の駆動回路31をそれぞれ同一の基板に実装し、各基板上において、通信線を介して相互に論理回路に接続し、いずれか一方のゲート駆動回路がオンしている時に他方のゲート駆動回路をオフする。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

鉄道車両用ゲートドライブ回路

【課題】 ゲートドライブ回路のゲート指令部とゲート電源部内の高圧側と低圧側の絶縁を可能とし、さらにゲートドライブ回路の小型化を図ることができる鉄道車両用ゲートドライブ回路を提供することを目的とする。

【解決手段】 実施形態の鉄道車両用ゲートドライブ回路は、架線と接続されるトランス103と、トランス103の架線側に接続され、鉄道車両の電力変換器のスイッチング素子を駆動する2つのスイッチ102a、102bと、トランスの架線とは反対側で接続する整流回路104を介してゲート電源を供給し、トランスの架線とは反対側で接続する信号検出回路106を介してゲート指令を出力する鉄道車両用ゲートドライブ回路を有している。

(もっと読む)

電力変換回路の駆動装置

【課題】フェール信号を出力するフェール用フォトカプラPCfの2次側を直列接続する場合、その配線長が長くなることから、フェール信号のノイズに対する耐性が低下するおそれがあること。

【解決手段】インバータIV1、コンバータCVおよびインバータIV2を構成する上側アームのスイッチング素子と下側アームのスイッチング素子とは、基板30に対して2列に配置され、その制御端子(ケルビンエミッタ電極KE、センス端子ST、ゲートG)が基板30に差し込まれている。これら2列の間には、フェール用フォトカプラPCfが配置されている。インバータIV1に対応するフェール用フォトカプラPCfは、隣接するもの同士で直列接続され、各列の端部が接続されることでU字型の配線構造を有し、その端部がマイコン20に接続されている。

(もっと読む)

ゲート駆動回路

【課題】電力用半導体素子を不必要にターンオフさせないようにし、損失を増加させないようにする。

【解決手段】IGBT4等のゲート駆動回路で、コレクタ・ゲート間にツェナーダイオード17を接続したものにおいて、IGBT4のチップ温度Tjをダイオード8を介して検出し、温度検出値Tjが設定値以下の時のみスイッチ素子9をオンしてツェナーダイオード17を動作させ、サージ電圧を低減させるためのクランプ動作を行なうが、温度検出値Tjが設定値以上の時はスイッチ素子9をオフとして、クランプ動作をさせないようにする。

(もっと読む)

スイッチング回路及び電力変換回路

【課題】スイッチング回路や電力変換回路について、単アーム構造の場合でも導通制御端子電源の自給化を可能とする。

【解決手段】スイッチ素子17と制御端子電源用コンデンサ21を備え、制御端子電源用コンデンサの放電によりスイッチ素子のゲート端子に電圧を印加するようにされているスイッチング回路について、制御端子電源用コンデンサの負側端子は、主電源5の基準電圧端子18に接続するとともに、ハーフブリッジ回路22を介してゲート端子に選択的に接続できるようにし、制御端子電源用コンデンサの正側端子は、ハーフブリッジ回路24を介して主電源の正側端子15とスイッチ素子のソース端子に対して選択的に接続できるようにする。そして制御端子電源用コンデンサは、正側端子が主電源に接続することで充電がなされる一方で、負側端子がゲート端子に接続し、正側端子がソース端子に接続することで放電する。

(もっと読む)

故障検出回路および電力調整器

【課題】カレントトランスを用いることなく、高価なICや規模の大きな回路構成を必要とすることなく、半導体素子の故障を検出できるようにする。

【解決手段】交流電源2とヒータ3との間の電力供給ラインに設けられてオンオフ制御されるスイッチング素子としてのサイリスタ4,5の故障を検出する回路12であって、サイリスタ4,5の両端電圧を、波形整形し、閾値と比較してデジタル信号に変換する変換部としての波形整形・比較部13と、変換されたデジタル信号を、電気的に絶縁して判定部としてのマイコン8に伝達する光結合部14と、伝達されたデジタル信号およびサイリスタ4,5に対するオンオフの制御指令に基づいて、故障の有無を判定する前記判定部としてのマイコン8とを備えている。

(もっと読む)

安定化電源装置及びその制御方法

【課題】フォトカプラが故障した場合にも安定動作を持続する。

【解決手段】出力電圧OUTにおける基準値からの差分をフォトカプラを介して帰還し、差分に応じて入力電圧INを電圧変換して安定した出力電圧OUTを得る安定化電源装置において、フォトカプラ17、18と、フォトカプラ17、18から一つを選択する切替回路16と、切替回路16によって選択したフォトカプラに差分を供給するフォトカプラ駆動回路14と、選択されたフォトカプラの駆動電圧および/または駆動電流を監視し、駆動電圧および/または駆動電流が所定の範囲外であることを検出した場合には、フォトカプラの選択を変更するように切替回路16を制御するフォトカプラ劣化検出回路15と、を備える。

(もっと読む)

ドライバ装置

【課題】トランジスタの異常動作検出と異常信号出力の両機能を備えつつも小型化が図れるドライバ装置を提供する。

【解決手段】外部からの入力信号を受けてトランジスタを駆動制御するドライバ回路と、トランジスタのコレクタに接続されたセンス端子と、センス端子の電位と閾値電圧とを比較するコンパレータと、コンパレータの出力に基づいてセンス端子の電位を保持するラッチ回路と、コンパレータの出力に基づいてタイマー動作を開始するとともに所定時間経過後にセンス端子の電位の保持を解除するためのリセット信号をラッチ回路に出力するタイマー回路とを有し、センス端子の電位に基づいてトランジスタの異常動作を検出するセンス回路と、センス端子に接続され閾値電圧と同じかそれより高い電圧で動作し、異常信号を出力する異常信号出力回路とを備えている。

(もっと読む)

ゲート駆動回路

【課題】還流ダイオードの省略化を図ること。

【解決手段】MOS−FETにおけるドレイン電位がソース電位より低くなると、PNPトランジスタ(46)のベース側からドレイン側へ電流を流すダイオード(48)の接続ラインが設けられている。これにより、PNPトランジスタ(46)のベース電位がゼロになり、MOS−FETのゲートにオン電圧が印可される。

(もっと読む)

半導体スイッチを制御するための光学的電力供給型駆動回路および方法

【課題】第1の半導体スイッチ(52)を制御するための、光学的電力供給型駆動回路(40)および方法を提供すること。

【解決手段】光学的電力供給型駆動回路(40)は、光ファイバケーブル(14)から第1の光信号に応答して第1の電圧を出力するように構成された光電池(100)と、光電池(100)に電気的に結合され、第1の電圧から受け取った電気エネルギーを蓄積し、第2の電圧を出力するように構成されたエネルギー蓄積デバイス(102)を含む。光学的電力供給型駆動回路(40)は、光電池(100)およびエネルギー蓄積デバイス(102)の両方に電気的に結合された電気回路をさらに含む。電気回路は、第2の電圧によって付勢される。電気回路は、第1の半導体スイッチ(52)の動作を制御するために、第1の電圧を受け取り、第1の電圧に応答して第3の電圧を出力する。

(もっと読む)

電圧駆動型半導体スイッチング素子の制御装置

【課題】 インバータ運転時でも、ゲート駆動回路や電源回路のコンデンサを過電圧で破壊してしまう虞がなく、分圧抵抗が小耐電力容量ですむ電圧駆動型半導体スイッチング素子の制御装置を提供する。

【解決手段】 直列接続されて主回路を構成する複数のIGBT31と、該IGBT31のゲートにゲート信号を供給するゲート駆動回路32と、IGBT31の端子間に並列接続され主回路からゲート駆動回路32に電力を供給する電源回路33と、該電源回路33に設けられ第1の分圧抵抗34を介して主回路から供給された電力を蓄積するコンデンサ37を備えた制御装置で、電源回路33には、第1の分圧抵抗34とコンデンサ37の間に直列に第2の分圧抵抗35と逆流阻止用ダイオード36が設けられ、かつ第2の分圧抵抗35に並列にスイッチ39が設けられていると共に、コンデンサ37の端子間に並列に過電圧検出器38が設けられている。

(もっと読む)

ゼロクロス検出装置および画像形成装置

【課題】比較的簡単かつ安価な回路構成でゼロクロスポイントを正確に検出する。

【解決手段】フォトカプラ102(ゼロクロス信号生成回路)は、交流電源101に基づいてその交流電圧のゼロクロスポイントを示すゼロクロス信号を生成する。ゲート信号生成手段は、交流電圧を受けて、その本来のゼロクロスポイントの近傍範囲を包含するパルス幅のゲート信号を発生する。ゲート信号生成手段は、ダイオードブリッジ103、降圧回路104、ノイズフィルタ105、方形波生成部106の組み合わせにより構成される。論理積回路107は、このゲート信号とフォトカプラ102(ゼロクロス信号生成回路)の出力との論理積をとる。ラッチ回路108(パルス信号形成回路)は、論理積回路107の出力中の最初の信号エッジでパルスの前縁を形成し、ゲート信号の後縁でパルスの後縁を形成する。ラッチ回路108の出力パルスが、求めるゼロクロス信号となる。

(もっと読む)

スイッチング回路

【課題】ノイズや電圧変動によって、2つの半導体スイッチング素子が同時に導通状態になる短絡の発生を確実に防止することができるスイッチング回路を提供する。

【解決手段】第1及び第2の駆動回路用電源回路4,5を、共通の直流電源Eを利用するように構成する。第1の駆動回路用電源回路を、第1及び第2のコンデンサC1及びC2と、コンデンサ充電回路と、順方向電圧印加回路と、逆方向電圧印加回路とから構成する。コンデンサ充電回路(Q3)は、第2の半導体スイッチング素子Q2が導通状態にある期間導通状態になって直流電源Eから供給される電荷で第1及び第2のコンデンサC1及びC2を充電する。第2のコンデンサC2の両端電圧を逆方向電圧として、第1のスイッチング素子用ゲート駆動回路Q1の第2の電源端子22と第1の半導体スイッチング素子Q1のエミッタとの間に印加する。

(もっと読む)

スペクトル拡散アイソレータ

回路パッケージは、機能回路部を含む第1および第2のユニットを含む。少なくとも1つのRF絶縁リンクが、第1のユニットと第2のユニットとを相互接続し、第1のユニットと第2のユニットとの間の電圧絶縁を提供する。このRF絶縁リンクは、第1の周波数と第2の周波数との間で掃引されるRF搬送波信号を使用して、第1のユニットと第2のユニットとの間にデータを提供する。  (もっと読む)

(もっと読む)

1 - 16 / 16

[ Back to top ]