Fターム[5J001CC00]の内容

パルス回路 (4,711) | 波形 (673)

Fターム[5J001CC00]の下位に属するFターム

パルスの伸長(前縁一致、後縁遅延) (77)

パルスの圧縮(前縁圧縮、後縁一致) (9)

パルスの遅延(前縁・後縁遅延) (491)

パルスの圧縮(前縁一致・後縁圧縮) (65)

パルスの遅延(入力後縁と出力前縁の一致) (8)

パルスの遅延(入出力波形の重複なし) (2)

パルスの圧縮(前縁・後縁圧縮) (3)

パルスの伸長(単安定回路波形) (3)

階段状の波形を有するもの (1)

Fターム[5J001CC00]に分類される特許

1 - 14 / 14

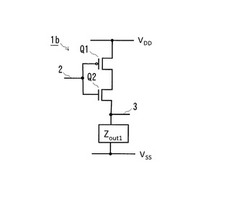

パルス発生回路

【課題】入力信号にジッタが含まれていても安定した時間幅のパルスを出力する。

【解決手段】パルス発生回路は、ゲートが入力端子2に接続され、ソースが電源電圧VDDに接続されたPMOSトランジスタQ1と、ゲートが入力端子2に接続され、ドレインがPMOSトランジスタQ1のドレインに接続され、ソースが出力端子3に接続されたNMOSトランジスタQ2と、一端が出力端子3に接続され、他端が接地電圧VSSに接続された負荷インピーダンスZout1とを有する。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号が入力され、入力されたクロック信号の波形の立ち上がりに合わせて波形が立ち上がりパルス幅が一定の幅であるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力が一方の入力側に入力される否定論理和回路120と、否定論理和回路120の出力信号を遅延させる第1遅延回路130を有し、第1遅延回路130により遅延された否定論理和回路120の出力を否定論理和回路120の他方の入力側にフィードバックする帰還回路140と、否定論理和回路120の出力信号が入力される第2ローパスフィルタ150と、を備える。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

CML−CMOS変換器

【課題】CMLレベルでスイングする信号をCMOSレベルでスイングする信号に変換する過程において、デューティ比の不一致を防止するCML−CMOS変換器を提供すること。

【解決手段】第1基準レベルを中心にスイングする正CML信号を第2基準レベルにシフトする第1基準レベルシフト部、第1基準レベルを中心にスイングする負CML信号を第2基準レベルにシフトする第2基準レベルシフト部、第1基準レベルシフト部の出力信号のスイング幅をCMOSレベルに増幅する第1CMOS反転部、第2基準レベルシフト部の出力信号のスイング幅をCMOSレベルに増幅する第2CMOS反転部、第1CMOS反転部の出力信号に応じて第1及び第2CMOS反転部にソース電流を提供する第1バイアス部、第1CMOS反転部の出力信号に応じて第1及び第2CMOS反転部にシンク電流を提供する第2バイアス部を備えるCML−CMOS変換器を提供する。

(もっと読む)

通信装置、ベースバンド信号処理装置及び受信処理方法

【課題】入力信号におけるデューティ比の制約を無くし、コストや基板面積や回路設計上の制約を取り払うことができる通信装置、ベースバンド信号処理装置及び受信処理方法を提供する。

【解決手段】VCTCXO16と、VCTCXO16からの第1クロック信号aを分周するクロック分周回路27と、クロック分周回路27から出力された分周クロック信号bが入力され、入力された分周クロック信号bを所定倍して第2クロック信号cを生成するPLL部28と、PLL部28で生成された第2クロック信号cによってベースバンド信号処理を行うベースバンド信号処理部22と、を含む。第1クロック信号aと第2クロック信号cとが同じ周波数となるように生成する。

(もっと読む)

遅延ロックループ回路

【課題】多相出力発振回路を備える位相遅延回路は、その多相出力発振回路の位相ジッタが遅延回路の遅延時間に影響が及ぶ。

【解決手段】遅延ロックループ回路は、第1の遅延ロックループ回路と、第2の遅延ロックループ回路と、入力信号遅延回路とを具備し、入力信号遅延回路は、入力信号に遅延を与えて出力する。第1の遅延ロックループ回路は、基準クロックに同期し、基準クロックを遅延させて複数の位相信号を出力する第1の遅延線回路を備える。第2の遅延ロックループ回路は、基準クロックを入力し、複数の位相信号に基づいて生成される目標位相信号に同期するように遅延量が制御される第2の遅延線回路と、遅延量が固定されている第1の固定遅延回路とを備える。入力信号遅延回路は、第2の遅延線回路の遅延量に等しい遅延量に制御され、入力信号に遅延を与えて出力する第3の遅延線回路を備える。

(もっと読む)

信号処理装置

【課題】簡単な回路構成で、入力信号レートに応じて、デューティサイクルが約50%に近いクロック信号を生成し得る信号処理装置を提供する。

【解決手段】バーストモードのシリアル信号をパラレル信号に変換したときに得られる入力クロック信号と有効データ識別パルスとを利用して、カウンタ142により有効データ識別パルスの入力タイミングから次の有効データ識別パルスの入力タイミングまでの入力クロック信号のクロック数をカウントし、乗算器145にてこのカウント値の1/2の値を求め、比較器146にてこの1/2の値とカウンタ142のカウント値とを比較し、この比較結果に基づきFF回路143にて有効データ識別パルス周期の略1/2期間で立ち上がりまた略1/2期間で立ち下がりへ変化する出力クロック信号を生成する。

(もっと読む)

容量装置及び半導体装置並びにそれを用いたマルチバイブレータ

【課題】二端子間に接続されて用いられる容量装置及び半導体装置並びにそれを用いたマルチバイブレータに関し、寄生容量の影響を低減できる容量装置及び半導体装置並びにそれを用いたマルチバイブレータを提供することを目的とする。

【解決手段】 本発明は、二端子(a、b)間に接続される容量装置(C100、C200)において、複数の容量素子(C10、C20)を、二端子(a、b)の両方の端子から見た素子容量(C11、C21)及び寄生容量(C12、C22)の配置が対称となるように接続したことを特徴とする。

(もっと読む)

DLL回路

【課題】 位相が誤ってロックされるという誤ロック状態の防止が図られたDLL回路を提供する。

【解決手段】 フリップフロップ17_1,17_2,イクスクルーシブノア回路17_3からなるコースサーチ回路17で、リファレンスクロックCLKINとフィードバッククロックCLKFBとを比較しておおまかなロックポイントを求め、次いで、フリップフロップ18_1,18_2,18_5,切替回路18_3,遅延回路18_4からなるファインサーチ回路18で、リファレンスクロックCLKINの立ち上りと、二分周フィードバッククロックCLKFB2の立ち上りおよび立ち下り双方との位相を比較することによって、リファレンスクロックCLKINとフィードバッククロックCLKFBとの間の位相が所定の位相となるように可変遅延セル16の遅延量を制御回路19で制御する。

(もっと読む)

DUTY補正回路

【課題】 波形歪みが補正された信号を用いて復調を行うことによりビット誤り率の低いDUTY補正回路を提供する。

【解決手段】 波形の形状を観測することで、波形歪を検出することにより歪補正を行うので、受信マンチェスタ信号のDUTY比が50%を維持できない場合でも本DUTY補正回路を使用することで、補正信号は50%近傍となり、より精度の高い再生クロックを作成することができる。また、精度の高い再生クロックと波形歪みが補正された信号を用いて復調を行うことで、ビット誤り率の低い復調が可能となる。

(もっと読む)

1 - 14 / 14

[ Back to top ]