Fターム[5J001CC04]の内容

Fターム[5J001CC04]に分類される特許

1 - 20 / 65

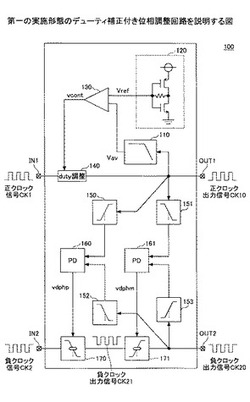

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

パルス幅調整回路及びこれを用いたデューティ比補正回路

【課題】入力クロック信号のパルス幅を安定して調整すること。

【解決手段】第1及び第2の電源間に設けられたパルス幅調整回路であって、ゲートに入力パルス信号INが入力される第1導電型の第1のトランジスタP1と、第1のトランジスタP1と第2の電源との間に設けられ、ゲートに入力パルス信号INが入力される第2導電型の第2のトランジスタN1と、第1のトランジスタP1と第1の電源との間に設けられ、ゲートに入力される第1の制御信号に応じて流れる電流が制御される第1導電型の第3のトランジスタP2と、第1のトランジスタP1と第1の電源との間に、第3のトランジスタP2と並列に設けられた第1の電流源回路102と、を備えるパルス幅調整回路。

(もっと読む)

半導体回路

【課題】DCC回路を備えたDLL回路の消費電力を低減させる。

【解決手段】制御信号DCCENに基づいて活性化・非活性化が制御されるデューティ変更検出回路21であって、入力されたクロック信号に基づいて生成されたクロック信号のデューティとあらかじめ設定されたデューティとを比較しその結果を出力するデューティ変更検出回路21と、デューティ変更検出回路の出力が生成されたクロック信号のデューティがあらかじめ設定されたデューティである目標値近傍にあることを示すときにはデューティ変更検出回路21を非活性化する制御信号DCCENを出力すると共に目標値近傍に無いときにはデューティ変更検出回路21を活性化する制御信号DCCENを出力するデューティ判定回路23とを備える。

(もっと読む)

PWM制御装置及びモータ制御装置

【課題】電圧指令に対する出力電圧の不連続な変化を簡易に解消する。

【解決手段】PWM信号及び反転PWM信号のパルスオン時間をそれぞれ検出するパルス時間検出器40,50と、パルス時間検出器40,50が検出したパルス時間と所定のデッドタイムを比較し、パルスオン時間がデッドタイム未満の時はそのパルスオン時間を、デッドタイム以上の時はデッドタイムをディレイ時間としてそれぞれ出力する比較回路60,70と、比較回路70からのディレイ時間に基づき、PWM信号の立ち上がりをディレイさせて駆動信号(PWM_U信号)を生成する可変ディレイ回路80と、比較回路60からのディレイ時間に基づき、反転PWM信号の立ち上がりをディレイさせて駆動信号(PWM_nU信号)を生成する可変ディレイ回路90とによってPWM制御装置を構成する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

パルス幅変調回路及びそれを用いたスイッチングアンプ

【課題】 温度係数によって直流バイアス電流Icおよび放電電流Idの電流値が変動する場合であっても、入力信号に正確に対応するパルス幅変調信号を出力する。

【解決手段】 電流生成回路14は、定電流I1を生成する定電流回路31と、定電流I1の1/2の電流値である電流I2と交流電圧esを電流に変換した電流Δiとを加算した電流I2+Δiを生成する差動回路32と、定電流I1を電圧Vb2に変換する電流電圧変換手段33と、電流電圧変換手段33から供給された電圧Vb2を電流に変換し、放電電流Idを生成する電圧電流変換手段34と、電流I2+Δiを電圧Vb1に変換する電流電圧変換手段35と、電流電圧変換手段35から供給された電圧Vb1を電流に変換し、充電電流Ic+Δiを生成する電圧電流変換手段36とを備える。

(もっと読む)

フリップフロップ、半導体集積回路、半導体デバイスおよびブレードサーバ

【課題】

回路オーバヘッドが小さく、かつ、ソフトエラーへの耐性が高い、高ソフトエラー耐性のフリップフロップおよび、それを用いた半導体集積回路を提供する

【解決手段】

ソフトエラーに対する耐性の異なる複数のラッチ回路と、前記複数のラッチ回路にクロックを供給するクロック分配部と、を備えたフリップフロップであって、前記複数のラッチ回路は、第一のラッチ回路と、前記第一のラッチ回路よりもソフトエラーに対する耐性の低い第二のラッチ回路の少なくとも2つのラッチ回路であることを特徴とするフリップフロップ。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

局部発振器信号のためのデューティサイクル調整

局部発振器(LO)モジュールは、局部発振器と、フィードバック回路と、を備える。局部発振器は、電源電圧でバイアスがかけられ、デューティサイクルを有する局部発振器信号を生成する。フィードバック回路は、局部発振器信号の電圧レベルを表す第1の電圧信号と、局部発振器信号に関する希望されるデューティサイクルに対応する電源電圧の部分の電圧レベルを表す第2の電圧信号との間の差に応答して局部発振器信号のデューティサイクルの絶対的調整を行う。  (もっと読む)

(もっと読む)

クロックデューティサイクル適合による半導体デバイスの性能の低下の補償

【解決手段】

集積回路のデバイス劣化が、クロック信号のデューティサイクルを適切に適合させることによって補償され得る。この目的で、デューティサイクルと集積回路の全体的な性能特性の間での相関が確立されてよく、またデューティサイクルを修正するためにデバイスの通常の分野の動作の間に用いられてよい。従って、デューティサイクルが効果的に制御され得る一方で、同時にクロック信号周波数の変化及び/又は供給電圧の増大は必要とされないであろうから、効果的な制御戦略の実装が可能になる。

(もっと読む)

PWMパルス生成装置

【課題】低クロック周波数のディジタル回路により高S/Nが確保できるPWMパルス生成装置を提供すること。

【解決手段】アナログの振幅変換信号Mをアナログ・ディジタル変換器11によりディジタル信号に変換し、パルス変換部13でパルス幅変調されたパルス信号を得るようにしたPWMパルス生成装置において、ディジタル信号により遅延時間が制御されるアナログ遅延器20を設け、ディジタルのパルスに更にディジタルの分解能の0/16〜15/16の遅延時間が付加されるようにして、パルスの分解能を16倍に細かくでき、1/16の周波数のクロックで同等の分解能が確保できるようにし、このとき変換テーブル14を設け、アナログ遅延器20を構成している回路素子の特性バラツキが補正されるようにしたもの。

(もっと読む)

1 - 20 / 65

[ Back to top ]