Fターム[5J022CE05]の内容

アナログ←→デジタル変換 (13,545) | タイミング調整・計数系 (1,285) | カウンタ (250)

Fターム[5J022CE05]の下位に属するFターム

アップ・ダウン(U、D)カウンタ (38)

プリセット(プログラマブル)カウンタ (1)

Fターム[5J022CE05]に分類される特許

1 - 20 / 211

信号切替回路およびA/D変換装置

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

AD変換回路及びAD変換方法

【課題】ビット判定時に比較部での比較時間が長くなることによりAD変換時間が長くなることを抑制する。

【解決手段】アナログ電圧生成部11が、受信したアナログ信号を外部クロック信号Φsに同期してサンプリングし、制御信号に基づいて第1のアナログ電圧及び第2のアナログ電圧を生成し、比較部12がクロック信号Φcに同期して第1のアナログ電圧と第2のアナログ電圧の大きさを比較し、制御部13が第1のアナログ電圧と第2のアナログ電圧の電圧差を縮小させていき、比較部12の比較結果に基づいて、外部クロック信号Φsに同期してサンプリングされたアナログ信号に応じたデジタル信号を生成し、中心電圧調整部15が、クロック信号Φcの信号遷移の回数が閾値以上になると、比較部12の入力トランジスタに流れる電流が増加するように、第1のアナログ電圧と第2のアナログ電圧の中心電圧を調整する。

(もっと読む)

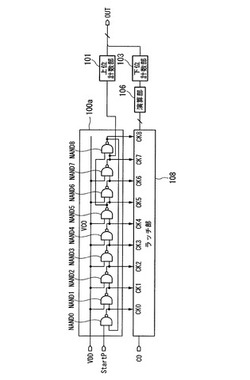

AD変換回路および撮像装置

【課題】カウントクロックの周波数によらず、AD変換により得られるデジタルデータの分解能を向上させることができるAD変換回路および撮像装置を提供する。

【解決手段】ラッチ部108は、比較部109による比較処理の間、クロック生成部18からのクロック信号を通過させ、比較処理の終了に係るタイミングでクロック信号をラッチする。列カウント部103は、クロック生成部18からのクロック信号をカウントすることに加えて、ラッチ部108にラッチされたクロック信号の論理状態に基づいて生成された計数信号をカウントする。

(もっと読む)

固体撮像装置

【課題】消費電流を低減することができる固体撮像装置を提供する。

【解決手段】画素信号のレベルに応じた論理状態の信号を出力する複数の遅延ユニットのいずれかの出力信号の論理状態をラッチするラッチ回路L_7において、複数の遅延ユニットのいずれかの出力信号が入力端子Dに入力される。NAND回路NAND1およびINV回路INV2は、画素信号のレベルに応じた制御信号が出力される制御信号出力タイミングまでは停止しており、制御信号出力タイミングの後に動作する。スイッチ回路SW1,SW2は、制御信号出力タイミングまでは複数の遅延ユニットのいずれかの出力信号を、信号線LN2を介して出力端子Mから出力し、制御信号出力タイミングから所定時間が経過した後のラッチタイミングで複数の遅延ユニットのいずれかの出力信号の論理状態をNAND回路NAND1およびINV回路INV2がラッチするように接続の切替を行う。

(もっと読む)

固体撮像装置

【課題】低周波ノイズ除去に伴う消費電力の増加を最小限に抑えることができる固体撮像装置を提供する。

【解決手段】画素部100は、入射した光の大きさに応じた画素信号を出力する画素101と、補正用基準電圧に応じた補正用画素信号を出力する補正用画素102とを有する。AD変換回路105は、複数の遅延素子が接続された遅延回路を有し、画素信号または補正用画素信号のレベルに対応する数の遅延素子をパルス信号が通過すると、パルス信号が通過した遅延素子の数に応じたデジタル信号を出力する。制御部111は、1フレーム内でm(mは2以上の自然数)行の画素信号のAD変換に対応して1行の補正用画素信号のAD変換を行うように垂直走査部103およびAD変換部105を制御する。ノイズ除去部109は、補正用画素信号のAD変換結果を用いて画素信号のAD変換結果からノイズを除去する。

(もっと読む)

半導体装置、固体撮像装置、およびカメラシステム

【課題】隣接ビアを伝送される信号間の干渉を低減でき、ひいてはビア数の増大を抑止でき、センサを搭載したチップの面積、実装工程を低減でき、結果的にコスト削減を図ることができる半導体装置、固体撮像装置、およびカメラシステムを提供する。

【解決手段】第1チップ110と、第2チップ120と、を有し、第1チップ110と第2チップ120は貼り合わされた積層構造を有し、第1チップと第2チップ間の配線は、ビア114を通して接続され、第1チップ110は、各センサ111で発生したアナログ信号を時間離散化した信号が、対応するビアを介して第2チップに伝送され、第2チップ120は、ビアを介した第1チップから伝送された信号を第1チップでサンプリングしたタイミングとは異なるタイミングでサンプリングする機能と、量子化してデジタル信号を得る機能と、を含む。

(もっと読む)

AD変換器、光電変換装置、および撮像システム

【課題】 並列型AD変換器におけるカウンター回路の動作を精度良く制御する。

【解決手段】 第1クロック信号を計数してカウント信号を出力するカウンター回路と、第1クロック信号に基づいて、第2クロック信号を生成する第2クロック信号生成部と、カウント開始信号を前記第2クロック信号に同期して出力するクロック同期化部と、を有し、カウンター回路は、第2クロックに同期したカウント開始信号に応じて計数を行う。

(もっと読む)

ランプ信号出力回路、アナログデジタル変換回路、撮像装置、ランプ信号出力回路の駆動方法

【課題】 ADCにおいて、ランプ信号の電位の時間に依存した変化の開始に先立って、ランプ信号のランプ開始電位をシフトする形態が知られている。このランプ信号の電位をシフトする方法として、従来は積分アンプの入出力端子間に設けられた積分容量に電流を印加して充放電させていた。従って、ランプ信号のランプ開始電位をシフトするのに積分容量を充放電する期間を要していた。

【解決手段】 ランプ信号のランプ開始電位をシフトさせる電圧供給部を有することを特徴とするランプ信号出力回路である。

(もっと読む)

光電変換システム

【課題】被写体の撮像と並行して、A/D変換器に供給されるカウント信号の検査を行うことができる光電変換システムを提供することを課題とする。

【解決手段】マトリクス状に配置された複数の画素と、ランプ信号を生成する参照信号生成部と、列毎に配置され、画素からの信号をA/D変換するA/D変換器と、ランプ信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介してA/D変換器に供給するカウンタと、A/D変換器とは独立して設けられ、カウント信号の期待値とカウント信号線を介して供給されるカウンタからのカウント信号とを照合することによりカウンタの検査を行うカウンタ検査回路を備え、被写体の撮像と並行に、カウント信号の検査を行えるようにする。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

AD変換装置

【課題】遅延ユニットの温度特性に基づくAD変換データのバラツキを抑制するAD変換装置を提供する。

【解決手段】DCO20は、TAD10を構成するリングディレイライン(RDL)11と同じ温度特性を有するRDL21を用いて、RDL21の駆動電圧が指定電圧V_DCOの時に、RDL21を構成する遅延ユニットをDp段数だけ通過するのに要する時間を周期T_CKとするサンプリングクロックCKを生成し、TAD10は、そのサンプリングクロックCKの周期T_CKを測定期間としてAD変換を実行する。つまり、RDL11を構成する遅延ユニットでの遅延時間は、温度によって変化するが、その変化に応じた分だけ、サンプリングクロックCKの周期T_CK、即ち、TAD10での測定時間も変化させている。

(もっと読む)

AD変換回路および撮像装置

【課題】カウントした計数値の誤差の発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ104から出力される上位用カウントクロックに基づいてカウントを行って第2の上位計数値を取得する。変更部103は、上位カウンタ101のカウントクロックの切換えの際に、カウントクロックの論理状態を所定の状態に変更する。

(もっと読む)

固体撮像装置、撮像装置および撮像方法

【課題】AD変換の処理時間を短くすることができるようにする。

【解決手段】 画素から得られるアナログの画素信号のレベルをディジタルデータに変換するための参照信号であって、第1のゲインの参照信号と、第1のゲインと異なる第2のゲインの参照信号が画素データレベル読み出し時に生成され、アナログの画素信号のレベルと参照信号とが比較され、比較処理と並行してカウント処理が行なわれ、第1のゲインの参照信号との比較処理が完了した時点の第1のカウント値がディジタルデータとして取得され、第1のカウント値が予め設定されている閾値に達していない場合、第2のゲインの参照信号との比較処理が完了した時点の第2のカウント値がディジタルデータとして取得される。

(もっと読む)

A/D変換器、固体撮像装置および電子情報機器

【課題】入射光の光強度をディジタル信号値に変換するのに要する時間を、得られるディジタル信号値が大きな誤差を含むのを回避しつつ短縮することができるA/D変換器を実現する。

【解決手段】固体撮像装置100を構成するA/D変換器120において、一定値ずつ変化するディジタル値を出力するカウンタ124と、該ディジタル値の二乗と該ディジタル値の和に比例させてランプ電圧を発生する二次ランプ発生回路123と、アナログ入力電圧と該ランプ電圧とを比較して大小関係の反転時を検出する比較回路121と、該比較回路121が該反転時を検出したとき、該カウンタから得られる時間情報から、該アナログ入力電圧の平方根を変換して得られるディジタル変換値を取り出すラッチ122とを備え、該アナログ入力電圧の平方根を該ディジタル変換値に変換する。

(もっと読む)

固体撮像装置

【課題】ランプ信号の傾きを変えてAD変換ゲインを上げても横線状のノイズの発生を抑制することができる固体撮像装置を提供することを課題とする。

【解決手段】2次元状に配列された複数の画素と、ランプ信号を生成する参照信号生成回路と、ランプ信号の出力に合わせてカウント動作を行うカウンタ回路と、列毎に配置され、画素からの画素信号をランプ信号と比較処理してAD変換するAD変換回路とを備え、AD変換回路に、画素信号及びランプ信号が入力される比較器とAD変換結果を記憶する記憶部とを設けるとともに、参照信号生成回路の出力端子とランプ信号を入力するための比較器の入力端子との間にランプ信号の傾きを変える振幅変換回路を設けて、ランプ信号に重畳するノイズがランプ信号の傾きに依存して変化するようにする。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

固体撮像装置

【課題】画素数の増大に伴うバッファの数の増大、微細化に伴うプロセスばらつきの増大により、このクロック信号のデューティ比の崩れを抑制する。

【解決手段】固体撮像装置1は、複数の画素10がアレイ状に配置された画素部20と、少なくとも一つのアナログデジタル変換部30を含む第1グループおよび第2グループを有する変換部と、直列に接続された第1のクロックバッファおよび第2のクロックバッファを有するクロック供給部とを含み、第1グループおよび第2グループのアナログデジタル変換部のそれぞれは、比較部およびカウンタ部を有し、第1のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して、第1グループのカウンタ部のそれぞれと第2のクロックバッファに出力し、第2のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して第2グループのカウンタ部のそれぞれに出力する。

(もっと読む)

AD変換回路および固体撮像装置

【課題】消費電流を低減することができるAD変換回路および固体撮像装置を提供する。

【解決手段】比較部109は、AD変換の対象となるアナログ信号と、時間の経過とともに増加または減少する参照信号とを比較し、参照信号がアナログ信号に対して所定の条件を満たしたタイミングで比較処理を終了する。第1のカウント部18は、所定の周波数のクロック信号をカウントクロックとしてカウントを行い、カウント値を出力する。ラッチ部108は、第1のカウント部18から出力されるカウント値をラッチする。ラッチ制御部105は、比較処理の終了に係る第1のタイミングでラッチ部108を有効にし、第1のタイミングを所定の時間だけ遅延させた第2のタイミングでラッチ部108にラッチを実行させる。

(もっと読む)

AD変換回路

【課題】AD変換結果に異常があった場合に、再変換の実行開始までの時間を短縮することのできるAD変換回路を提供する。

【解決手段】実施形態のAD変換回路1は、最上位ビットから順次値が確定する逐次比較レジスタ111を有する逐次比較AD変換部11と、逐次比較AD変換部11の前回の変換結果が書き込まれた変換結果レジスタ12とを備える。このAD変換回路1は、比較部13が、AD変換の途中で、逐次比較レジスタ111の値の確定した範囲のビット値を変換結果レジスタ12の同一範囲のビットの値と比較し、変換開始制御部14が、比較部から比較結果が不一致であることを示す不一致信号UMが出力されたときに、逐次比較AD変換部11へ新たな変換の開始を指示する変換開始信号STを出力する。

(もっと読む)

1 - 20 / 211

[ Back to top ]