Fターム[5J039AB02]の内容

パルスの操作 (9,993) | エッジ(トランジェント)の検出 (82) | 遅延出力との論理操作 (33) | 同期型 (18)

Fターム[5J039AB02]に分類される特許

1 - 18 / 18

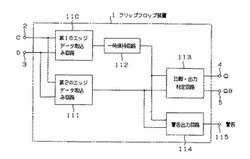

フリップフロップ装置

【課題】クロックCが入力される入力端子2とデータDが入力される入力端子3とを有し、クロックの立上り時または立下り時に同期してデータを取り込む従来のフリップフロップ装置では、データに混じってノイズが入って来た場合、それを真正なデータだと誤認して動作してしまっていた。

【解決手段】フリップフロップ装置1を、クロックの第1のエッジでデータを取り込む第1のエッジデータ取込み回路110と、第2のエッジでデータを取り込む第2のエッジデータ取込み回路111と、第1のエッジデータ取込み回路の出力を一時的に保持する一時保持回路112と、一時保持回路の出力と第2のエッジデータ取込み回路との出力を比較し出力する比較・出力判定回路113と、該2つの出力が異なる時に警告を出力する警告出力回路114とで構成する。

(もっと読む)

デジタル信号処理装置

【課題】フレーム同期式のDSPにおいて、動作クロックの異なる信号処理回路間のデータの受け渡しを簡便に実現する。

【解決手段】各々の動作クロックの異なる複数の信号処理回路のうちから送信側回路と受信側回路を定め、各信号処理回路の動作クロックの全ての立ち上がりエッジが揃うタイミングをデータ受け渡しタイミングとする。送信側回路には、当該送信側回路に与えられるタイミング信号がアクティブレベルであることを条件にデータを出力させる一方、受信側回路には、各動作クロックの周波数の約数を周波数とし、かつデータ受け渡しタイミングを跨ぐ所定期間に亘ってアクティブレベルとなるフレーム同期信号がアクティブレベルであることを条件に、送信側回路から出力されるデータを取り込む処理を実行させる。

(もっと読む)

半導体集積回路及びエッジ検出方法

【課題】ポート機能の変更時における誤エッジ検出を防止する。

【解決手段】本発明による半導体集積回路は、端子110の機能が変更可能なポート回路部100と、端子110からの入力信号DINのエッジを検出するエッジ検出回路部200とを具備する。端子110の機能の変更時刻を基準とした所定の期間T、エッジ検出回路部200におけるエッジ検出動作は無効となる。

(もっと読む)

半導体集積回路

【課題】回路規模を増大させることなく、高速テストを実施することが可能な半導体集積回路を提供する。

【解決手段】本発明にかかる半導体集積回路は、複数のメモリセルによって構成されるメモリセル部22と、メモリセルへのデータの書き込み及び読み出しを制御する制御部と、クロックCLKに応じて制御部へ入力されるパルス信号を生成するパルス信号生成部と、を備える。そして、パルス信号生成部は、ワンショットパルス生成回路20を有する。ワンショットパルス生成回路20は、通常動作モード時には、クロックCLKに同期したワンショットパルス信号をパルス信号として生成し、高速動作モード時には、クロックCLK及びパルス信号に同期した連続したワンショットパルス信号をパルス信号として生成する。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

半導体集積デバイス

【課題】動作中に動作モードの設定の変更が可能であり、モード設定のための専用の端子を必要としない半導体集積デバイスを提供する。

【解決手段】動作タイミングを制御するためのクロック信号を入出力するワードクロック線101a、ビットクロック線101bと、クロック信号に基づいて動作することによって処理する原因を示すデータ、またはクロック信号に基づいて動作することによって処理された結果を示すデータを間欠的に入出力するデータ線101cと、データ線101cからデータが出力されない期間、データ線101cから信号を取得するフリップフロップ回路102と、フリップフロップ回路102によってサンプリングされた信号によって自デバイスの動作モードを設定するモード設定回路103によって半導体集積デバイスを構成する。

(もっと読む)

位相比較装置

【課題】高速動作するBang-Bang型位相比較回路の出力パルスに歪や欠損がある場合であっても、チャージポンプやA/D変換器を用いることなく、進相、遅相のいずれであるかを正確に表すデジタル信号を得る。

【解決手段】Bang-Bang型の位相比較回路10と、該位相比較回路の進相出力パルスおよび遅相出力パルスを入力して遅相/進相の識別を行う位相比較結果識別回路20とを備える。位相比較結果識別回路20は、位相比較回路10の進相出力パルスによってリセットされた後にクロック信号のカウントを行い所定のカウント値に達すると遅相を示す信号を出力する第1カウンタ回路21と、位相比較回路10の遅相出力パルスによってリセットされた後に前記クロック信号のカウントを行い所定のカウント値に達すると進相を示す信号を出力する第2カウンタ回路22と、前記遅相を示す信号と前記進相を示す信号を入力して進相/遅相の識別信号を出力する識別回路23とを具備する。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を

提供する。

【解決手段】パルス発生装置100を、CLK信号の入力に応じて起動開始信号D0と、

D0を反転したXD0とを出力する起動開始信号生成回路20と、起動開始信号の入力に

応じてパルス信号を発生する、各々の信号出力部が独立した第1〜第Nのパルス発生回路

21_1〜21_Nと、第1〜第Nのパルス発生回路21_1〜21_Nのうちパルス信

号を出力する予定の一部の回路の信号出力部を順次選択して、該選択した信号出力部を共

通の信号出力線に接続し、残りのパルス発生回路の信号出力部を共通の信号出力線から電

気的に切断する選択回路22とを含む構成とした。

(もっと読む)

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

デューティ補正回路

【課題】伝送速度が異なる複数のマンチェスタ符号化信号のデューティ比を補正可能なデューティ補正回路を得ること。

【解決手段】本発明にかかるデューティ補正回路は、マンチェスタ符号化された受信信号の連続する2つの立上りエッジの間隔または立下りエッジの間隔に基づいて受信信号の伝送速度を判定するシンボル周期判定回路7と、受信信号の“Hレベル”または“Lレベル”の継続時間を観測するエッジ検出回路2およびカウンタ3と、観測結果および判定結果に基づいて波形歪みを検出する波形歪み検出回路4と、波形歪みが検出された場合に波形歪み発生期間、受信信号を反転することにより波形の補正を行うセレクタ5と、を備えることとした。

(もっと読む)

パルス入力装置

【課題】入力信号の周波数に応じて最適な精度と応答時間を得ることができるパルス入力装置を実現する。

【解決手段】入力信号をパルス信号として検出し、パルス信号の周波数を上位システムへ通知するパルス入力装置に関する。パルス信号の立ち上がりエッジ又は立ち下がりエッジのエッジタイミングでパルス信号のパルス数を所定時間の間カウントし、エッジカウント値として保持するエッジカウント手段と、エッジタイミングで、前回のエッジタイミングとの間隔時間を測定するとともに、所定時間の間の間隔時間を積算し、エッジ間隔値として保持するエッジ間隔測定手段と、エッジカウント値をエッジ間隔値で除してパルス信号の周波数を算出する周波数算出手段とを設けた。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

クロックエッジ復元を有するパルスカウンタ

特定の時間間隔の間に入力パルスをカウントするための装置および方法が提供される。クロックエッジ復元出力信号は、入力ゲート信号および入力パルスを含むクロック信号に応答して生成される。クロックエッジ復元出力信号は、入力ゲート信号がイネーブル状態にある間および入力ゲート信号がイネーブル状態からディスエーブル状態に遷移するときに生じる、クロック信号の入力パルスの、立ち上がりまたは立ち下がりのいずれかのそれぞれに対して、それぞれ完全なクロックパルスを有する。カウンタ回路は、クロックエッジ復元出力信号に含まれるパルスをカウントする。  (もっと読む)

(もっと読む)

同期カウンタ回路およびセンサ制御装置ならびに同装置における位相差検出方法

【課題】レゾルバやロータリエンコーダ等、センサ検出信号に本来含まれる位相差の同期回路による消失を防止して高精度化をはかる。

【解決手段】クロックに同期してカウントデータを出力する同期カウンタ回路であって、被測定信号の立ち上がりエッジがクロックの任意のタイミングを基準に前に位置するか後ろに位置するかを判別し、当該判別結果をカウントデータに付加して出力するカウントデータ生成手段(1、2)を設ける。

(もっと読む)

クロック発生回路

【課題】基準クロックと分周クロックとの伝送路におけるチップ内ばらつきによるスキューを抑制し、タイミング収束性を改善したクロック発生回路を実現する。

【解決手段】クロック発生回路は、第1の回路10と、第2の回路20Aと、第3の回路50Aとを備えている。第1の回路10は、第1のクロック信号s10を生成する。第2の回路20Aは、前記第1のクロック信号s10を分周して、第2のクロック信号s20を生成する。第3の回路50Aは、前記第1及び第2のクロック信号s10,s20から、前記第2のクロック信号s20の周期を有し、かつ第1の論理レベルから第2の論理レベルへの変化のタイミングが前記第1のクロック信号s10の当該タイミングと同じである第3のクロック信号s50を生成する。

(もっと読む)

分周回路

【課題】グリッチの発生を抑制することのできる分周回路を提供すること。

【解決手段】分周回路2aの第1カウンタ21は基準クロック信号ICKの立ち上がりエッジに同期動作して基準クロック信号ICKを分周した第1分周信号RCKを出力する。第2カウンタ22は基準クロック信号ICKの立ち下がりエッジに同期動作して基準クロック信号ICKを分周した第2分周信号FCKを出力する。第1カウンタ21は、第2イネーブル信号生成回路24により生成された第1イネーブル信号RENに応答してカウント動作を実行・停止し、第2カウンタ22は、第1イネーブル信号生成回路23により生成された第2イネーブル信号FENに応答してカウント動作を実行・停止する。出力回路25は、第1分周信号RCKと第2分周信号FCKを合成して分周クロック信号DCKを生成する。

(もっと読む)

レジスタ回路、レジスタ回路を含む同期式集積回路

【課題】従来のゲーティッドセルを用いたクロックゲーティングに比べて、制御信号enが伝播されるレジスタ間のパス遅延を縮小することができるレジスタ回路を提供する。

【解決手段】通過許可回路101fは、レジスタ1に入力される制御信号enがアクティブ状態から非アクティブ状態となることで、クロック信号clkの信号状態によらず、通過許可回路101fに入力されたデータ信号Qを、後段の保持回路101gに通過させず、保持回路101gは、レジスタ1に入力される制御信号enがアクティブ状態から非アクティブ状態になることで、クロック信号clkの信号状態によらずに、通過許可回路101fを通過したデータ信号Qをラッチするので、ゲーティッドセルを用いずにクロックゲーティングを行うことができ、ゲーティッドセルの遅延時間分、パス遅延を縮小することができる。

(もっと読む)

1 - 18 / 18

[ Back to top ]