Fターム[5J039AC03]の内容

Fターム[5J039AC03]に分類される特許

1 - 20 / 22

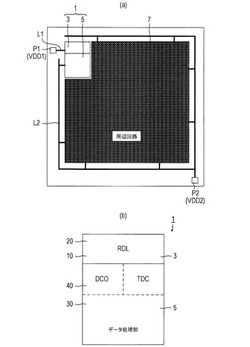

半導体集積回路

【課題】半導体集積回路に搭載されたデジタル制御発振装置が生成するクロック信号の品質を向上させる。

【解決手段】ICチップは周辺部を除く部位に位置する回路形成部位が、パルス遅延回路10からなる第1回路ブロック3と、時間/数値変換回路20及びデータ処理部30,デジタル制御発振回路40からなる第2回路ブロック5と、第1回路ブロック3及び第2回路ブロック5により形成されるデジタル制御発振装置1にて生成されたクロック信号CKOを利用した各種処理を実行するための周辺回路等からなる第3回路ブロック7とからなる。また、第1回路ブロック3は、電源パッドP1及び電源ラインL1を介して供給される第1の電源VDD1により駆動され、第2回路ブロック5及び第3回路ブロック7は、電源パッドP2及び電源ラインL2を介して供給される第2の電源VDD2により駆動されるように、レイアウトされている。

(もっと読む)

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

受信装置

【課題】衛星から受信した信号の精度を早期に推定する技術を提供する。

【解決手段】アンテナ10は、少なくともひとつの衛星から送信された信号を受信する。周波数弁別部28は、受信した信号において発生しうるドップラーシフトの範囲にわたって周波数が変化するローカル信号を発生する。周波数弁別部28は、ローカル信号によって、受信した信号を周波数変換する。周波数弁別部28は、周波数変換した信号をエンベロープ検波する。周波数弁別部28は、エンベロープ検波した信号をしきい値と比較する。CPU20は、比較の結果、しきい値以上の値になっている信号成分の数を計数することによって、受信した信号の送信元になる衛星の数を推定する。

(もっと読む)

周波数逓倍遅延ロックループ

【課題】周波数逓倍回路を提供する。

【解決手段】周波数逓倍回路(100)は、遅延ラインとクロック合成回路(TOG)を備える。遅延ラインは、その一端でリファレンスクロック(102)を受けて、一周期に一致した複数の遅延素子(101)からクロックタップ出力を発生させる。クロック合成回路(TOG)は、一対のタップ出力に応答して、各タップ出力から出力クロックパルスの立ち上がり及び立ち下がりエッジを発生させる。出力クロックの周期は入力クロックの周期よりも短い。遅延ラインは、遅延素子(101)の周期に一致するように遅延ロックループに含まれてもよい。所定数の遅延段タップ出力に接続された入力を有し、相補出力を供給する、複数の合成回路セル(TOG)が設けられる。セレクタ(106)は、位相検出器(112)からの選択制御信号に応答して、合成セルの1つに係る一対の相補出力のうちの一方から出力を選択する。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

周波数逓倍回路

【課題】インタフェースクロックまたは外部クロックの倍数である内部クロックを発生できる周波数逓倍回路を提供する。

【解決手段】遅延ラインは、リファレンスクロックの一周期に一致するように設けられた複数の遅延素子を備え、リファレンスクロックを一端で受けて、遅延素子のそれぞれから遅延段タップ出力を発生する。複数のクロック合成回路は、それぞれ対になった複数のタップ出力に応答して、対のそれぞれから出力クロックパルスの立ち上がりエッジおよび立ち下がりエッジを発生させ、このとき、出力クロックの周期は入力クロックの周期より短い。

(もっと読む)

信号逓倍器、信号生成器、光送信器および光通信装置

【課題】回路の製造ばらつきや経時変動があっても、クロック信号のデューティ比を精度よく制御すること。

【解決手段】入力部11には、連続して電圧が変化するクロック信号が入力される。供給部12は、一定の参照電圧を供給する。セレクタ13は、入力部11から入力されたクロック信号の電圧が、供給部12によって供給される参照電圧を跨ぐごとに電圧を交互に切り替えたクロック信号を出力する。演算回路14は、入力部11から入力されたクロック信号と、セレクタ13から出力されたクロック信号と、の排他的論理和を出力する。

(もっと読む)

位相クロック発生器

【課題】より少ない数のトランジスターを使いながらも、高周波特性が反映されたクロック信号を生成でき、具現可能なクロック周波数帯域に限界がない位相クロック発生器を提供することと、回路サイズ及び電力消費量を最小化して、半導体設計及び工程が容易になり、トランジスターの動作周波数がそのまま反映された高周波クロック信号を生成することができ、ノイズ成分の影響を最小化することができる位相クロック発生器を提供する。

【解決手段】電源線及び接地線の間に繋がって4行とN列を構成して、多数の位相遅延信号をゲート端子を通じて入力されるトランジスターを含み、単位列を構成する4個のトランジスターの中で、一方の側の2個のトランジスターはNMOSでペアを構成し、他方の側の2個のトランジスターはPMOSでペアを構成して、前記単位列を構成するNMOSペアとPMOSペアの間のラインに繋がってクロック信号を送り出すバッファーを含む。

(もっと読む)

周波数逓倍回路および送信装置

【課題】 本発明は、電子機器において所望のクロック信号を2逓倍する周波数逓倍回路と、その周波数逓倍回路によって生成された2逓倍クロック信号に同期して伝送情報のCMI符号化を行う送信装置とに関し、物理的なサイズが小さく、かつ安価に精度よく2逓倍クロック信号が生成されることを目的とする。

【解決手段】 クロック信号の周期Tの半分に相当する遅延d(=T/2)を前記クロック信号に与え、遅延クロック信号を生成する遅延手段と、前記クロック信号と前記遅延クロック信号との双方の前縁または後縁に同期し、パルス幅が前記周期Tの四分の一であるパルス信号の列を生成するパルス幅調整手段とを備えて構成される。

(もっと読む)

パルス発生回路およびこの回路を用いた電子装置、携帯電話機、パーソナルコンピュータ、ならびに、この回路を用いる情報伝送方法

【課題】簡単な回路で低消費電力にて高周波数帯域のパルスを容易に発生することがで

き、しかも高価な半導体プロセスを使うことなく実現することができるパルス発生回路を

提供すること。

【解決手段】パルス発生回路を、所定段数縦続接続されたインバータ回路101〜109と、これらインバータ回路101〜109にあって1つのインバータ回路の入出力側に

1段置きに接続され、この接続された各段のインバータ回路102,104,106,108の遅延量に相当する時間幅のパルスを発生する複数のNAND回路110〜113と、

これらNAND回路110〜113の出力の論理和を取るNOR回路114とを備えて構

成する。

(もっと読む)

クロック発生装置

【課題】遅延回路により、1/2N(Nは正の整数)周期遅延させたN個のクロックの排他的論理和をとることでN逓倍クロックを発生する従来技術では、プロセスのバラツキにより遅延回路の遅延値が変動し、N逓倍クロックのジッタやデューティ劣化するなどの問題があった。

【解決手段】本発明では外部よりあらかじめ1/2N(Nは正の整数)周期遅延させた信号を入力することで、半導体製造プロセスのバラツキによる遅延回路の遅延変動は発生しない。したがって、排他的論理和により生成されるN逓倍クロックはジッタやデューティ劣化を低減でき、高精度なN逓倍クロックを生成できる。また、N逓倍クロックを半導体集積回路の外部に出力し、周波数のバラツキやデューティ劣化量を計算し、入力信号の入力タイミング及びデューティを調整することで高精度なN逓倍クロックを供給する。

(もっと読む)

発振回路

【課題】 実装面積を増大させることなく正確なクロック逓倍出力を得ることができる逓倍出力を有する発振回路を提供する。

【解決手段】 発振回路5は、少なくとも奇数段のインバータ11mを備えるリングオシレータ10と、リングオシレータ10の少なくとも2つの段のインバータ11mと11fから取り出した2つの信号の排他的論理和を逓倍出力として出力する周波数逓倍部20とを備える

(もっと読む)

半導体集積回路装置

【課題】 簡単な構成で高逓倍能力を持ち、高速応答を実現したクロック生成回路を備えた半導体集積回路装置を提供する。

【解決手段】 遅延回路の各段遅延信号をゲート手段で選択し初段側に帰還してリングオシレータを構成する。デコーダにより1つのゲート手段の選択信号を形成して上記ゲート手段を制御する。基準周波数信号の1周期間での上記リングオシレータの発振出力のカウンタ出力とX倍指定値との比較結果により第1レジスタで上記デコーダの入力信号を形成する。第1動作モードで上記制御回路の代表比較結果に対応してバイナリスキャンにより上記入力信号を形成する。第2動作モードでは、上記比較結果により上記入力信号に対して+1又は−1とする。

(もっと読む)

半導体集積回路

【課題】 待機モードから通常モードに速やかに復帰することができる半導体集積回路における上記待機モードでの消費電力の低減を図る。

【解決手段】 自走モードと逓倍モードとを備えたクロック生成回路(10)と、上記クロック生成回路によって生成されたクロック信号に同期動作可能な内部回路(40)と、基準クロック信号を生成する発振回路(30)と、通常モードと待機モードとの切り換えを制御可能な動作モード制御回路(20)とを設ける。上記発振回路の発振動作が安定する前に上記自走モードによるクロック信号が生成されることにより、これに同期して内部回路が通常モードで動作することができ、待機モードから通常モードへの復帰時間が短縮される。そして上記待機モードにおいては、上記発振回路の上記発振動作が停止されることで消費電力が低減される。

(もっと読む)

周波数逓倍器

周波数逓倍器を開示する。複数の電圧調整器のそれぞれが、電圧制御遅延線から得た1つの入力信号に応じて、第1および第2共通ノードでの電圧レベルを調整する。入力バッファは、フィードバック信号に応じて第1ノードを充電または第2ノードを放電する。出力バッファは、出力ノードでの電圧のレベルを調整し、周波数が逓倍されたクロック信号と出力ノードの電圧レベルに対応したフィードバック信号とを出力する。放電回路は、電圧制御遅延線の各入力信号の立ち上がりエッジが入力される前に、第1ノードを放電する。充電回路は、電圧制御遅延線からの各入力信号の立ち上がりエッジが入力される前に、第2ノードを充電する。  (もっと読む)

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

1 - 20 / 22

[ Back to top ]