Fターム[5J039EE24]の内容

Fターム[5J039EE24]の下位に属するFターム

90度の位相差を持つもの (16)

Fターム[5J039EE24]に分類される特許

1 - 20 / 54

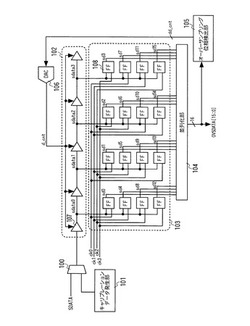

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

半導体装置、電子機器、及び出力波形歪み改善方法

【課題】N本のクロック信号を出力した際に生ずる出力波形歪みを改善した装置構成を提供する。

【解決手段】半導体装置は、所定周波数の入力クロック信号CLK−Iを入力して同一周波数の複数のクロック信号CLK1からCLKNを出力する。前記入力クロック信号は遅延部1_1から遅延部1_N−1により所定の遅延時間差を与えられ、前記複数のクロック信号として出力される。前記複数のクロック信号の立ち上がり及び立ち下がりを分散することで、共通の電源レギュレータ11への負荷が低減する。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

信号処理装置および試験装置

【課題】制御チップに占める制御回路の面積を低減し、且つ、制御信号を出力する出力部の数を低減しつつ、複数の命令信号の処理時間の増大を抑制する。

【解決手段】複数チャネルの被制御回路を制御する制御信号を生成する信号処理装置であって、それぞれの被制御回路に対する命令信号を共通の入力部で受け取り、受け取った命令信号に応じて制御信号を生成し、それぞれの被制御回路への制御信号を共通の出力部から出力する制御チップと、制御チップが出力するそれぞれの制御信号を、対応する被制御回路に分配する分配回路とを備える信号処理装置を提供する。

(もっと読む)

半導体設計装置

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

多相クロック生成装置

【課題】回路の規模を増大させることなく多相クロック信号を生成できる多相クロック生成装置を提供する。

【解決手段】、多相クロック生成装置1では、基準となるクロック信号のうち選択回路4にて2つが選択され、この2つのクロック信号のうち多相クロック生成部5a〜5cにて何れか一つを選択されると共に、選択された2つのクロック信号の中間位相を有するクロック信号が生成されて出力され、このクロック信号の何れか一つのクロック信号が位相選択部6dにて選択されることで所定の位相の出力クロック信号が生成されている。このように、簡易な構成で多相の出力クロック信号を生成することができる。そのため、多段的に並列に位相混合器を接続する従来の構成に比べて、回路の規模の増大を抑制できる。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

クロック供給システム及び画像形成装置

【課題】SSCGの変調度を大きくすることなく、且つ低コストで、複数の電子部品から放射されるノイズを効果的に低減する。

【解決手段】一定周波数の第1クロック信号を生成する第1クロック生成器と、前記第1クロック信号の周波数変調を行うことで周期的に周波数が変動する第2クロック信号を生成する第2クロック生成器と、複数のクロック供給対象回路で使用される前記第2クロック信号の位相が、前記クロック供給対象回路毎に異なるように位相調整を行う位相調整回路とによってクロック供給システムを構成する。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

スキャナー、電気光学パネル、電気光学表示装置及び電子機器

【課題】双方向転送機能を有したスキャナーで信号数を削減するとともに出力電位を安定化させる。

【解決手段】同一導電型のトランジスターで構成された複数の単位回路510からなる双方向転送可能なスキャナーであって、前記スキャナーを構成する前記単位回路510は、外部から与えられる信号を選択的に出力端子に出力する出力トランジスターを有し、前記出力トランジスターのゲート電極は第1の方向スイッチを介して他の単位回路510の出力端子である第1の端子に電気的に接続され、前記出力トランジスターのゲート電極は第2の方向スイッチを介してさらに他の単位回路510の出力端子である第2の端子にも電気的に接続される。

(もっと読む)

1 - 20 / 54

[ Back to top ]