Fターム[5J042CA02]の内容

Fターム[5J042CA02]に分類される特許

1 - 15 / 15

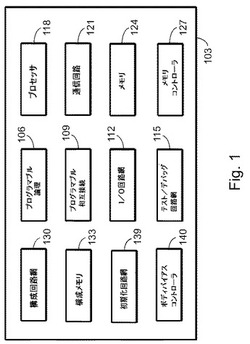

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

プログラマブルロジックデバイス

【課題】ロジックブロックユニットの演算構成と接続を高速に変更可能なプログラマブルロジックデバイスを提供する。

【解決手段】コンフィグレーションコントロール回路(213)は、第1のコンフィグレーション情報に応じてロジックブロックユニット(210)の演算構成と接続を制御する。データコントロール回路(211)は、第1の入力データストリームをロジックブロックユニットに出力し、ロジックブロックユニットは、第1の入力データストリームの論理演算結果を出力する。コンフィグレーションコントロール回路は、データコントロール回路が第1の入力データストリームをロジックブロックユニットに出力している間に、第2のコンフィグレーション情報を入力して記憶し、ロジックブロックユニットが第1の入力データストリームの論理演算を終了すると、第2のコンフィグレーション情報に応じてロジックブロックユニットの演算構成と接続を制御する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

再構成可能な論理装置

【課題】再構成可能な論理装置を提供する。

【解決手段】第1論理ブロックと、第2論理ブロックとを含む少なくとも2つの論理ブロック;第1論理ブロックに連結される複数の第1グローバル配線と、前記第2論理ブロックに連結される複数の第2グローバル配線と、を含むグローバル配線グループ;複数の第1グローバル配線と、複数の第2グローバル配線とが交差する領域にそれぞれ配される複数の第1不揮発性メモリ素子を含み、論理装置の動作をリアルタイムで再構成するために、複数の第1不揮発性メモリ素子それぞれに保存された第1データを基に、複数の第1グローバル配線及び第2グローバル配線のルーティングを制御するグローバル制御部;を含む再構成可能な論理装置である。

(もっと読む)

ルックアップテーブル、半導体集積回路、ルックアップテーブルの製造方法、および半導体集積回路の製造方法

【課題】製造が容易で集積度が高く動作の速い低廉なルックアップテーブルを短期間で開発すること。

【解決手段】

ルックアップテーブル200は、入力端子101と、出力端子102と、入力端子101の個数により決定される入力パターン数に対応したビア挿入箇所と、トランジスタにより構成される選択回路と、プリチャージ回路とを備える。ビア挿入箇所は、単一のビア層が有している。ビア挿入箇所の中から組合せ回路に応じてビアが挿入され、挿入されたビアを介して入力端子101と出力端子102とが接続される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応している場合、出力端子102にはVSSが出力される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応していない場合、出力端子102にはプリチャージ回路によりVDDが出力される。

(もっと読む)

スイッチング信号を出力するための安全回路

本発明は、負荷(LA)への給電の遮断を制御するための電流回路を安全目的で遮断するための少なくとも1つのスイッチ(TRA,TRB)に対してスイッチング信号を出力するための安全回路に関する。この安全回路は、少なくとも1つのスイッチ(TRA,TRB)に対して各出力端(OUTA1,OUTB1;OUTA2,OUTB2)でそれぞれ不確実な駆動制御信号を出力する少なくとも1つの評価回路(μCA,μCB)を有する。さらに、当該安全回路はプログラマブル論理回路(PL)を有し、前記駆動制御信号は該プログラマブル論理回路(PL)の各入力端(INA1,INB1;INA2,INB2)へ供給され、該プログラマブル論理回路(PL)は前記少なくとも1つのスイッチ(TRA,TRB)を確実な駆動制御信号によって駆動制御するために、前記少なくとも1つのスイッチ(TRA,TRB)に接続されている。前記プログラマブル論理回路は、動作中に各スイッチ(TRA,TRB)が障害無しで動作しているか否かをテストおよび検査するテスト監視装置として構成されている。最後に本発明では、前記少なくとも1つのスイッチ(TRA,TRB)の、電位に接続された確実な第1の端子(OUT(P),OUT(M))を有し、該第1の端子の電位状態を監視するため、該第1の端子(OUT(P),OUT(M))は前記プログラマブル論理回路(PL)の各フィードバック入力端(FBA,FBBに接続されている。動作に障害が無い場合、前記第1の端子の電位状態は、前記少なくとも1つのスイッチ(TRA,TRB)の確実な信号に相応する。  (もっと読む)

(もっと読む)

プログラマブルゲートアレイ並びにそのようなアレイの相互接続スイッチ及び論理ユニット

複数の入力部(I,I’)を一つのグループとする入力ポート及び複数の出力部(O,O’)を一つのグループとする出力ポートを有する、プログラマブルゲートアレイ用の相互接続スイッチ(2)であって、入力部及び出力部は、入力部から出力部に下る連結3構造に接続され、連結3構造は、単一経路によって全ての入力ポートの各入力部を各出力ポートの少なくとも一つの出力部に接続するために複数のレベルで構成されたルーティング素子(4,5,6)を備える。相互接続スイッチ、論理ユニット及びこれらの二つを有するプログラマブルゲートアレイは、ネットワークの二つのポイント間の単一経路を確立するために配置される。 (もっと読む)

論理モジュール

【課題】 論理モジュールを汎用化し、検証対象論理の回路構成に容易に合わせることができ、検証対象論理をプログラム可能な複数の論理素子にプログラムする工数と作成費用を大幅に低減することができる論理モジュールを提供する。

【解決手段】 本論理モジュールは、FPGA101,102と、外部と接続するためのソケットコネクタ105およびヘッダコネクタ106と、FPGA101,102およびコネクタ105,106に配線で接続された接続切替回路103とを基板に備える。FPGA101とコネクタ105とは配線で接続される。接続切替回路103は、FPGA101とFPGA102との接続およびコネクタ105とコネクタ106との接続を行う第1の接続と、FPGA101とコネクタ106との接続およびFPGA102とコネクタ105との接続を行う第2の接続とを切替可能とされる。

(もっと読む)

論理検証システム基板

【課題】複数論理のアーリープロトタイピング検証を、同一のシステム基板で高速に実行することのできる技術を提供する。

【解決手段】FETスイッチ903を使用し、高速な配線経路切り替えを実現するとともに、そのオン/オフ制御をプログラマブルスイッチ(FPGA等)902で行うことで、論理分割、FPGA間配線処理時に、FPGA901にプログラムされるターゲット論理に合わせてFETスイッチ903の制御を決定する。

(もっと読む)

プログラマブルゲートアレイ装置及び回路切替方法

【課題】ゲートアレイ内部の記憶素子の数を必要最小限に抑えつつ、コンテクストデータを切り替えるための時間を大幅に短縮することができるゲートアレイ装置を提供する。

【解決手段】各マクロセルに、実行中のロジック/状態データを記憶するための第1の記憶素子群の他に、第1の記憶素子群に対応する第2の記憶素子群を設ける。第2の記憶素子群を直列に接続して、第2の記憶素子群に他の回路のロジック/状態データをロードしておき、第1の記憶素子群に記憶されているロジック/状態データと、第2の記憶素子群に記憶されている他の回路のロジック/状態データとを交換するときには、第2の記憶素子群と第1の記憶素子群との間で、対応する2つの記憶素子同士を接続し、その後、交換実行信号が入力されて、第2の記憶素子群は第1の記憶素子群に記憶されているロジック/状態データを記憶し、第1の記憶素子群は第2の記憶素子群に記憶されている他の回路のロジック/状態データを記憶する。

(もっと読む)

製造中止部品対応用変換アダプタ

【課題】 製造中止部品毎に互換部品の選定や代替部品の設計・製作を実施することなく効率的に代替部品を供給することが可能な製造中止部品対応用変換アダプタを得る。

【解決手段】 ユーザが自由に回路構築できるFPGA(Field Programmable Gate Array)等のプログラマブル素子12を互換部品として搭載した変換アダプタにおいて、変換アダプタのプログラマブル素子に予め複数の製造中止部品と同一の機能ロジックを書き込んでおき、既存の基板上の電子部品が製造中止等により入手不可となった場合に変換アダプタのプログラマブル素子にて製造中止部品の機能をエミュレートすることにより代替部品として使用する。

(もっと読む)

出力回路

【課題】 オンラインダウンロード機能を備える出力部の2つの入力端子の電圧が互いに相関がない電圧で決定されるので、起動時の突入電流が大きい。この突入電流を小さくするために定常状態での出力部の電圧を0Vにしていたが、過渡的にマイナス電位になるために寄生トランジスタをオンしてしまうという課題を解決する。

【解決手段】 ダウンロード切替デジタル信号でスイッチをオン・オフして一端が基準電位に接続された時定数回路内のコンデンサを充放電する時定数回路の出力を出力部の一方の入力端子に入力して、出力部の他方の入力端子に前記基準電位を印加するようにした。出力部の入力誤差が小さくなるので、これによる過大な突入電流が流れることはない。そのため、定常状態における出力部の電圧を自由に選ぶことができるので、寄生トランジスタをオンさせることもなくなる。

(もっと読む)

多用途電子機器システム

【課題】 故障箇所を特定するための信号線の配線を簡易にして回路規模を小さくし、モジュールの再構築を容易にして、稼働率を向上させることができる多用途電子機器システムを提供する。

【解決手段】 モジュール2内の機能実行部を信号線で連結すると共に、モジュール2間の機能実行部を横断的に連結して全ての機能実行部をマトリクス状に信号線で接続し、当該マトリクス状の信号線をホスト1が監視することで、信号線の配置を複雑にすることなく、故障部位を検出し、更に代替可能な機能実行部を表示することでモジュール構成の再構築を容易に実現できるとする多用途電子機器システムである。

(もっと読む)

縦列アーキテクチャ

複数の列に配列される回路を有する集積回路(IC)が開示される。ICの列は、ICの第1の端部から第2の端部へ延在する、同じ種類の実質的に一連の位置合せされた回路素子である。加えて、異なるタイプの回路素子を有する中央列があり得る。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]