Fターム[5J043DD13]の内容

Fターム[5J043DD13]に分類される特許

1 - 17 / 17

発振回路

【課題】共振部とインバータを並列接続する発振回路では、インバータのトランスコンダクタンスが発振周波数に拘わらず一定なので、スプリアスへの収束を回避することが難しい。本発明はスプリアスへの収束を回避できる発振回路を提供することを目的にする。

【解決手段】インバータの入力信号の遷移点(立ち上がり、立ち下がり)で一定幅のパルス信号を出力するワンショット回路を用い、このワンショット回路のパルス幅がインバータへの入力信号のパルス幅より大きいときに、インバータへの電源供給を停止するようにした。スプリアスではトランスコンダクタンスの時間平均が小さくなり、発振が持続しない。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

発振器

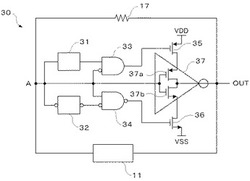

【課題】 本発明は、発振器が搭載される電子機器に応じた立ち上がり時間を有する出力信号を生成することができ、従って出力信号を高精度に生成することができる発振器を提供することを目的とする。

【解決手段】 発振部200から出力される中間出力信号に対して、それぞれ異なる波形整形を行う複数の波形整形回路500A〜500Cを有する波形整形部300と、複数の波形整形回路500A〜500Cの中から選択された波形整形回路500に対応するデータを記憶する記憶部400と、記憶部400に記憶されているデータに基づいて、波形整形部300が有する複数の波形整形回路500A〜500Cの中から選択された波形整形回路500によって、中間出力信号に対して波形整形を行わせる制御部450とを備える。

(もっと読む)

半導体集積回路

【課題】 振動子型発振回路の発振停止を確実に検出し、発振停止を検出した際には確実に発振回路を再起動できる半導体集積回路を提供すること。

【解決手段】 半導体集積回路は、振動子によりメインクロック信号を生成する一つ以上のメイン発振回路と、メイン発振回路と独立し常に動作するリング発振器と、リング発振器の出力クロック信号を基準にメインクロック信号を監視してメイン発振回路の動作状態を判断するメインクロック検知回路と、メインクロック検知回路の検知結果に応じて、メイン発振回路を構成する素子の組み合せを変更する素子構成変更回路とを備える。

(もっと読む)

発振回路

【課題】温度補償回路に発振部の出力がノイズとして入力しない発振回路を提供する。

【課題の解決手段】周囲温度に応じた制御信号によって出力周波数が制御される発振部1と、この発振部1に制御信号を供給する温度補償回路2と、発振部1の発振出力と温度補償回路2の温度センサ出力のいずれかを出力するようオンオフ制御される出力バッファ4と温度センサ出力スイッチ3からなる切換スイッチ回路とを備え、温度センサ出力スイッチ3は、トランスファーゲートスイッチ301,302を2段直列に接続し、この接続点に固定電位に接続した第3のスイッチ303を介在させてなり、発振出力を出力する時はトランスファーゲートスイッチ301,302をオフとして、第3のスイッチ303をオンとし、温度センサ出力を出力する時はトランスファーゲートスイッチ301,302をオンとして、第3のスイッチ303をオフとする。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

クロック信号生成装置

【課題】消費電流を低減すると共にクロック信号を早期に安定出力することができるクロック信号生成装置を提供する。

【解決手段】クロック信号生成装置は、水晶発振子からの発振信号を定電流値に応じて増幅して得られた増幅発振信号の振幅が閾値振幅を超過したと判別した場合に当該増幅発振信号に基づいてクロック信号を生成し、該クロック信号のクロックパルス総数が所定のパルス数を超過したと判別した場合に該定電流値を低減する。

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

半導体集積回路およびそれを備えた電子機器

【課題】発振信号を安定して生成することが可能な半導体集積回路およびそれを備えた電子機器を提供する。

【解決手段】半導体集積回路101は、発振信号を出力する発振回路1と、発振回路1から受けた発振信号を外部へ出力するか否かを切り替える切り替え回路2とを備える。

(もっと読む)

発振安定化検出回路

【課題】発振信号の安定化時間が短い発振安定化検出回路を提供する。

【解決手段】本発明の発振安定化検出回路は、水晶振動子の発振により生成されたパルス形態の発振信号が印加されて、前記発振信号を分周して出力するTフリップフロップ50と、インバータ及びトランジスタを含み、前記Tフリップフロップから出力された信号をハイレベルから始まるパルス形態の信号に変換して出力するパルス制御部60と、前記パルス制御部から出力される信号により充電されるキャパシタと複数のトランジスタとを含み、バイアス電流の調節により前記キャパシタの充電時間を制御し、その充電時間が経過した後に前記発振信号の安定状態を表す安定信号をCPUに出力する発振安定化検出部70と、を含む。

(もっと読む)

発振回路およびその制御方法

【課題】増幅手段の駆動電力を連続制御し、発振起動時間の短縮や動作の安定性を確保しながら定常時の消費電力を効率的に低減することのできる発振回路およびその制御方法を提供する。

【解決手段】発振回路が駆動する負荷容量への充放電電流に応じて発振回路の駆動電力を制御することとしたため、発振起動時間や発振の安定性を犠牲にすることなく定常時の消費電力を効果的に低減することが出来る。また本発明を採用したシステムにおいては、環境の変動に応じて最適な電力を発振回路に与えることが可能となり、システム全体での省エネルギー化、電池の長寿命化が実現出来る。

(もっと読む)

水晶発振子のためのパルス整形回路

可変閾値の多段パルス整形回路を活用した、回路配置及び方法を用いて、水晶発振回路の信号出力をパルス整形する。パルス整形回路の各段は、ラッチの入力を駆動するシュミット・トリガを有し、該シュミット・トリガは水晶発振回路によって発生する歪んだパルスを拒否するために制御されるプログラム可能なトリップ・ポイントを有する。可変閾値の多段パルス整形回路は、例えば、ノイズおよび他の環境効果に対して強い電子回路のためのクロック信号の生成に用いることによって、電子回路におけるクロック関連のエラーの可能性を低減できる。  (もっと読む)

(もっと読む)

半導体装置及び発振周波数補正方法

【課題】 本発明は、半導体装置の動作時の発振周波数の変動要因に対応できるとともに、特定の通信機能や通信相手を必要とすることなく、RC発振回路の発振周波数の補正が可能な半導体装置を提供することを目的とする。

【解決手段】 半導体装置は、第1の周期で発振する第1の発振信号を出力するRC発振器と、RC発振器の出力に結合され第1の発振信号の第1の周期の長さを第2の周期を有する第2の発振信号に基づき計測し、その計測値を出力する計測回路と、計測回路の出力とRC発振器の出力とに結合され計測値に応じた数で該第1の発振信号を分周する補正回路を含むことを特徴とする。

(もっと読む)

差動出力圧電発振器および電子機器

【課題】 圧電発振回路と、この回路から出力されるクロック信号の分配回路とをパッケージに搭載した差動出力圧電発振器およびこの発振器を搭載した電子機器を提供する。

【解決手段】 差動出力圧電発振器10は、圧電発振回路と、前記圧電発振回路から出力される信号に基づいて差動信号を出力するバッファと、前記バッファに接続し、前記差動信号を伝送する一対の伝送線路24と、前記各伝送線路24上に電気的に接続し、いずれか一方の前記伝送線路を跨いで前記伝送線路24の側方に前記差動信号を引出す受動素子28と、前記受動素子28に接続し、前記受動素子28を介して引出された差動信号を伝送する分配伝送線路26とを備えた構成である。

(もっと読む)

近似n次関数発生装置及び温度補償水晶発振回路

対の入力端子に共通の1次の入力信号及び所定レベルの定レベル信号が個別に入力され、前記1次の入力信号に対して反転又は非反転信号を出力すると共に、出力信号を所定の最大値及び最小値で制限するリミッタ機能を有する複数6個の差動増幅器15A〜15Fと、前記6個の差動増幅器に前記定レベル信号を夫々供給する定レベル信号発生回路と、差動増幅器15A〜15Fの通電電流を制御するカレントミラー回路14と、各差動増幅器15A〜15Fの出力電流を加算する加算用抵抗16A,16Bとを有し、第6の差動増幅器15Fで、通電電流を大きくして抵抗値を大きくすることにより、入力信号に対してより急峻な傾きの高精度の5次関数成分の出力電流を得る。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]