Fターム[5J055AX49]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 簡素化、小型化 (492) | 集積回路化 (154) | プロセスの問題点(ばらつき等) (81) | 回路で補償 (38)

Fターム[5J055AX49]に分類される特許

1 - 20 / 38

電圧検出回路

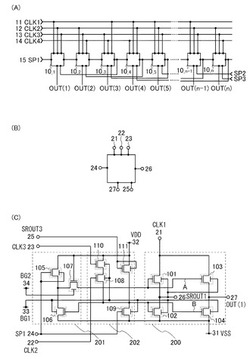

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

パワーオンリセット回路

【課題】面積の小さいパワーオンリセット回路を提供する。

【解決手段】電源端子と接地端子との間に設けられる容量及び電流源と、容量と電流源の接続点を入力端子に接続するインバータと、を備えたパワーオンリセット回路に、電源電圧の立ち上がりを検出すると、容量をディスチャージするディスチャージ回路を設けた。ディスチャージ回路は、容量と電流源を備えているが、この容量の容量値は小さくて良いので、パワーオンリセット回路の面積が小さくなる。

(もっと読む)

高周波用スイッチ回路

【課題】制御電圧以外の電源を用いることなく低消費電力かつ低コストで高性能に切り替え動作を行うことができる高周波用スイッチ回路を提供する。

【解決手段】第1および第2MOSFET回路11,21のゲート端子と第1および第2制御端子CT1,CT2との間に一端が接続され、他端がグランドGNDに接続されることにより、第1および第2制御端子CT1,CT2からグランドGNDへ向かう方向が順方向となるような少なくとも1つの整流素子D11,D12,D21,D22を含む第1および第2整流回路12,22と、第1および第2整流回路12,22の整流素子の少なくとも1つの順方向電流入力端子側と第1および第2MOSFET回路11,21の何れかの主端子側とが接続された接続部3とを備えている。

(もっと読む)

負荷制御装置

【課題】センサや制御回路等の動作用電力を安定に得られるとともに、不所望な電力損失をなくすとともに、小形化が可能な負荷制御装置を提供すること。

【解決手段】定電圧ダイオード15が導通していない期間、トランジスタ18はオフ、トランジスタ20がオンとなり、充電制御スイッチ13はオンしている。これにより、作動用電源部10は交流電源ACの出力により充電される。定電圧ダイオード15の導通電圧(所定電圧)に達すると、トランジスタ23はベースにバイアス信号を供給されてオンする。したがって、インバータ8の入力がロー、出力がハイになって、FET5がオンする。一方、トランジスタ18はオン、トランジスタ20がオフとなり、充電制御スイッチ13はオフする。

(もっと読む)

過電流検出装置

【課題】装置を大型化することなく且つ半導体スイッチの電圧のばらつきの影響を軽減して過電流を検出することが可能な過電流検出装置を提供する。

【解決手段】FET(T1)のドレインと、EEPROM12との間に、抵抗R1,R2の直列接続回路を含む分圧回路15を設ける。従って、EEPROM12には、FET(T1)のドレイン電圧V1を抵抗R1とR2で分圧した電圧が供給され、この電圧が判定電圧VMの嵩上げ電圧となる。その結果、FET(T1)のドレイン・ソース間電圧Vdsが大きく、判定電圧VMがEEPROM12の設定電圧の上限を超える場合であってもこの嵩上げ電圧が存在することにより、この電圧Vdsに応じた判定電圧VMを設定することができ、過電流の発生を高精度に検出することが可能となる。

(もっと読む)

負荷駆動回路

【課題】ユーザに対して異常が発生する前兆を事前に報知することができる負荷駆動回路を提供する。

【解決手段】検出回路14にて、過電流の発生やその前兆および他の異常の発生を検出し、温度上昇に基づいて過電流の発生やその前兆を検出したり、実際に半導体スイッチング素子12を通じて負荷3に流されている電流に基づいて過電流の発生やその前兆を検出すると共に、負荷3への電源電圧の印加の状態の異常、例えば負荷オープンと出力ON故障および出力OFF故障の発生を検出する。そして、過電流の前兆が検出されると、前兆ダイアグ回路18cにその旨を伝え、それに対応する前兆ダイアグ信号を発生させる。

(もっと読む)

電力供給制御回路

【課題】従来技術の電力供給制御回路は、回路規模が増大するという問題があった。

【解決手段】本発明にかかる電力供給制御回路は、負荷に対する電力の供給を制御する出力トランジスタ32と、外部入力信号に基づいて出力トランジスタ32のオンオフを制御するための制御信号a,bを生成するゲート駆動回路31と、出力トランジスタ32のゲート−ソース間に設けられ、出力トランジスタ32をオフする場合、制御信号a,bに基づいて出力トランジスタ32のゲート電荷を放電するためのトランジスタ37と、トランジスタ37よりも緩やかに放電するためのトランジスタ39と、トランジスタ37に直列に接続され、出力トランジスタ32をオフする場合において、出力トランジスタ32のゲート電圧が所定の電圧レベルに低下したことを検出し、出力トランジスタ32のゲート電荷の放電を遮断するダイオード40aと、を備える。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

出力回路、及びそれを用いた車載用通信システム

【課題】回路面積が小さく、製造バラツキによる出力特性の劣化を修正できる出力回路を提供することにある。

【解決手段】本発明による出力回路は、差動入力信号DIに応じた差動出力信号BP、BNを出力端子対31、32から出力するメインバッファ回路1と、制御信号CSに応じて出力端子対31、32のインピーダンスを調整するトリミング回路2とを具備する。トリミング回路2は、第1電源VDDと出力端子対31、32との間に、メインバッファ回路1内の第1トランジスタ対MP1、MP2及び第1抵抗対R1、R2に対して並列に接続された少なくとも1つの第2トランジスタ対MP11、MP21を備える。

(もっと読む)

シーケンス制御装置およびシーケンス制御方法

【課題】 スイッチを用いることなく、表示装置などの被制御装置に入力する信号のシーケンスを制御することができるシーケンス制御装置およびシーケンス制御方法を提供する。

【解決手段】 マイコン11は、時刻t1に、電源3に電圧を出力するように指示すると、電源3は、TFT制御IC12のVCC端子121に電圧を印加する。時刻t1から所定の時間が経過した時刻t21、たとえばTFT2の仕様で定められる時間が経過した時刻t21に、RESET端子122に入力するリセット信号を解除する。TFT制御IC12は、RESET端子122に入力されるリセット信号が解除されると、出力信号を生成するに必要な内部の回路の遅延時間の後、時刻t4に出力端子123に出力信号を出力する。出力端子123に出力された出力信号は、TFT2の入力端子に入力される。

(もっと読む)

スイッチ回路

【課題】少数の汎用入出力ポートを使用し同時に検出できるスイッチ数を増加させる。

【解決手段】基準充放電回路が基準抵抗RrefとコンデンサCにより構成される。被測定

充放電回路がスイッチS1−S6、抵抗R1−R6およびコンデンサCにより構成される。被測定充放電回路の合成抵抗値がスイッチの動作状態により一意に決まる。コンデンサCが放電された状態からGPIO0がハイレベルとされ、GPIO1およびCAPTimer

が入力状態とされる。コンデンサCの端子電圧がしきい値THを超えるまでの充電時間Trefが測定される。次に、コンデンサCが放電された状態からGPIO1がハイレベルと

され、GPIO0およびCAPTimerが入力状態とされる。しきい値THを使用して充電

時間Txが測定される。(Tx/Tref=Rx/Rref)の関係から合成抵抗値Rxが求められ、スイッチの動作状態が判別される。

(もっと読む)

高周波半導体スイッチ装置

【課題】チャージポンプの出力容量を低減してチップ面積を縮小できる高周波半導体スイッチ装置を提供する。

【解決手段】アンテナ端子ANTと、各高周波端子TX、RXとの間の接続を切り換える回路であって、アンテナ端子ANTと各高周波端子TX、RXとの間にそれぞれ接続されたスルーFETT1、T2を有する高周波スイッチ回路1と、各スルーFETT1、T2のゲートを駆動する駆動回路11、12と、駆動回路11、12の高電位電源端子に正側出力端子CP_out1が接続され、駆動回路11、12の低電位電源端子に負側出力端子CP_out2が接続された正負両極性チャージポンプ回路15と、を備え、各スルーFETT1、T2のゲート容量はそれぞれ概略等しく、正負両極性チャージポンプ回路15の正側出力端子CP_out1と負側出力端子CP_out2との間に容量Cxが設けられている。

(もっと読む)

FETスイッチ

【課題】1入力多出力スイッチおよび多入力1出力スイッチとして、広帯域化ならびに小型化・低コスト化が可能なFETスイッチを提供する。

【解決手段】第1の端子とn個(n:正整数、図1の場合n=4)の第2の端子との間の切替制御を行うSPnTスイッチとして、第1の端子と接続した配線210を分岐点Aにてn分岐した配線211〜214に、それぞれ、n個のFET41〜44のソースまたはドレインを接続し、n個のFET41〜44のドレインまたはソースには、それぞれ、配線221〜224を介して第2の端子を接続するとともに、少なくとも、配線211〜214を、それぞれ、直線で形成し、かつ、それぞれの長さを互いに等しくする。

(もっと読む)

ドライバ回路、及び電子回路装置

【課題】基準電流に対して所定の比の負荷電流を高い精度で得るドライバ回路を提供する。

【解決手段】MOSトランジスタM3のドレイン端子には二つの抵抗R1及びR2が接続されており、その他端には夫々電流発生装置IREF、負荷LOADが接続されている。両抵抗値は同値であるとする。またトランジスタM3のドレイン端子と両抵抗との接続部を接続点Aとする。この電子回路装置は抵抗R1と電流発生装置IREFとの接続部を接続点B、抵抗R2と負荷LOADとの接続部を接続点Cとして、夫々差動増幅器A1の入力端子へ接続したものである。該差動増幅器において、トランジスタM3のゲート端子に出力端子、つまり制御入力端子が接続されることを特徴とする。その接続部を接続点Gとする。該差動増幅器は接続点BおよびCの電位差を帰還する回路として機能する。

(もっと読む)

1 - 20 / 38

[ Back to top ]