Fターム[5J055BX03]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 切り換えスイッチ (661) | 複数接続の切り換え (528) | 多入力1出力(マルチプレクサ) (271)

Fターム[5J055BX03]に分類される特許

1 - 20 / 271

信号切替回路およびA/D変換装置

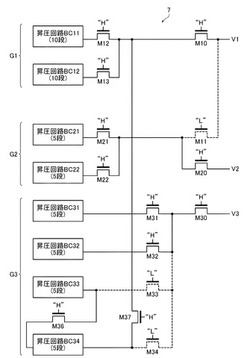

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

RFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器

【課題】スイッチング素子の個数を減らし、スイッチング素子を送受信時共有して、RFアンテナスイッチのサイズを減らすと共に、小型化及びワンチップ化にさらに応じるRFアンテナスイッチ回路、高周波アンテナ部品及び移動通信機器を提供する。

【解決手段】アンテナ1と、少なくとも一つの送信段2及び少なくとも一つの受信段3を備える複数の入出力段と、少なくとも一つの送信段2とアンテナ1側の共通ノード4、5との間の送信経路上に配置され、制御信号によって信号を伝達する少なくとも一つの送信スイッチブロック10と、受信段3と共通ノード4、5との間の受信経路上に配置され、制御信号によって伝達する少なくとも一つの受信スイッチブロック30、30a、30bと、スイッチング素子を共有して各々の送信及び受信動作と同期してオン動作する共用送受信スイッチブロック50とを含む。

(もっと読む)

半導体スイッチ回路

【課題】高いESD保護耐圧を確保しつつ、ESD保護素子の静電容量を極力小さくし、しかも、集積化の際における占有サイズを小さくする。

【解決手段】ESD保護回路103は、共通端子41とグランドとの間に設けられており、共通端子41側から順に、ESD保護スイッチ素子としての複数の直列接続された電界効果トランジスタ31−1〜31−4と、逆接続された一組のESD保護素子としてのダイオード32−1,32−2が直列接続されると共に、電界効果トランジスタ31−1〜31−4は、ゲートが相互に接続されてグランドに接続されており、ESD保護素子のダイオード32−1,32−2による静電容量を低減し、高いESD保護耐圧の確保が可能となっている。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

誤接続防止回路

【課題】屋外装置が一般の購入品である場合は屋内装置との接続正誤確認のために特別な加工を必要とする。

【解決手段】屋外装置17,18は送信装置または受信装置であって異なる電源入力条件を採り得る。屋外装置17,18とケーブルで接続された屋内装置16に設けられた誤接続防止回路1は、ケーブル接続の誤りを内部回路の切替えにより自動的に修正する。セレクタ1〜4は電源入力条件に適合するように屋外装置17,18への電源6,7および電源供給経路を選択し、セレクタ3,4は屋内装置16の中核部(不図示)との間の送受信と整合するように屋外装置17,18との信号接続経路を選択する。信号接続経路は電源供給経路の一部を形成する。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

スイッチおよびそのスイッチを用いたスイッチ回路

【課題】スイッチ用のトランジスタに発生する寄生ダイオードを介して内部に流入するESDによる負電流から内部回路を保護する。

【解決手段】第4nチャネルMOSFET(Mn4)は、ソース端子とバーグゲート端子間が接続されている。スイッチ素子は、第4nチャネルMOSFET(Mn4)のソース端子とグラウンド電位との間に接続され、第4nチャネルMOSFET(Mn4)のオフ時に第4nチャネルMOSFET(Mn4)のソース端子をグラウンド電位にする。保護回路40は、第4nチャネルMOSFET(Mn4)のソース端子と上記スイッチ素子の入力端子の接続点と、グラウンド電位との間に設けられ、静電気放電による第4nチャネルMOSFET(Mn4)のドレイン端子から流入する負電流をグラウンド電位に流す。

(もっと読む)

高周波スイッチモジュール

【課題】マルチバンドパワーアンプへ接続される小型の高周波スイッチモジュールを構成する。

【解決手段】高周波スイッチモジュール10は、アンテナANTに共通端子PIC0が接続する第1スイッチ素子11と、マルチバンドパワーアンプ40に共通入力端子PICt0が接続する第2スイッチ素子30を備える。第2スイッチ素子30の個別出力端子PICt2は、第1のローパスフィルタ12を介して第1スイッチ素子11の個別端子PIC11に接続し、第2のローパスフィルタ13とハイパスフィルタ102の直列回路を介して第1スイッチ素子11の個別端子PIC12に接続する。第2スイッチ素子30の個別出力端子PICt1は位相回路101とSAWデュプレクサ14を介して第1スイッチ素子11の個別端子PIC13に接続し、位相回路101とSAWデュプレクサ15を介して第1スイッチ素子11の個別端子PIC14に接続する。

(もっと読む)

スイッチ回路

【課題】高周波信号の伝送経路におけるインピーダンス変動の変動を抑え、高周波信号の挿入損失を向上させることができるスイッチ回路を提供すること

【解決手段】本発明にかかるスイッチ回路10は、入力端子11と出力端子12との間において信号を伝達する第1の伝送路上に設けられたFET14と、入力端子13と出力端子12との間において信号を伝達する第2の伝送路上に設けられたFET15と、入力端子13とFET15との間に一端が第2の伝送路と接続され、他端がオープンスタブ17である第3の伝送路と、第3の伝送路上に設けられたFET16と、を備え、第1の伝送路上を信号が伝達される場合、FET14及びFET16がオン状態となり、FET15がオフ状態となるように制御されるものである。

(もっと読む)

半導体スイッチ及び無線機器

【課題】端子切替時の歪みの増加を抑制した半導体スイッチ及び無線機器を提供する。

【解決手段】実施形態によれば、電源回路と、駆動回路と、スイッチ部と、補正回路と、を備えた半導体スイッチが供給される。前記電源回路は、電源電位と異なる第1の電位を生成する。前記駆動回路は、前記第1の電位と異なる第2の電位と前記第1の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて共通端子と高周波端子との接続を切り替える。前記補正回路は、前記端子切替信号の変化を検出し、前記第1の電位の極性と等しい極性の電荷を前記駆動回路に供給して前記第1の電位を補正する。

(もっと読む)

高周波モジュールおよび無線通信システム

【課題】低コスト化または小型化を実現可能なマルチバンド対応の高周波モジュールおよび無線通信システムを提供する。

【解決手段】例えば、高周波電力増幅装置HPAIC1は、GSM用のパワーアンプ回路部PABK_LB(PABK_HB)と、GSMかW−CDMAかを選択するモード設定信号Mctlを受けて、アンテナスイッチ制御信号SctlをVSW1レベルかVSW2レベルで出力する制御回路を備える。VSW2は、発振回路OSCからのクロック信号を用いてVSW1を昇圧することで生成される。HPAIC1は、MctlによってGSMが選択された際には、OSCを停止させると共にVSW1レベルのSctlをアンテナスイッチ装置ANTSWに出力し、MctlによってW−CDMAが選択された際には、OSCを用いてVSW2レベルのSctlをANTSWに出力する。

(もっと読む)

高周波スイッチ

【課題】マルチモードシステムにおいてSOI基板上に形成された高周波スイッチの挿入損失特性を改善する。

【解決手段】少なくとも1つの第1ポート10および第2ポート20、共通ポート30、第1および第2シリーズスイッチ40,50を有する。第1ポート、第2ポートは、各々高周波信号を入力または出力する。共通ポートは、第1ポートまたは第2ポートを介して入出力される高周波信号を送信または受信する。第1シリーズスイッチは、少なくとも1つの第1のFETを備え、第1のFETのゲートに接続される第1ゲート抵抗への印加電圧に応じて第1ポートと共通ポートとの間を導通または遮断する。第2シリーズスイッチは、少なくとも1つの第2のFETを備え、第2のFETのゲートに接続され、第1ゲート抵抗よりも大きな抵抗値を有する第2ゲート抵抗への印加電圧に応じて第2ポートと共通ポートとの間を導通または遮断する。

(もっと読む)

高周波半導体スイッチ

【課題】送信端子および受信端子に求められる特性を考慮して設計されたFETを有する高周波半導体スイッチを提供する。

【解決手段】高周波半導体スイッチ10は、複数の電界効果型トランジスタ50を有する。複数の電界効果型トランジスタ50は、それぞれ、基板100に間隔を置いて形成されたソース領域130およびドレイン領域140と、当該間隔上であって基板100上に形成されたゲート160と、基板100上に形成されソース領域に接続されるソースコンタクト172と、基板100上に形成されドレイン領域140に接続されるドレインコンタクト182とを含む。受信端子側に接続される受信端子側トランジスタ50aのソースコンタクト172およびドレインコンタクト182間の距離Lrは、送信端子側に接続される送信端子側トランジスタ50cのソースコンタクト172およびドレインコンタクト182間の距離Ltよりも長い。

(もっと読む)

高周波スイッチ回路および高周波スイッチ回路の制御方法

【課題】受信時だけではなく送信時にも消費電力が低減される高周波スイッチ回路を提供する。

【解決手段】本発明の高周波スイッチ回路は、パルス生成手段120と、クロック選択手段130と、降圧手段140と、スイッチング手段150と、を有する。パルス生成手段120は、所定のアクティブ期間を有するクロック選択用パルス信号を生成する。クロック選択手段130は、クロック選択用パルス信号がアクティブのとき基準クロック信号を選択する一方で、クロック選択用パルス信号がアクティブではないとき基準クロック信号よりも周波数が低い低速クロック信号を選択する。降圧手段140は、クロック選択手段130で選択されたクロック信号の周波数に応じた速度で負電荷をキャパシタに蓄積して所定の負電圧を生成する。スイッチング手段150は、所定の負電圧が印加されてオフ状態を維持する少なくとも1つのスイッチ素子を備える。

(もっと読む)

1 - 20 / 271

[ Back to top ]