Fターム[5J055BX06]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 切り換えスイッチ (661) | 複数接続の切り換え (528) | 多入力多出力 (35)

Fターム[5J055BX06]に分類される特許

1 - 20 / 35

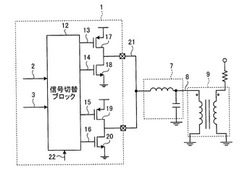

電源回路、電源回路の信号切替方法、帯電装置、画像形成装置

【課題】負荷の増加に伴い、駆動用ドライバをICの外付け素子として用いる場合でも、専用ICを新たに作成するまたは駆動用ドライバに対するプリドライバおよび端子を別途設けることなく、ICと出力端子を共用することで設計およびチップ製作にかかるコストを低減する。

【解決手段】入力信号2,3を切替選択信号22によって切り替え、出力信号13〜16を出力する信号切替ブロック12と、出力信号13〜16をそれぞれチャンネルの異なるスイッチング素子に入力する複数のD級アンプと、を備え、信号切替ブロック12は、複数のD級アンプを、負荷を駆動するための駆動用ドライバ、または外付けされた駆動用ドライバ回路に対するプリドライバとするかを前記切替選択信号により切り替える。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

半導体スイッチ回路

【課題】入出力端子におけるアイソレーション劣化を抑制可能とする。

【解決手段】

第1の入出力端子51と第2の入出力端子52間に第1の単位スイッチ101が、第1の入出力端子51と第3の入出力端子間53に第2の単位スイッチ102が、それぞれ設けられ、第2の入出力端子52とグランドとの間に第1のシャントスイッチ103及び第1のDCカットコンデンサ49が、第3の入出力端子53とグランドとの間に第2のシャントスイッチ104及び第2のDCカットコンデンサ50が、それぞれ直列接続され、第1及び第2の単位スイッチ101,102を構成する第1乃至第4のFET1〜4のゲート・ドレイン間には、それぞれ付加容量41〜44が接続されると共に、第1の単位スイッチ101に対して第1の端子間連絡用抵抗器31が、第2の単位スイッチ102に対して第2の端子間連絡用抵抗器32が、それぞれ並列接続されたものとなっている。

(もっと読む)

誘導性負荷を接続するための方法、及び、その方法を実行するための接続回路

【課題】最小限の突入電流の発生にとどめることを課題としている。

【解決手段】

本発明は、誘導負荷、特に発電機(12)の巻き線(13)を所定の交流中間電圧に接続するための方法に関し、誘導負荷は、ブレーカー(17)を用いて中間電圧に接続されている。突入電流を減少させるために、中間電圧が所定の位相にある場合に、接続がなされるように調節される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

バス幅変換回路、情報入出力装置および電子機器

【課題】光学式のタッチセンサの検査を簡易に行うことの可能なセンサ画素検査用のバス幅変換回路、ならびにそれを備えた情報入出力装置および電子機器を提供する。

【解決手段】バス幅変換回路11cは、複数の受光セルCRを有する入力パネル11に設けられており、受光セルCRの受光信号を出力するN本のセンサ信号線SSigXと、M本(2<M<N)の検査用出力線SoutXとの間に接続されている。バス幅変換回路11cは、N本のセンサ信号線SSigXから入力されるパラレル信号を、M本またはM本よりも少ない数のパラレル信号として、複数の検査用出力線SoutXに出力する。

(もっと読む)

高周波スイッチ回路

【課題】通過損失が少なく出力特性が良いSOI基板上の高周波スイッチ回路を提供する。

【解決手段】本発明の実施形態の高周波スイッチ回路は、シリコン基板20上に形成された酸化膜21上に、第1の端子1と、入出力端子2と、第1の電極4bが前記第1の端子1に電気的に接続され、第2の電極4cが前記入出力端子2に接続されたFET4とを備える。第1の層間絶縁膜22が前記FETを周囲から離間分離し前記酸化膜21に達する溝に埋め込まれて配置され、前記酸化膜21と接続され、前記FET4を周囲から絶縁する。導電体層10が、前記溝内の前記第1の層間絶縁膜22上に形成され、接地端子GNDに接続される。第2の層間絶縁膜23が、前記導電体層10上及び前記FET4上に形成される。直流電圧を供給する配線層7が、前記溝内の第1の層間絶縁膜22上且つ前記導電体層10上に前記第2の層間絶縁膜23を介して形成されている。

(もっと読む)

双方向スイッチシステム、双方向スイッチ、スイッチングマトリックスおよび医療用刺激装置を制御する制御回路構造ならびに方法

セレクタ回路

【課題】回路規模の増大を抑えながら、データ転送システムにおいて受信されるデータのビット順序の変更にある程度柔軟に対処できるセレクタ回路を提供する。

【解決手段】セレクタ回路3は、入力されたビットをそのままのビット順序で出力するか、又はビット順序を入れかえて出力するチャネルスワップ回路11a〜11eと、各チャネルスワップ回路11a〜11eから出力された各ビットを伝送する内部バス12と、内部バス12上の連続した所定個数のビットをそれぞれ選択して取り出すデータフィールド指定回路14a,14b,14cとを備える。入力データの各ビットは、チャネルスワップ回路11a〜11eのうちのいずれかに入力され、出力データのそれぞれは、データフィールド指定回路14a,14b,14cのうちのいずれかによって取り出された複数のビットを含む。

(もっと読む)

多チャンネル高周波信号切替装置

【課題】多チャンネルの高周波信号切り替えを小規模の回路構成にて容易に実現できる多チャンネル高周波信号切替装置を提供する。

【解決手段】多チャンネルの高周波信号を扱う切替回路を、四辺形のマトリクス配線領域11を囲繞するように例えば8組の高周波信号切替スイッチ12A〜12Hを設け、各チャンネルに共通のマトリクス配線領域に集成して、多チャンネル集成型の高周波信号切替回路を構成した。

(もっと読む)

マルチポート型メモリスーパーセル及びデータ経路スイッチング回路を伴う集積回路

【課題】マルチポート型メモリスーパーセル及びデータ経路スイッチング回路を伴う集積回路を提供する。

【解決手段】集積回路は、複数のメモリリクエスタ及びメモリスーパーセルを含む。メモリスーパーセルは、別々にアドレスできる記憶位置の各範囲を各々形成する複数のメモリバンクを備え、メモリスーパーセルは、複数のバンクグループへと編成される。複数のバンクグループの各々は、複数のメモリバンクのサブセット及びそれに対応する専用アクセスポートを含む。集積回路は、更に、複数のメモリリクエスタとメモリスーパーセルとの間に結合されたスイッチを含む。このスイッチは、複数のメモリリクエスタの所与の1つによるメモリ要求に応答して、その所与のメモリリクエスタと、メモリ要求によりアドレスされるバンクグループのうちの特定の1つバンクグループの専用アクセスポートとの間にデータ経路を接続する。

(もっと読む)

ビデオ用およびその他の用途に用いられるクロスポイント・スイッチ

スイッチ再構成タイミング要件の異なる複数のデータフォーマットを同時にサポートするクロスポイント・セレクタスイッチは、演算スイッチ・データに応じて、その出力を選択的にその入力のそれぞれからデータを受け取るように接続する構成可能なスイッチ部と、このスイッチ部に演算スイッチ・データを供給するように動作可能に接続されている構成部とを備えている。構成部は、スイッチ部の複数の異なる構成をサポートするスイッチ構成データを記憶し、また、構成部は、スイッチ部の異なる構成とそれぞれ関連付けられた異なる演算更新コマンドを受け取って、異なる演算更新コマンドのどれを受け取ったのかに基づき、記憶しているスイッチ構成データで演算スイッチ・データを更新することでスイッチ部を再構成するように動作する。 (もっと読む)

多値論理ドライバ

【課題】SLVSを多値化して、多値のCML及び2値のSLVSと比べ1ビット当りの消費電力を削減し、SLVSの多値化に際して生じる論理値の違いによる電源電流の変動を補償した多値論理ドライバを提供する。

【解決手段】第1、2の差動プッシュプル回路(DPP)は各々対応する第1、2の差動入力を受け、各々第1〜4のトランジスタ(Tr)を含み、第1、3のTrのドレーン(D)は電源に接続され、第2、4のTrのソース(S)は接地され、第1、3のTrのゲート(G)は正入力に接続され、第2、4のTrのGは補入力に接続され、第1のTrのSと第2のTrのD及び第3のTrのSと第4のTrのDは第1、2のDPPに亘り正・補各々コモン接続されて単一の差動出力を形成し、第1、2のDPPを構成する各4個のTrのオン時の抵抗値は差動出力に接続される伝送路の特性抵抗値Zoを単位として各々3/2、3に設定されている。

(もっと読む)

高周波信号用スイッチ回路

【課題】高周波信号の歪が少ない高周波信号用スイッチ回路を提供する。

【解決手段】SOI基板上に形成された高周波信号用スイッチ回路において、1つのアンテナ端子ANTと複数の高周波端子との間にそれぞれスルースイッチ部を設ける。スルースイッチ部M4Tにおいては、アンテナ端子ANTと高周波端子RF4との間にn個(nは2以上の整数)の電界効果型トランジスタM1〜Mnを直列に接続する。トランジスタM1〜Mnは、共通の制御信号Cont4に基づいてオン状態とオフ状態とを切替える。また、スルースイッチ部M4Tには電界効果型トランジスタMxを設け、トランジスタMnに対して並列に接続する。トランジスタMxのゲートには常時電源電位Vddを印加し、常時オン状態とする。

(もっと読む)

半導体集積回路装置および高周波電力増幅モジュール

【課題】アンテナスイッチの各トランジスタに流れる高周波電流の変化量を低く抑え、高調波歪みを大幅に低減する。

【解決手段】SP6Tスイッチのシャント部31(,32)は、FETなどからなるトランジスタ53〜56、抵抗57〜66、およびDCカット容量となる静電容量素子67〜69から構成されており、抵抗61〜65の抵抗比は、たとえば、1:2:2:2:1となるように設定されている。このように、抵抗比を1:2:2:2:1として抵抗分割することによって、オフ時の基本スイッチを構成する多段に接続されたトランジスタ53〜56にかかるゲート−ソース間電圧、ゲート−ドレイン間電圧、ドレイン・ソース間電圧を均等化でき、特定のトランジスタのゲート−ソース間容量、およびゲート−ドレイン間容量に流れる高周波電流変化が大きくなることを防ぎ、歪を低く抑えることができる。

(もっと読む)

多チャンネル高周波信号切替装置

【課題】多チャンネルの高周波信号切り替えを小規模の回路構成にて容易に実現できる多チャンネル高周波信号切替装置を提供する。

【解決手段】多チャンネルの高周波信号を扱う切替回路を、四辺形のマトリクス配線領域11を囲繞するように8組の高周波信号切替スイッチ12A〜12Hを設け、各チャンネルに共通のマトリクス配線領域に集成して、多チャンネル集成型の高周波信号切替回路を構成した。

(もっと読む)

高周波スイッチ回路

【課題】消費電流を削減することができるアンテナスイッチ半導体集積回路を提供する。

【解決手段】複数のスイッチ用FET4〜11のオンオフを制御する論理回路17に与える制御入力信号INA,INBのうち、送信モードと受信モードと切り替える制御入力信号INAを発振回路18に入力し、高い電圧が論理回路17に必要な送信モードのときにのみ、発振回路18を動作させ、これによって昇圧回路16を動作させ、論理回路17に昇圧された電圧を供給し、受信モードのときには、発振回路18を停止させ、これによって昇圧回路16を停止させる。そして、論理回路32によって、スイッチ201をオンにすることで、昇圧回路16の停止時には、電源電圧を論理回路17に供給する。これによって、昇圧回路の動作期間が少なくなり、消費電流を削減することができる。

(もっと読む)

スイッチ装置

【課題】高性能化および歩留まりの向上と、制御回路部の低コスト化および低消費電力化とが両立可能なスイッチ装置を提供する。

【解決手段】スイッチ3の入力端子11,12と出力端子21,22との間の接続状態を2つの制御端子へ2値の制御電圧VH,VLを相補的に入力することにより切り替えるスイッチ回路部と、2個の2入力1出力スイッチ41,42の入力端子511,522と入力端子512,521に電圧VHとVLを常時入力し、制御端子VCTLにHレベルを印加した場合、出力端子61,62から制御電圧VH,VLをスイッチ3に入力し、入力端子11,12と出力端子21,22とを平行なバー状態に接続させ、逆に、制御端子VCTLにLレベルを印加した場合、出力端子61,62から制御電圧VL,VHをスイッチ3に入力し、入力端子11,12と出力端子21,22とをクロスした状態に接続させる制御回路部とを備える構成を有する。

(もっと読む)

電圧選択回路、液晶ディスプレイドライバ、液晶表示装置

【課題】電圧選択回路の面積を縮小すること。

【解決手段】本発明に係る電圧選択回路12は、デジタル信号D0〜D5に応じた電圧を第1電圧範囲から選択する第1選択回路(BL−E)と、そのデジタル信号D0〜D5に応じた電圧を第2電圧範囲から選択する第2選択回路(BL−D)とを備える。第1選択回路(BL−E)に含まれる第1MOSトランジスタTEの拡散層とバックゲートとの間には、第1電圧が印加される。また、第2選択回路(BL−D)に含まれる第2MOSトランジスタTDの拡散層とバックゲートとの間には、第2電圧が印加される。第1電圧は第2電圧より小さく、第1MOSトランジスタTEのオフセット長LoEは、第2MOSトランジスタTDのオフセット長LoDより短くなるように設計されている。

(もっと読む)

1 - 20 / 35

[ Back to top ]