Fターム[5J055BX42]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | リセット回路 (286) | 電源電圧低下の検出を行うもの (160)

Fターム[5J055BX42]に分類される特許

1 - 20 / 160

電圧検出回路

低電圧検出回路

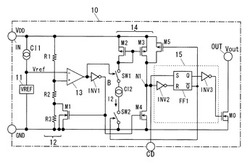

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

電子機器装置

【課題】電子機器装置において、減電圧状態になった場合及び過電圧状態になった場合に、より確実に回路を保護する。

【解決手段】電子機器装置1は、第1の規定電圧値以下の電圧が電子機器装置1に供給される減電圧状態になった場合に、マイコン8をリセットさせ、第2の規定電圧値以上の電圧が電子機器装置1に供給される過電圧状態になった場合に、ヒューズ10を溶断させる減電圧/過電圧検出回路11を備える。減電圧/過電圧検出回路11は、平滑用のコンデンサ4により平滑化された電圧(1次側電圧出力ラインL1から出力された電圧)を監視し、平滑用のコンデンサ4により平滑化された電圧に基いて、減電圧状態、及び過電圧状態を検出する。そして、減電圧/過電圧検出回路11は、過電圧状態を検出した場合には、マイコン8をリセットさせ、過電圧状態を検出した場合には、ヒューズ10を溶断させる。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

電源電圧検出回路

【課題】簡単な構成で電源投入時にも精度よく電源電圧の状態を検出する。

【解決手段】第1スイッチ(122)と第2スイッチ(124)とは直列に接続されてスイッチ部を形成し、第1スイッチ(122)は、基準信号に基づいて開閉が制御される。判定信号生成回路(110)は、第1電源電圧(VDD)と第2電源電圧(VSS)とに基づいて電源電圧判定信号(VG)を生成し、第2スイッチ(124)は、電源電圧判定信号(VG)に基づいて開閉が制御される。第1負荷素子(126)は、第1電源電圧(VDD)とスイッチ部との間に直列に挿入される。スイッチ部は、基準信号(Vref)が所定の第1電圧を超え、電源電圧判定信号(VG)が所定の第2電圧を超えたとき回路を閉成して第1負荷素子(126)に電流を供給し、第1負荷素子(126)とスイッチ部との接続ノードから第1電源電圧(VDD)の状態を示す第1出力信号(VOUT)を出力する。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

周波数入力モジュール

【課題】第1モジュールと第2モジュールが別電源で給電される周波数入力モジュールにおいて、第1モジュールへの給電が第2モジュールへの給電よりも遅れて起動する場合に、第1モジュールへの給電が安定化するまでの期間中、第1モジュールから第2モジュールへ渡される信号の演算を停止させることを可能とする周波数入力モジュールを実現する。

【解決手段】電源モジュールからの第1電源電圧で給電されて入力パルスを処理する第1モジュールと、前記電源モジュールからの第2電源電圧で給電されて前記第1モジュールからの出力パルスの複数個のパルス間隔情報とパルス数情報に基づき前記入力パルスの周波数を演算して出力する第2モジュールを具備し、起動時に前記第1電源電圧が前記第2電源電圧より所定時間遅れて立ち上がる周波数入力モジュールにおいて、

前記第1電源電圧が所定の安定値に達するまでの期間中、前記第2モジュールの演算機能を停止させるリセット信号を出力するリセット手段を備える。

(もっと読む)

半導体装置

【課題】大きな外付け容量素子による時定数に依存することなく遅延時間を設定でき、ユーザが実装システム上でリセット解除に代表されるパルス変化の遅延時間を容易に変更する事ができ、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間が短くなる虞を抑制する。

【解決手段】発振回路(3)の発振動作で生成されるパルス信号をカウントし、カウント値が所定値に達したところでリセット解除に代表されるパルス変化のタイミングを生成する技術において、半導体装置の外部端(P1)子に接続される抵抗素子(R8)の抵抗値によって発振回路の発振周波数を可変にする。外付け抵抗素子によってリセット解除に代表されるパルス変化のタイミングを可変に設定することができ、それは、大きな外付け容量素子を用いる時定数に依存する遅延時間を必要とせず、故に、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間は短くならない。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

リセット回路

【課題】マイクロコンピュータとCPUを安全かつ確実にリセットして正常起動させる。

【解決手段】第1制御回路41は第2電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC20は第1電圧をレギュレートして生成した第2電圧を第1制御回路41に供給し、第2制御回路42は第3電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC30は、第3電圧をレギュレートして生成した第4電圧を第2制御回路42に供給する機器において、リセット回路100は、第1電圧が第5電圧を超えて150msが経過するまでリセット信号の出力を継続させ、第1電圧が第5電圧を超えてから150msが経過するとリセット信号の出力を停止する。(第1電圧≧第2電圧、第3電圧≧第4電圧、第1電圧>第3電圧、第5電圧>第2電圧)

(もっと読む)

減電圧リセット回路及びこれを用いた電源装置

【課題】より確実に安定した減電圧監視を行うことが可能な減電圧リセット回路及び電源装置を提供する。

【解決手段】減電圧リセット回路15は、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第1トランジスタ153と、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第2トランジスタ154と、監視対象電圧V1の供給を受けて動作し、監視対象電圧V1が第1閾値電圧を下回っているときに第1トランジスタ153をオンさせる第1監視部151と、監視対象電圧V1とは異なる駆動電圧V0の供給を受けて動作し、監視対象電圧V1が第1閾値電圧よりも低く第1監視部151の下限動作電圧よりも高い第2閾値電圧を下回っているときに第2トランジスタ154をオンさせる第2監視部152と、を有する。

(もっと読む)

モードコントロール回路

【課題】 パワーダウンモードを含む複数の動作モードを有する半導体集積回路において、モード切り換えを行うモードコントロール回路の消費電力を少なくする。

【解決手段】 制御電圧VCに基づきパワーダウンを設定するか解除するかの判定を行う回路としてオフセット付き電圧比較器30Aを設けた。制御電圧VCがオフセット電圧V0よりも低く、オフセット付き電圧比較器30Aがパワーダウン解除信号MD0を非アクティブレベルとしている間は、基準電圧発生回路10Aを動作させず、制御電圧VCとの比較に用いる基準電圧V1〜V3を出力させない。制御電圧VCがオフセット電圧V0を越えて上昇し、パワーダウン解除信号MD0がアクティブレベルになったとき、基準電圧発生回路10Aを動作させ、基準電圧V1〜V3と制御電圧VCとの比較によるモード切り換えを行わせる。

(もっと読む)

活線挿抜制御回路

【課題】解除電圧のばらつきを低減した活線挿抜制御回路を提供する。

【解決手段】実施形態によれば、出力回路と、電圧発生回路と、検出回路と、補正回路とを備えた活線挿抜制御回路が提供される。前記出力回路は、活線挿抜基板に設けられた半導体装置の出力信号を電源電圧が解除電圧以下のときディスエーブルに切替え、前記電源電圧が前記解除電圧よりも高いときイネーブルに切替えることのできるイネーブル信号を生成する。前記電圧発生回路は、前記電源電圧が供給されるMOSFETを含み、前記電源電圧に応じて変化し前記解除電圧を検出する基準となる第1の電圧を発生する。前記検出回路は、前記第1の電圧を検出する。前記補正回路は、前記検出回路の出力に応じて前記第1の電圧を一定値に補正する。

(もっと読む)

パワーオンリセット回路

【課題】回路の消費電流を低減可能な、パワーオンリセット回路を提供すること。

【解決手段】抵抗分圧回路(R3,R4)によって得られた電源電圧VDDの検出電圧Vcが基準電圧Vrefを超えているとき、リセット解除信号を出力するコンパレータC2と、基準電圧Vrefよりも高い所定電圧を検出する第2の電圧検出回路D2と、第2の電圧検出回路D2によって前記の所定電圧が検出されているときに抵抗分圧回路(R3,R4)とコンパレータC2に流れる電流を遮断するスイッチM1,M2と、スイッチM1,M2によって電流が遮断されているときにリセット解除信号の出力を補償する補償回路とを備え、第2の電圧検出回路D2の消費電流を、抵抗分圧回路(R3,R4)とコンパレータC2との合計消費電流よりも低く設定した、パワーオンリセット回路。

(もっと読む)

電子回路、パワーオンリセット回路、集積回路装置及び電子機器

【課題】電源投入時に初期状態を確実に設定できる電子回路、パワーオンリセット回路、集積回路装置及び電子機器等を提供すること。

【解決手段】電子回路は、各回路素子がトランジスターで構成される複数の回路素子XA1〜XB2と、第1の高電位電源電圧VDDが供給され、VDDが所定の電圧レベルになるまでは、低電位電圧レベルに設定され、VDDが所定の電圧レベルを越えると、VDDに追従して電圧レベルが上昇する第2の高電位電源電圧VINTを出力する電源出力回路100とを含む。複数の回路素子のうち、初期状態においてその出力ノードが高電位電圧レベルになる回路素子である第1のグループの回路素子XA1、XA2には、VDDが供給され、初期状態においてその出力ノードが低電位電圧レベルになる回路素子である第2のグループの回路素子XB1、XB2には、VINTが供給される。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

低電圧検出回路

【課題】電源投入時および通常動作時において信頼性の高い正確な低電圧検出を可能とするとともに、ICのチップサイズの小さい低電圧検出回路を提供する。

【解決手段】第1の基準電圧あるいは入力電圧から生成される出力インピーダンスが小さい第1の電流源と第2の電流源と、第1の電流源と前記第1の基準電圧よりも電圧の低い第2の基準電圧に接続され、両電圧の電位差が所定の電位差以下になったときに、閉状態となるスイッチング素子と、一方が、スイッチング素子を介して、第1の電流源に接続され、他方が、第2の電流源に接続され、スイッチング素子が閉状態となったときに、第2の電流源に接続される結線から低電圧検出信号を出力するカレントミラー回路とを備える。

(もっと読む)

1 - 20 / 160

[ Back to top ]