Fターム[5J055EZ12]の内容

Fターム[5J055EZ12]に分類される特許

161 - 180 / 670

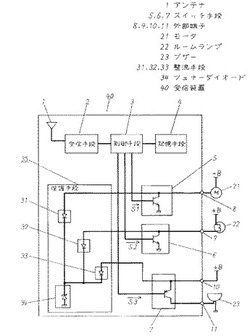

受信装置

【課題】主に自動車のドアの施解錠などに用いられる受信装置に関し、安価であり、かつ受信装置単体で正負逆転した電圧に耐えうることを両立したものを提供することを目的とする。

【解決手段】保護手段35を、一つのツェナーダイオード34と複数の整流手段31〜33で構成し、ツェナーダイオード34のアノード電極をグランドに接続すると共に、カソード電極を、複数の整流手段31〜33の一端と接続し、複数の整流手段31〜33の他端はスイッチ手段5〜7と接続する。

(もっと読む)

アナログスイッチ回路

【課題】切替え時のノイズを低減したアナログスイッチ回路を提供する。

【解決手段】入力信号をn個(nは、1以上)の出力信号としてそれぞれ出力するn個のスイッチ素子と、前記n個のスイッチ素子を制御するスイッチ制御回路と、前記入力信号の負荷となるインピーダンス素子と、前記インピーダンス素子を制御するインピーダンス制御回路と、を備え、前記スイッチ制御回路は、前記n個のスイッチ素子のすべてがオフ、またはいずれか1つがオンとなるように制御し、前記インピーダンス制御回路は、前記n個のスイッチ素子のいずれか1つがオンのときは、前記インピーダンス素子を最大のインピーダンスに制御し、前記n個のスイッチ素子がすべてオフのときは、前記インピーダンス素子を前記最大のインピーダンスよりも小さい第1のインピーダンスに制御する、ことを特徴とするアナログスイッチ回路が提供される。

(もっと読む)

スイッチ回路

【課題】シリーズFETおよびシャントFETとして4端子NMOSFETを用いるSPSTスイッチ回路では、シリーズFETがオン状態で、シャントFETがオフ状態のときに、SPSTスイッチ回路はオン状態になる。FETのバックゲートには寄生ダイオードが存在し、入力交流信号電圧が所定の閾値を超えると、寄生ダイオードがオン状態になる。その結果、SPSTスイッチ回路はスイッチ・デバイスとしての線形動作を維持できなくなり、挿入損失特性やゆがみ特性が悪化する場合がある。

【解決手段】FETのバックゲートに、バイアス電圧を印加するためのバイアス電源を設ける。このバイアス電源として、DC−DC変換回路を用いることで、SPSTスイッチ回路をシリコン半導体チップ化することが容易になる。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】低電圧動作が可能でありながら、中間電源電圧の供給の有無に関わらず動作可能である表示パネルドライバを提供する。

【解決手段】データ線ドライバ3が、出力アンプ回路14と出力端子16A、16Bとを具備する。出力アンプ回路14は、電源電圧VDDと電圧VMLとの供給を受けて、正の駆動電圧を出力する正専用出力段24Aと、電源電圧と接地電圧の間の駆動電圧を出力可能な正負共用出力段28とを備えている。正専用出力段24Aのプルダウン出力トランジスタは、ディプレッション型であり、正負共用出力段28のプルダウン出力トランジスタは、エンハンスメント型である。電圧VMLがVDD/2に設定されたときは、正専用出力段24Aが正の駆動電圧を出力端子16A又は16Bに出力する。電圧VMLが接地電圧VSSに設定されたときは、正負共用出力段28が正の駆動電圧を出力端子16A又は16Bに出力する。

(もっと読む)

切替回路

【課題】信号の電力漏洩を抑制することができる切替回路を提供することを課題とする。

【解決手段】第1の端子(P1)と、第2の端子(Tx)と、第3の端子(Rx)と、前記第1の端子及び前記第2の端子間に直列に接続される第1のトランジスタ(301)と、前記第1の端子及び前記第3の端子間において前記第1の端子側から順に接続される第1のインピーダンス変換素子(312)、第2のトランジスタ(302)、第3のトランジスタ(303)及び第2のインピーダンス変換素子(313)とを有し、前記第2のトランジスタは、前記第3のトランジスタ及び前記第1のインピーダンス変換素子の相互接続点と基準電位ノードとの間に接続され、前記第3のトランジスタは、前記第1のインピーダンス変換素子及び第2のインピーダンス変換素子間に直列に接続される切替回路が提供される。

(もっと読む)

半導体装置

【課題】より適切にリセット信号を出力することが可能な半導体装置を提供する。

【解決手段】半導体装置は、信号端子の電圧に応じてリセット信号が出力される出力端子と、信号端子と電源との間に接続され、接地にゲートが接続された第1のMOSトランジスタと、信号端子と接地との間に接続された第1の容量素子と、信号端子と接地との間に接続され、第1の端子にゲートが接続された第2のMOSトランジスタと、電源と第1の端子との間に接続され、接地にゲートが接続された第3のMOSトランジスタと、第1の端子と第2の端子との間に接続され、接地にゲートが接続された第4のMOSトランジスタと、電源と第2の端子との間に接続された第2の容量素子と、第2の端子と接地との間に接続され、電源にゲートが接続された第5のMOSトランジスタと、を備える。

(もっと読む)

誘導負荷制御装置

【課題】本発明は、誘導負荷に流れる負荷電流を止めなくても、負荷電流の電流検出部のオフセットを検出して補正をすることができる、誘導負荷制御装置の提供を目的とする。

【解決手段】誘導負荷30に流れる負荷電流の電流検出値を出力する電流検出回路12と、電流検出値に電流検出回路12のオフセットを反映することにより電流検出値を補正した補正検出値を出力する補正回路13と、負荷電流の電流値がその指示値に一致するように、補正検出値に基づいて、誘導負荷30を駆動するためのPWM信号のデューティ比を制御する制御回路14とを備えており、制御回路14は、負荷電流の電流値が安定した状態での制御方式を、閉ループ制御からその閉ループ制御で制御されていたデューティ比を維持するように制御する開ループ制御に切り替え、開ループ制御に切り替えられた状態で電流検出回路12のオフセットが検出される、誘導負荷制御装置。

(もっと読む)

スイッチ回路に給電する供給回路

エネルギ効率を改善するよう、スイッチ回路(2)に給電する供給回路(1)は、電源(7)から第1の量の入力電力を受けて、スイッチ回路(2)の制御部(3)を有する出力回路(5)へ第1の量の出力電力を供給する第1の供給モードと、第2の量の入力電力を受けて、第2の量の出力電力を供給する第2の供給モードとを有する。第1の量の出力電力は、第2の量の出力電力よりも大きい。第2の量の入力電力は、零よりも大きく、且つ、スイッチ回路(2)を動作させるのに必要なスイッチ電力の量よりも小さい。スイッチ回路(2)は、負荷(8)を切り換えるリレーを有してよい。第1の量の入力電力は、リレーの主接触部を介して到達してよい。スイッチ(47)は、出力信号レベルを切り替えてよい。リレーは、双安定リレーであってよい。  (もっと読む)

(もっと読む)

スイッチ回路

【課題】周辺回路を誤動作させないスイッチ回路を提供する。

【解決手段】第一端子P1が内部回路への負の入力電圧を入力される時、NMOSトランジスタ12はオフするよう制御されているが、入力電圧が負であるので、この時のNMOSトランジスタ12のゲート・ソース間電圧に基づき、NMOSトランジスタ12が完全にオフしないで例えば弱反転領域で動作する。すると、接地端子VSSから第一端子P1にNMOSトランジスタ12、13を介して電流が流れる。よって、電源端子VCCでなくて接地端子VSSからこの電流は流れるので、この電流が流れることにより、電源電圧が低くならず、その電源電圧を使用する周辺回路が誤動作しない。

(もっと読む)

半導体スイッチ、半導体スイッチMMIC、切り替えスイッチRFモジュール、耐電力スイッチRFモジュールおよび送受信モジュール

【課題】簡素な構成で受信系の性能を維持しつつ、受信時の入力電力に応じて信号を切り替えることができる半導体スイッチを提供する。

【解決手段】第1入出力端子P1と第2入出力端子P2との間に直列に接続された第1FET2と、第1入出力端子P1と第3入出力端子P3との間に接続された伝送線路4と、伝送線路4と平行に配置され、伝送線路4を通過する高周波信号の一部を分岐させる伝送線路7と、伝送線路7の一端に接続され、分岐された高周波信号の電力レベルに応じた直流電圧を出力する検波回路8とを備え、検波回路8からの出力に応じて第1FET2がスイッチング制御されることにより、第1入出力端子P1から第2入出力端子P2または第3入出力端子P3までの経路が切り替えられる。

(もっと読む)

ソレノイド電流制御回路

【課題】低損失かつ高精度の電流検出手段を有するレノイド電流制御回路を提供することにある。

【解決手段】

直流電源1に対して直列接続されたハイサイドMOSFET4とローサイドMOSFET5との接続点からソレノイド6に電流を供給する。制御回路3は、ハイサイドMOSFET及びローサイドMOSFETのオンオフを制御する。センスMOSFET7とセンス抵抗8との直列回路が、ローサイドMOSFET5と並列に接続される。誤差増幅器9は、センス抵抗8の両端の電圧を増幅する。制御回路2の電流算出部2A,2Bは、誤差増幅器の出力値を用いて、ローサイドMOSFETがオフとなる期間の電流を算出する。

(もっと読む)

アナログスイッチ回路

【課題】入力信号電圧が変化する場合にも、オン抵抗の変動によって入力信号波形に生ずる歪みを低減し、入力連続信号の広い周波数帯域に渡ってオン抵抗を一定に保つことができるアナログスイッチ回路を提供することを課題とする。

【解決手段】ソースが第1のスイッチ端子に接続され、ドレインが第2のスイッチ端子に接続される第1の電界効果トランジスタ(MN)と、電荷を充電するための第1の容量(CP)と、電荷を充電するための第2の容量(CA)と、直流電圧ノードと基準電位ノードとの間に第1の容量を接続するための第1のスイッチ回路(S1HP,S1LP)と、第1の容量及び第2の容量を並列に接続するための第2のスイッチ回路(S1HS,S1LS)と、第1の電界効果トランジスタのゲートとソースとの間に第2の容量を接続するための第3のスイッチ回路(S2HS,S2LS)とを有するアナログスイッチ回路が提供される。

(もっと読む)

二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路

【課題】回路を構成する二重ゲート電界効果トランジスタの動作モードを、回路組み上げ後に適宜変更できるようにした二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路を提供する。

【解決手段】二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路は、二重ゲート電界効果トランジスタX1(21)の第1ゲートG1に第1の入力信号in1を加え、第2ゲートG2に選択回路11aを接続し、その選択回路11aに第1の入力信号in1と第2の入力信号in2を加え、選択回路11aにより第1の入力信号in1または第2の入力信号in2を選択して第2ゲートG2に加える。第2ゲートG2に切り替えて入力される入力信号に応じて、3端子動作又は4端子動作を行わせる。

(もっと読む)

スイッチングボックス回路、スイッチングブロック回路、およびFPGA回路

【課題】高集積化および低消費電力化を可能にする。

【解決手段】第1乃至第4の方向にそれぞれ設けられた第1乃至第n(≧1)の信号線と、前記第1乃至第4の方向にそれぞれ設けられた第1乃至第nの入出力部であって、各方向における第i(1≦i≦n)の入出力部は、一端が対応する方向の第iの信号線に接続する第1乃至第nの入出力部と、第1乃至第2nの接続端子と、前記第1乃至第4の方向にそれぞれ設けられ、各方向において前記第1乃至第nの入出力部のそれぞれと、前記第1乃至第2nの接続端子のそれぞれを接続するためにそれらの間に1個ずつ設けられ、ゲートにクロック信号を受ける2n2個のスピンMOSFETと、を備えている。

(もっと読む)

液晶表示装置の駆動方法

【課題】トランジスタの劣化を抑制する。

【解決手段】第1の期間と、第2の期間とを有する。第1の期間において、第1のトランジスタと第2のトランジスタとが交互にオンとオフとを繰り返し、第3のトランジスタと第4のトランジスタとはオフになる。第2の期間において、第1のトランジスタと第2のトランジスタとはオフになり、第3のトランジスタと第4のトランジスタとが交互にオンとオフとを繰り返す。こうして、トランジスタがオンになる時間を短くすることができるので、トランジスタの特性劣化を抑制する。

(もっと読む)

半導体集積回路装置

【課題】電圧パルスで振動子を駆動する送信回路において、誤送信や波形オーバーシュートを改善するため出力がハイインピーダンス状態にならない回路構成を提供し、且つ複数チャネルを集積化した半導体集積回路装置を実現する。

【解決手段】最も絶対値の大きい正電圧VPP1及び負電圧VNN1が供給された従来のパルス発生回路部10と、2番目に絶対値が大きい正電圧VPP2が供給されたP型アナログスイッチタイプのパルス発生回路部20と、2番目に絶対値が大きい負電圧VNN2が供給されたN型アナログスイッチタイプのパルス発生回路部30と、接地電位が供給されたN型アナログスイッチタイプの接地レベルダンピング回路部40とを備える送信回路において、10、20、30、及び40がそれぞれ出力端子OUTに接続される。スイッチ制御信号S1〜S5によって10、20、30、及び40を各別にオンオフして超音波振動子50を駆動する。

(もっと読む)

RFIDタグ

【課題】トランジスタと容量によって情報を記憶し、リフレッシュを必要としないRFIDタグを提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、容量およびバッファを有するRFIDタグであり、第2のトランジスタのソースおよびドレインの一方は入力端子に電気的に接続され、ソースおよびドレインの他方は、第1のトランジスタのソースおよびドレインの一方かつ第3のトランジスタのソースおよびドレインの一方に電気的に接続され、第1のトランジスタのソースおよびドレインの他方は容量の一方の電極かつバッファの入力に電気的に接続され、容量の他方の電極は基準電圧端子に電気的に接続され、バッファの出力は出力端子および第3のトランジスタのソースおよびドレインの他方に電気的に接続される。

(もっと読む)

集積回路装置及び電子機器

【課題】様々な電気光学パネルに対応した場合にも適正な表示画像を得ることができる集積回路装置等の提供。

【解決手段】集積回路装置は駆動回路と制御回路を含み、制御回路はアドレス制御回路を含む。表示メモリーには電気光学パネルの第1、第2の表示領域の表示データを記憶する第1、第2のメモリー領域MR1、MR2が確保される。アドレス制御回路は、第1の表示モードでは第1、第2のメモリー領域MR1、MR2のアドレスを、第1のアドレスAD1から第NのアドレスADNへと変化させて、表示データを読み出し、第2の表示モードでは、第1のメモリー領域MR1のアドレスについては第1のアドレスAD1から第NのアドレスADNへと変化させ、第2のメモリー領域MR2のアドレスについては第NのアドレスADNから第1のアドレスAD1へと変化させて表示データを読み出す。

(もっと読む)

電子装置およびその外部電源供給装置の制御方法

【課題】電子装置およびその外部電源供給装置の制御方法を提供する。

【解決手段】本発明による電子装置1は、オン状態とオフ状態を有する外部電源供給装置5と電気接続し、該電子装置はスイッチモジュール2と、内部電源モジュール3とを含み、スイッチモジュールが触発されると、スイッチ信号を生成する。内部電源モジュールは、スイッチ信号を受信し、トリガ信号を生成して、外部電源供給装置に伝送することにより、外部電源供給装置をオフ状態からオン状態に切り換え、該外部電源供給装置は、電子装置に電源を供給する。

(もっと読む)

電流モード回路

【課題】改良された歪み特性,低減された消費電力,低減された回路サイズおよび向上されたサンプリングレートの少なくとも1つを可能にする電流モード回路の提供を図る。

【解決手段】電流信号IINをサンプリングする電流モード回路40であって、前記電流信号が印加される第1ノード(IIN)と、それぞれ経路を通って前記第1ノードに導電的に接続され得るX個の第2ノードA〜Dと、前記第1ノードと前記第2ノード間の接続を、前記電流信号を構成する電荷の異なるパケットが、時間の経過により異なる前記経路を通ってステアされるように制御するステアリング手段42と、を有し、前記Xは、3以上の整数であり、前記ステアリング手段は、X個の時間インターリーブされた湾曲の制御信号を生成する制御信号生成手段と、前記経路を通って分配され、前記X個の湾曲の制御信号に従って制御を実行するスイッチング手段と、を有するように構成する。

(もっと読む)

161 - 180 / 670

[ Back to top ]