Fターム[5J055EZ12]の内容

Fターム[5J055EZ12]に分類される特許

101 - 120 / 670

半導体スイッチ回路

【課題】 切替時間の短縮と消費電流の低減を図ることができる半導体スイッチ回路を提供する。

【解決手段】 外部からの経路切替信号の状態が変化した直後から予め設定された時間だけ、レベルシフト短絡スイッチ回路でレベルシフトしない高電圧でスイッチ回路を駆動し、一定時間経過後はレベルシフト短絡スイッチ回路を開放させることによりレベルシフト回路を経由させ、電圧降下させた電圧でスイッチ回路を駆動させる。

(もっと読む)

半導体集積回路装置及び送受信システム

【課題】入力信号に対する増幅器の出力信号の利得特性を線形化するために必要な回路の面積を低減できる半導体集積回路装置及び送受信システムを提供する。

【解決手段】半導体集積回路装置は、切り替え可能な複数の第1の利得特性を有し、入力信号に対して前記第1の利得特性を切り替えて中間信号を生成し、第2の利得特性を有する回路に前記中間信号を出力する線形化回路を備え、前記線形化回路は、少なくとも1つの第1の整流素子を有し、前記入力信号を線形化する線形化器と、前記第1の整流素子と逆極性の複数の第2の整流素子と、制御信号に基づき前記複数の第2の整流素子のうち少なくとも1つを選択する第1の切り替え部とを有し、前記線形化器に並列に接続され、前記線形化器による前記入力信号の線形化を抑制する線形化抑制器とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

半導体集積回路

【課題】 ゲート酸化膜の信頼性を維持しながら、待機時のリーク電流を抑制でき、回路面積の増加を最小限にでき、欠陥を確実に検出することができる半導体集積回路を実現する。

【解決手段】 論理回路10と電源電圧Vddの供給端子との間にスイッチング回路20を設ける。動作時に、スイッチング回路20のトランジスタMP0のゲートに0Vの電圧を印加し、チャネル領域に電源電圧Vddと同じかまたは僅かに低いバイアス電圧VBを印加することで、トランジスタMP0のしきい値電圧を低くし、その電流駆動能力を大きくする。待機時にトランジスタMP0のゲートに電源電圧Vddと同じ電圧を印加し、ソースに電源電圧より低い電圧を印可し、チャネル領域に電源電圧Vddと同じかまたはそれより高いバルクバイアス電圧VBを印加し、トランジスタMP0のドレイン電流を最少化することにより、論理回路10の電流経路を遮断し、リーク電流の発生を抑制する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

アンテナスイッチおよびそれを内蔵した高周波モジュール

【課題】アンテナスイッチの高調波歪特性を改善する。

【解決手段】アンテナスイッチのアンテナ端子2にアンテナが接続され、第1信号端子3とアンテナ端子2の間に第1転送スイッチ100が接続され、第2信号端子4とアンテナ端子2の間に第2転送スイッチ101が接続され、第1信号端子3と接地電位の間に第1シャントスイッチ102が接続され、第2信号端子4と接地電位の間に第2シャントスイッチ103が接続される。負電圧生成回路104の入力10は第1信号端子3に供給される送信信号に応答可能とされ、出力端子11に生成される負電圧に応答して第2転送スイッチ101と第1シャントスイッチ102とはオフ状態に制御される。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

適応標本化装置および適応標本化プログラム

【課題】入力信号のフレームを標本化する場合に、入力信号の性質に応じた不等間隔で標本化を行う技術を提供する。

【解決手段】適応標本化装置1Aは、フレーム記憶手段10と、フレームに対して、標本点数を減らした複数の異なる標本化間隔で標本化して縮小信号とし、この縮小信号群を出力する階層化信号縮小手段20と、この各縮小信号を入力信号と同じ標本化間隔に戻して、フレームとの誤差をブロックごとに定量化し誤差信号として出力する階層化誤差演算手段30と、フレームの各ブロックに対して適用する標本化間隔の割り当て方である標本化パターンを複数記憶する標本化パターンデータベース50と、各誤差信号と、標本化パターンとに基づき、誤差を最適化する標本化パターンを探索する最適化手段70と、この最適化手段が求めた標本化パターンに基づき、入力信号のフレームを標本化し、出力信号として出力する標本選択配置手段80と、を備える。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、インバータとして機能する回路(3つのトランジスタTr21,Tr22,Tr23)と、トランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21とを有している。閾値補正回路21は、トランジスタTr21,Tr22のゲートに対して、トランジスタTr21,Tr22の閾値電圧Vth1,Vth2をオフセットとして設定するようになっている。

(もっと読む)

データ出力回路

【課題】プリエンファシスまたはディエンファシスのためのドライバの追加がなくても、プリエンファシスまたはディエンファシス動作を行えるデータ出力回路を提供すること。

【解決手段】インピーダンスコードによって各々オン・オフされ、出力ノードにデータを出力する複数の駆動手段311、312を備え、前記インピーダンスコードが、前記駆動手段をターンオンさせる値を有する第1のグループと前記駆動手段をオフさせる値を有する第2のグループとに分けられ、プリエンファシス期間の間には、前記第2のグループによる制御を受ける駆動手段の全部または一部がターンオンされる。

(もっと読む)

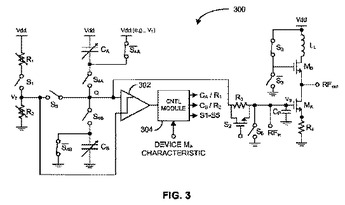

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路

【課題】複数の電源の供給を受けて動作する信号処理回路においていずれの電源が供給されない場合にも回路の破壊を回避する信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路を提供する。

【解決手段】複数の電源の供給を受け、複数の電源により動作する通信端末装置200、データ変換部160,170,180への信号の供給を制御する信号供給制御部130,140,150は、複数の電源の少なくとも1つが供給されていない場合に、供給されていない電源とは異なる電源に起因する信号の通信端末装置200、データ変換部160,170,180への供給を制限する。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

高耐圧スイッチ回路およびそれを用いた半導体集積回路装置

【課題】 双方向スイッチにおいて、ドレイン電圧またはドレイン-ソース間電圧に基づいて、上記スイッチのゲート-ソース間電圧を制御する手段と、上記制御手段を介して、上記スイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを提供する。

【解決手段】 双方向スイッチであるメインスイッチと、上記メインスイッチのゲート-ソース間電圧を、上記メインスイッチのドレイン電圧、ソース電圧に基づいて制御する手段と、上記制御手段を介して上記メインスイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを構成する。

(もっと読む)

入力回路

【課題】ヒステリシス電圧や応答速度の電源電圧依存性を緩和し、幅広い範囲の電源電圧条件下で動作するヒステリシス特性を有する入力回路を提供すること。

【解決手段】低電源電圧条件下でヒステリシス電圧が小さくなる回路(PMOSトランジスタ101〜103及び、インバータ501)と、低電源電圧条件下でヒステリシス電圧が大きくなる回路(PMOSトランジスタ101、104及び、インバータ501)とを設けた。

(もっと読む)

101 - 120 / 670

[ Back to top ]