Fターム[5J055GX09]の内容

Fターム[5J055GX09]の下位に属するFターム

表示パネル、表示素子の配置図 (18)

Fターム[5J055GX09]に分類される特許

1 - 20 / 90

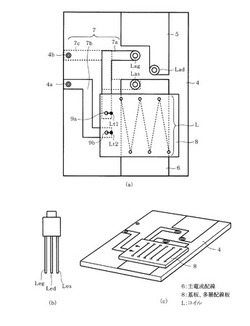

誘導性負荷の駆動回路

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

電磁機器駆動装置および電磁機器の駆動方法

【課題】電磁機器の累積使用量が多くなっても少ないと同じ一定時間で電磁機器を動作状態から停止状態に移行させる。

【解決手段】電磁機器駆動装置は、励磁用電源から電磁コイルへの通電が停止したときに逆起電力によって電磁コイルの両端間に生じる電圧をクランプするフリーホイール回路と、フリーホイール回路によってクランプされた電圧が、電磁機器の累積使用量が少ないときよりも多いときの方が高くなるように、フリーホイール回路の動作を制御するコントローラーと、を備える。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

電子デバイス、およびオーディオデバイスを制御する複数の受動スイッチを有するオーディオアクセサリ

【課題】電子デバイスと、オーディオデバイスを制御するための複数の受動Spスイッチを有するオーディオアクセサリとを提供すること。

【解決手段】電子デバイスを制御するように適合されているシステムであって、システムは、電子デバイスに結合されているオーディオアクセサリを含み、オーディオアクセサリは、複数の抵抗型スイッチを有し、電子デバイスは、バイアス抵抗器とグラウンド接続とを介して抵抗型スイッチに電力を提供するように適合されているバイアス電圧供給源と、測定モジュールとを含み、測定モジュールは、バイアス電圧供給源と抵抗型スイッチとの間の接続上のバイアスポイントを監視することと、オーディオ出力によって引き起こされるグラウンドオフセット電圧を決定することと、グラウンドオフセット電圧を補償することと、スイッチのどれが係合しているかを決定することとを行うように適合されている。

(もっと読む)

半導体装置

【課題】本発明は、信号線駆動回路におけるトランジスタの特性のばらつきの影響を抑制

する技術に関する。

【解決手段】信号線駆動回路には、各々容量手段と供給手段とを有する第1電流源回路(

437)及び第2電流源回路(438)を設ける。シフトレジスタ(418)から供給さ

れるサンプリングパルスと外部から供給されるラッチパルスに従って、前記容量手段は、

n個のビデオ信号用定電流源(109)の各々から供給される電流を加算した電流を電圧

に変換し、前記供給手段は変換された電圧に応じた電流を供給することで、トランジスタ

の特性によらず、ビデオ信号に応じた電流出力を行うことを特徴とする。前記n個のビデ

オ信号用定電流源から供給される電流値は、20:21:・・・:2nに設定されて、階

調を表現することが可能となる。

(もっと読む)

スイッチ回路

【課題】接点スイッチの仕様が変わっても回路変更が必要なくコストダウンを図ったスイッチ回路を提供する。

【解決手段】電流可変回路9が、接点スイッチ3に対して直列接続される。電流可変回路9は、互いに並列接続された複数の抵抗R1、R2、R3と、この複数の抵抗R1、R2、R3に各々直列接続されると共に互いに並列接続された複数のトランジスタスイッチTr1、Tr2、Tr3と、を備えている。この電流可変回路9は、トランジスタスイッチTr1、Tr2、Tr3のオンオフによって接点スイッチ3がオンのときに当該接点スイッチ3に流れる電流を可変にする。そして、制御ユニットが、接点スイッチ3の仕様に応じた電流が接点スイッチ3に流れるように電流可変回路9を制御する。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

ゲートドライバ

【課題】一導電型のTFTによって構成し、かつ出力信号振幅を正常に得られる回路を提供する。

【解決手段】TFT101、103は、CK1にHレベルが入力されてONし、信号出力部Outの電位がLレベルに確定される。次に、信号入力部Inにパルスが入力されてHレベルとなり、TFT102のゲート電位は(VDD−VthN)まで上昇し、浮遊状態となる。これによりTFT102がONする。次にCK1がLレベルとなり、TFT101、103がOFFする。同時にCK3がHレベルとなって信号出力部の電位は上昇し、同時に容量104の働きによってTFT102のゲートの電位が(VDD+VthN)以上に上昇することによって信号出力部Outに現れるHレベルはVDDに等しくなる。SPがLo、CK3がLo、CK1がHレベルになると、信号出力部Outの電位は再びLレベルとなる。

(もっと読む)

負荷駆動装置

【課題】複数の負荷の駆動状態に応じて、スイッチング損失の低減とノイズの抑制とを図ることができる負荷駆動装置を提供する。

【解決手段】複数の負荷2A〜2Dについて個別に設けられ、半導体スイッチング素子5,6により前記負荷をスイッチング駆動する複数の負荷駆動手段3A〜3Dで、台形波傾き制御プリドライバ7が、NチャネルMOSFET5,6のゲートに対してそれぞれ台形波状のパルス信号を出力する場合に、台形波の立上り及び立下りの傾きを変更可能に構成し、4チャネル駆動の場合は傾きを大きく、1チャネル駆動の場合は台形波の傾きを小さくする。

(もっと読む)

バッファ回路

【課題】TFT特性のばらつきにかかわらず画像ムラがなく、高精細・高解像度の良好な画像を得ることができる半導体表示装置の駆動回路および半導体表示装置を提供する。

【解決手段】半導体表示装置はソース信号線側駆動回路と、ゲイト信号線側駆動回路とを有し、駆動回路はシフトレジスタ回路からのタイミング信号をバッファする複数のインバータ回路を有するバッファ回路を有し、インバータ回路は複数のインバータ回路を並列に接続して構成される。

(もっと読む)

1 - 20 / 90

[ Back to top ]