Fターム[5J056BB28]の内容

論理回路 (30,215) | 目的、効果 (4,057) | 信頼性の向上 (1,356) | 使用環境に対するもの (89) | 温度 (80)

Fターム[5J056BB28]に分類される特許

1 - 20 / 80

半導体装置

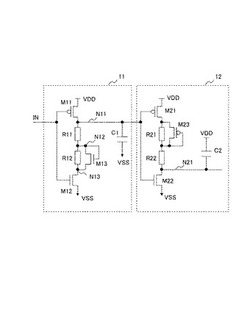

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

LVDS出力回路

【課題】 1個の基準電圧源を用いて、中間電圧(コモン電圧)及び出力振幅について温度特性がフラットになり、搭載されるICチップの面積増大を防ぐことが出来るLVDS出力回路を提供する。

【解決手段】 中間電圧(コモン電圧)作成用の基準電圧はバンドギャップリファレンス回路1の演算増幅器5の出力部から引き出し、振幅を決める定電流回路の基準電圧はバンドギャップ電圧を作る際に使用する抵抗R41、R42の節点14(中間タップ)から引き出す。そして、引き出し部分は電流検出用抵抗R6の温度特性に合わせる。検出用抵抗の温度特性と中間タップの位置での温度特性を合わせることにより、定電流回路3全体としての温度変化を無くすようにする。このようにして、1つのバンドギャップリファレンス回路1を用いて温度変化無しにLVDS出力回路を駆動できる。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

半導体装置

【課題】可変抵抗回路の抵抗値の調整可能範囲が大きな半導体装置を提供する。

【解決手段】この半導体装置は、複数組の抵抗素子RA,RBおよび複数組のトランジスタP,Qを含む出力バッファDOBと、複数のレプリカ回路RPと、複数組の演算増幅器AP,ANとを備え、出力バッファDOBの出力インピーダンスZp,Znが所定値になるように、複数組のトランジスタP,Qのドレイン電流を調整する。したがって、製造プロセスなどの変動によって抵抗素子RA,RBの抵抗値が大きく変動した場合でも、出力インピーダンスZp,Znを所定値に設定できる。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

差動出力回路

【課題】ゲート電圧に対する遅延調整を行わずに、クロスポイントの変動を抑えること。

【解決手段】駆動部100と出力部101は、カレントミラー構成により、プロセス、電圧、温度条件が変動しても共に同一の変動となるため、入力信号INTの信号レベルが“H”から“L”に切り替わる際、MOSFET3、6がオンしているときに、MOSFET5、4がオフ状態からオン状態に速く切り替わることはない。従って、クロスポイントの変動を抑えることができる。また、この構成により、ゲート電圧PL、PR、NL、NRは、電源電圧VSSからVDDまでフルスイングされないため、MOSFET3、6をオンさせ、MOSFET5、4をオフさせる場合、ゲート電圧PLの立ち下がりに対してゲート電圧NLの立ち下がりに遅延をもたせたり、ゲート電圧NRの立ち上がりに対してゲート電圧PRの立ち上がりに遅延をもたせたりする必要がない。

(もっと読む)

半導体装置

【課題】データ出力タイミングの設計を簡略化出来る半導体装置を提供すること。

【解決手段】第1クロックCLKに同期してデータを連続的に出力する半導体装置であって、外部から与えられる前記第1クロックCLKから第2クロックICLKを生成するクロック生成回路50、51と、前記第2クロックICLKに同期して動作し、前記データが入力されるフリップフロップ回路52と、前記フリップフロップ回路52から出力される前記データを外部へ出力する出力バッファ回路54と、バンドギャップリファレンス回路22を含み、該バンドギャップリファレンス回路22により制御される電圧VBGRを発生し、該電圧VBGRを前記クロック生成回路50、51、前記フリップフロップ回路52及び前記出力バッファ回路54へ電源電圧として供給する電源回路とを備える。

(もっと読む)

半導体装置及び情報処理システム

【課題】FETの閾値電圧の変動に起因するアンプのセンスマージンの低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、信号線(BL)に信号を出力する第1の回路(MC)と、FET(Q1、Q2、Q3)と、信号線に基準電位を与える第2の回路(Q5)を備えている。FETQ1はノードN1の電位と駆動信号SETの電位との間の電位差に応じてゲート容量が制御されるゲーテッドダイオードとして機能し、FETQ2は制御信号TGに応じて信号線とノードN1との間の接続を制御し、FETQ3はゲートがノードN1に接続されノードN1の信号電圧を増幅する。導通状態のFETQ2を非導通に制御した後、駆動信号SETの電位は第1の電位から第2の電位に遷移する。FETQ1の閾値電圧の変動量に対応して少なくとも第1の電位をオフセット制御し、FETQ3のセンス増幅時にFETQ1の閾値電圧の変動を補償する。

(もっと読む)

電圧調整回路

【課題】電圧調整回路を提供するための改善された技法を提供する。

【解決手段】供給電圧ノードを出力電圧ノードに接続するプルアップp型閾値デバイスであって、制御信号に依存してオフに切り替えられるように構成されるプルアップp型閾値デバイスを備える電圧調整回路が提供される。プルダウンスタックは、出力電圧ノードを基準電圧ノードに接続し、プルダウンスタックは、直列で接続されるプルダウンp型閾値デバイスおよびプルダウンn型閾値デバイスを備える。インバータは、出力電圧ノードから入力を受け取るように構成され、カットオフ信号を生成するように構成され、プルダウンn型閾値デバイスは、制御信号に依存してオンに切り替えられるように構成され、プルダウンp型閾値デバイスは、カットオフ信号に依存してオフに切り替えられるように構成される。

(もっと読む)

集積回路装置、電子機器及び調整電圧の制御方法

【課題】 温度条件が変化しても停止電圧との適切な電位差を保ち低消費電力を実現する集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、第1の振幅と比べて、入力された発振信号400の振幅の方が大きい場合に、第1の矩形波信号408を出力する第1の矩形波信号生成部11と、前記第1の振幅よりも大きな第2の振幅と比べて、前記発振信号400の振幅の方が大きい場合に、第2の矩形波信号402を出力する第2の矩形波信号生成部12を含む。

(もっと読む)

伝送装置

【課題】従来は、ヒータの制御を主制御部が行うようにしていたため、低温起動時において、装置内が所定の温度以上に加熱され装置動作に入る前の段階で、装置全体に電力を供給することになり、消費電力が多くなるという課題があった。

【解決手段】伝送装置を、主制御部と、消費電力が主制御部よりも小さい副制御部と、伝送装置外部との間で信号を送受信するインタフェース部と、該インタフェース部で受信した信号を増幅する増幅部と、伝送装置内を所定の温度に加熱する加熱部と、伝送装置内の温度を検出する温度検出部とから構成し、伝送装置の起動時において、まず副制御部が起動され、副制御部が増幅部への電力供給を行うとともに、温度検出部により伝送装置内の温度を検出し、伝送装置内が所定の温度以上である場合は、主制御部の起動を行い、伝送装置内が所定の温度未満である場合は、加熱部を加熱制御し、伝送装置内が所定の温度以上になると主制御部の起動を行うようにする。

(もっと読む)

電子回路の作動の監視

【課題】本発明は、電子回路の所与の機能又は動作の実行を監視するための方法及び回路を提供する。

【解決手段】デジタル信号(EN)を監視する方法は、第1のP チャネルMOS トランジスタ(P1)を、監視されるべき前記信号が第1の状態にある期間に負バイアス温度不安定性(NBTI)タイプの劣化状態に置くステップと、前記第1のP チャネルMOS トランジスタ(P1)の飽和電流を表す第1の量(VMES)を、監視されるべき前記信号が第2の状態に切り替わるとき測定するステップと、前記第1の量が閾値(TH)を超えるとき、監視結果を示す検出信号(DET) を与えるステップとを備えている。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】電源電圧を変更することなく、広い温度範囲でリーク電流を抑えて動作する半導体装置を提供する。

【解決手段】しきい値電圧が第1電圧である第1トランジスタを含む高VT部7と、しきい値電圧が第1電圧よりも低い第2電圧である第2トランジスタを含む低VT部8と、温度を測定し、温度が所定の温度より高い高温状態であるか、温度が所定の温度よりも低い低温状態であるかを判定し、高温状態を示す信号又は低温状態を示す信号を出力する温度検知部6と、高温状態を示す信号、又は低温状態を示す信号を受信し、高温状態を示す信号に基づいて高VT部7を動作させ、低温状態を示す信号に基づいて低VT部8を動作させる制御を行う制御部9とを具備する。

(もっと読む)

半導体装置

【課題】オフリーク電流の温度特性が互いに異なる複数の回路ブロックに対して電源制御を行うことにより、消費電力を低減する。

【解決手段】オフリーク電流が第1の温度特性を有するトランジスタによって構成された第1のXデコーダ12と、オフリーク電流が第2の温度特性を有するトランジスタによって構成されたプリデコーダ13及び周辺回路14と、スタンバイ時において温度が第1のしきい値を超えている場合、Xデコーダ12を非活性化させる電源制御回路16と、スタンバイ時において温度が第2のしきい値を超えている場合、プリデコーダ13及び周辺回路14を非活性化させる電源制御回路17とを備える。本発明によれば、複数の回路ブロックに対する電源制御の有無を、互いに異なる温度を基準として判断していることから、各回路ブロックに対して最適な電源制御を行うことが可能となる。

(もっと読む)

半導体装置

【課題】相補電界効果トランジスタのオフ電流の周囲温度の変動に伴う変動を抑制する。

【解決手段】CMOSを構成するNチャンネルMOSトランジスタの基板電圧VPWを生成する基板電圧生成回路31と、上記NチャンネルMOSトランジスタのレプリカであり、かつダイオード接続されたレプリカトランジスタ32と、レプリカトランジスタ32のアノード−カソード間に所定の電圧値VFの電圧を印加する電圧印加部33とを備え、レプリカトランジスタ32の基板電圧は基板電圧生成回路31が生成する基板電圧VPWであり、基板電圧生成回路31は、レプリカトランジスタ32に流れる電流の電流値が所与の目標値となるよう、生成する基板電圧VPWを制御する。

(もっと読む)

CMOSインバータ回路

【課題】低電圧CMOSインバータ回路における製造プロセスバラツキや温度バラツキの影響をオンチップで検知して、製造プロセスバラツキや温度バラツキの影響をキャンセル補正し、論理反転閾値のバラツキを大幅に抑制する低電圧CMOSインバータ回路を提供する。

【解決手段】pMOSFETの論理反転閾値とnMOSFETの論理反転閾値のプロセスバラツキによる変動の差電圧を、そのまま出力電圧変動とする閾値電圧差バラツキモニタ回路を備え、前記閾値電圧差バラツキモニタ回路の出力電圧をCMOSインバータの電源ラインに供給する。また、CMOSインバータ回路における出力電圧の後段に、さらに論理値レベル補正部が設けられ、電源電圧の変動を抑制する。

(もっと読む)

ドライバストレングス調整回路、半導体集積回路、及びドライバストレングスの調整方法

【課題】本発明は、高速にドライバストレングスの調整を行うことが出来、また一度ドライバストレングスの調整を行なった後も、温度や電圧といった外部要因に基づいたドライバストレングスの再調整が可能となるドライバストレングス調整回路、半導体集積回路、及びドライバストレングスの調整方法を提供することを課題とする。

【解決手段】コード情報を、電圧、温度、プロセスばらつきと対応づけてテーブルに記憶する。変化する温度/電圧、及びプロセスばらつき情報を用いてテーブルを参照してコード情報を求めドライバストレングスの調整を行う。

(もっと読む)

半導体集積回路装置

【課題】PTVばらつきによる出力バッファ回路の出力電圧のばらつきを小さく抑えることができる半導体集積回路装置を提供する。

【解決手段】NMOSトランジスタ23に対応してレプリカ回路32と差動アンプ41とを設ける。レプリカ回路32は、テブナン終端回路5と外部信号配線4とNMOSトランジスタ21、23とからなる回路の複製であり、基準電圧VREF1を生成する。差動アンプ41は、NMOSトランジスタ21と共にノードN26の電圧を制御する負帰還回路を構成する。PTVばらつきによりNMOSトランジスタ23のしきい値が高くなると、NMOSトランジスタ37のしきい値も高くなり、NMOSトランジスタ37の能力も下がり、基準電圧VREF1が低下し、ノード26の電圧が低下し、L側出力電圧VOLが低下する。これにより、L側出力電圧VOLのばらつきを小さく抑える。

(もっと読む)

集積回路の入力ポートにおける消費電力を低減するための回路および方法

集積回路(102)の入力ポートにおける消費電力を低減するための回路が開示される。この回路は、集積回路(102)に結合される入力信号を受けるための、集積回路(102)の複数の受信機回路(112、114、116、118)と、複数の受信機回路(112、114、116、118)に結合されたバイアス電流発生器(122)とを備え、バイアス電流発生器(122)は、複数の受信機回路(112、114、116、118)の各受信機回路に対してバイアス電圧を与えてバイアス電流発生器(122)における電流を受信機回路(112、114、116、118)各々にミラーする。集積回路(102)の入力ポートにおける消費電力を低減する方法も開示される。  (もっと読む)

(もっと読む)

1 - 20 / 80

[ Back to top ]