Fターム[5J056CC09]の内容

Fターム[5J056CC09]に分類される特許

1 - 20 / 432

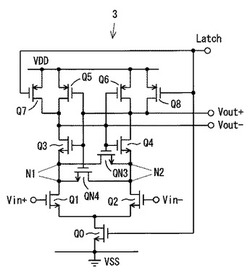

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファ回路を含む出力回路(101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(150)と、複数の単位バッファ回路のそれぞれのインピーダンスを調整するインピーダンス調整部(130)であって、複数の単位バッファ回路のうちの1つと実質的に同一の調整可能なインピーダンスを有するレプリカ回路(131e)と、当該レプリカ回路と並列に接続され、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数に応じて自身を流れる電流量を変化させる負荷電流生成回路(131f)とを含む、インピーダンス調整部と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】より少ない調整ステップでキャリブレーションを完了する。

【解決手段】出力端子(DQに相当)と、出力端子と接続され、出力端子を調整可能なインピーダンスで駆動する出力回路(210に相当)と、出力回路のインピーダンスを段階的に調整するキャリブレーション回路(100)と、を備え、キャリブレーション回路は、キャリブレーション動作の実行を指示するコマンドを受けて、インピーダンスの調整を開始し、インピーダンスを変化させる変化幅を、開始直後に対し以降においてより狭めるように調整する。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

半導体装置

【課題】信号伝送のより高速化を図る。

【解決手段】入力信号Vinと基準信号Vrefとを入力する第1の差動対(Q3、Q4が相当)と、第1の差動対のそれぞれ負荷となる第1及び第2のトランジスタQ2、Q1と、を含む第1の入力回路を備え、第1の入力回路の出力側となる第1のトランジスタQ2は、第2のトランジスタQ1に比べてゲート幅を長くする。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

ロジック回路及び携帯端末装置

【課題】DVDD系ロジック回路とRVDD系ロジック回路との間のアイソレートを実施しながら、小型化及び低コスト化を実現する。

【解決手段】第一のデジタル回路と第二のデジタル回路とを含むロジック回路であって、第一のデジタル回路の動作電圧である第一の電圧値を検出する第一の検出手段と、第二のデジタル回路の動作電圧である第二の電圧値を検出する第二の検出手段と、第一の電圧値と第二の電圧値とを比較する比較手段と、比較手段により得られた比較結果に応じて、第一のデジタル回路と第二のデジタル回路との間の分離結合を行う分離結合手段と、を含む。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

1 - 20 / 432

[ Back to top ]