Fターム[5J064BC08]の内容

圧縮、伸長、符号変換及びデコーダ (21,671) | 細部(回路)構成 (8,519) | 加減算 (922)

Fターム[5J064BC08]に分類される特許

61 - 80 / 922

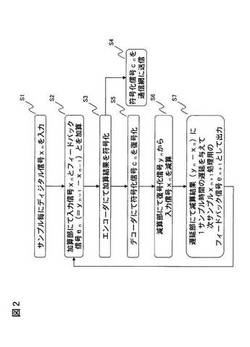

符号化方法、プログラム

【課題】容易に既存の符号化方式と組み合わせることができ、かつ、送信側だけに機能を

追加するだけで、効果的に量子化ノイズの耳障り感を低減することが可能な符号化装置を

実現する。

【解決手段】第nサンプル目のディジタル音響信号サンプルxnとフィードバック信号サンプルとを加算して加算結果を得るステップと、入力された信号をサンプル毎に符号化する所定の符号化方式により加算結果から符号化信号を生成するステップと、符号化信号から上記符号化方式に対応する復号化方式により復号化信号サンプルを生成するステップと、復号化信号サンプルからディジタル音響信号サンプルを減算して減算結果を得るステップと、減算結果を1サンプリング時間遅延させてフィードバック信号サンプルを得る遅延ステップと、をディジタル音響信号サンプルxnの入力がxn+1、xn+2、・・・と継続する間、繰り返し実行する。

(もっと読む)

ΔΣAD変換器

【課題】高分解能のAD変換結果を短時間で得ることを可能とするΔΣAD変換器を実現する。

【解決手段】アナログ入力信号とフィードバック回路のDA変換器の出力信号との差を積分する積分器と、この積分器の積分結果を入力するコンパレータと、このコンパレータの出力をカウントしたデジタル出力信号を前記DA変換器に入力するカウンタとを具備するΔΣAD変換器において、

前記フィードバック回路に設けた多ビットDA変換器と、この多ビットDA変換器の多ビット入力をコントロールし、逐次比較型AD変換器またはΔΣAD変換器として動作させる制御ロジックとを備え、

前記制御ロジックは、前記多ビット入力の上位所定ビットを逐次比較型AD変換動作で決定し、下位所定ビットをΔΣAD変換動作により決定することを特徴とするΔΣAD変換器。

を備える。

(もっと読む)

直交ベクトルを用いたデータ交換装置

集積回路と、集積回路の複数のイニシエータユニットからその集積回路の少なくとも1つのターゲットユニットにメッセージを送信する方法。前記複数のイニシエータユニットは第1のデジタルメッセージを第2のデジタルメッセージに変換し、前記第2のデジタルメッセージが付加され、前記ターゲットユニットに送信される。前記第1のメッセージの前記第2のメッセージへの変換は、単位行列の複数の行或いは複数の列から得られる複数のベクトルによる直交変換の適用を含む。  (もっと読む)

(もっと読む)

部分的な複素変調フィルタバンク

【課題】高品質の操作を可能にする信号を出力するための効率的な概念と、歪が少ない状態で信号を削減するための効率的な概念とを提供する。

【解決手段】第1の実数サブバンド信号と第2の実数サブバンド信号とを含む複数の実数サブバンド信号を処理して少なくとも1つの複素サブバンド信号を提供する装置210であって、この装置は、実数中間サブバンド信号を出力するためのマルチバンドフィルタ204と、上記複数の実数サブバンド信号からの実数サブバンド信号と上記中間サブバンド信号とを結合することによって複素サブバンド信号を出力するための計算器215と、上記実数サブバンド信号を遅延させ、この遅延された実数サブバンド信号を上記計算器215へと供給する遅延器203と、を備える。

(もっと読む)

ΔΣ型アナログデジタル変換器およびそれを用いた電子機器

【課題】ノイズ特性を改善することが可能なΔΣ型アナログデジタル変換器を提供する。

【解決手段】ΔΣ型A/D変換器100は、アナログの入力信号Sinをデジタルの出力信号Soutに変換する。D/A変換器40は、デジタルの出力信号Soutをアナログの帰還信号Sfbに変換する。差分演算回路10は、入力信号Sinに応じた信号Sin’と、帰還信号Sfbに応じた信号Sfb’の差分に応じた差分信号Sdを生成する。フィルタ回路20は、直列に接続された複数の積分器INTを含み、差分信号Sdをフィルタリングする。量子化器30は、フィルタ回路20の出力信号Sfを量子化し、出力信号Soutを生成する。フィルタ回路20は、ある積分器INT3の出力信号に所定の係数を乗じそれより前の積分器INT2の入力へと帰還する少なくともひとつの帰還係数回路CO9を含み、当該帰還係数回路CO9の係数は調節可能に構成される。

(もっと読む)

ΔΣ型A/D変換器

【課題】アナログ入力信号をディジタル信号に変換するためのチャネルを複数備えるΔΣ型A/D変換器において、アイドルトーンの悪影響を各チャネルで低減する。

【解決手段】ΔΣ型A/D変換器は、受けた信号を量子化して出力するための第1の量子化器55と、第1の量子化器55の出力信号をアナログ信号に変換して出力するための第1のD/A変換器56と、第1のアナログ入力信号と第1のD/A変換器56の出力信号との差を示す信号を出力するための第1の演算器51と、第1の演算器51の出力信号を積分した信号を出力するための第1の積分器52と、第1のディザ信号を生成するための第1のディザ回路と、第1の積分器52の出力信号に第1のディザ信号を加算した信号を第1の量子化器55へ出力するための第2の演算器54とを備える。

(もっと読む)

連続時間型多ビットΔΣADC回路

【課題】グリッジの発生を防止してS/N特性を良好にする。

【解決手段】加算器1と、加算器1から出力する信号を積分する積分器2と、積分器2の出力をを3ビットの出力デジタル信号に量子化する量子化器3と、量子化器3から出力する3ビットのデジタル信号を1サンプリングクロックだけ遅延させる遅延回路4と、遅延回路4から出力する3ビットの遅延デジタル信号をパラレル/シリアル変換およびPWM変調して2本の帰還PWM信号を生成するPWM回路5と、PWM回路5から出力する2本の帰還PWM信号を抵抗加算することで帰還アナログ信号に変換して加算器1に入力させる抵抗R2,R3とを備える。さらに、抵抗R2,R3と加算器1との間にグリッジキャンセル回路6を挿入し、抵抗R2,R3から出力する帰還アナログ信号に対してリタイミング処理を行う。

(もっと読む)

デジタルアナログ変換器、それを用いたΔΣ型アナログデジタル変換器およびそれを用いた電子機器

【課題】精度が改善されたΔΣ型アナログデジタル変換器を提供する。

【解決手段】D/A変換器40は、サイクルごとに入力されるデジタル入力信号DINをアナログ出力信号VOUTに変換する。各単位素子UCは、複数の候補値のいずれか取り得る制御データを受け、その値を示すアナログ信号を生成する。加算演算器44は、単位素子UCが生成したアナログ信号Vを加算し、アナログ出力信号VOUTを生成する。制御回路42は、サイクルごとに各単位素子UCに制御データを出力する。制御回路42は、デジタル入力信号の値をY、i(1≦i≦N)番目の単位素子UCに対する制御データの値をXiと書くとき、Y=Σi=1:NXiを満たすように各単位素子UCに対する制御データを生成する。制御回路42は、複数の候補値のうちのL個を(Lは自然数)循環対象値として管理し、各循環対象値を示す制御データを、N個の単位素子UCに循環的に割り当てる。

(もっと読む)

画像圧縮装置及び画像圧縮プログラム

【課題】網点画像のような隣接する画素間の濃度差が大きい画像において、復号後の画質劣化を抑えつつ符号化効率を向上させること。

【解決手段】画像圧縮部は、注目画素の対象ビット桁をそのままで下位ビットを全て‘0’又は‘1’にした値Aと、対象ビット桁を変更して下位ビットを全て‘0’又は‘1’にした値Bを算出して、注目画素の値と値Aの差の絶対値(第1誤差)と注目画素の値と値Bの差の絶対値(第2誤差)をそれぞれ算出し、第1誤差が第2誤差以下である場合は注目画素の対象ビット桁の値はそのままとし、第1誤差が第2誤差より大きい場合は注目画素の対象ビット桁の値を変更する。

(もっと読む)

積分器およびそれを備えたオーバーサンプリングA/D変換器

【課題】1個の演算増幅器で高次積分器を実現する。

【解決手段】積分器(100)は、演算増幅器(11)と、演算増幅器の反転入力端に接続された第1のフィルタ(12)と、演算増幅器の反転入力端と出力端との間に接続された第2のフィルタ(13)とを備えている。第1のフィルタ(12)は、直列接続されたn個の抵抗素子(121)と、抵抗素子の各接続点とグランドとの間に接続されたn−1個の容量素子(122)と、抵抗素子の各接続点とグランドとの間に接続されたn−1個の抵抗素子(123)とを有する。第2のフィルタ(13)は、直列接続されたn個の容量素子(131)と、容量素子の各接続点とグランドとの間に接続されたn−1個の抵抗素子(132)と、容量素子の各接続点とグランドとの間に接続されたn−1個の容量素子(133)とを有する。

(もっと読む)

ΔΣ変換器の制御値に基づいて電力増幅器を制御する送信機、プログラム及び方法

【課題】スイッチングアンプの素子数を増やすことなく、所望信号と量子化雑音との電力比を高くし、送信機の電力効率を高効率化することができる送信機等を提供する。

【解決手段】非一様量子化器を含む複数のΔΣ変換器と、キャリア周波数へ周波数変換する複数のミキサと、キャリア周波数信号を加算する加算器と、加算信号に対して電力増幅する電力増幅器と、電力増幅器へ電圧を供給する電源供給部と、送信すべきベースバンド信号の振幅値の確率密度関数に基づいて、非一様量子化器に対する閾値xk及び出力値qkを制御する制御部とを有する。電力増幅器は、加算信号に基づく出力電流に電流加算するスイッチングアンプを有する。電源供給部は、電力増幅器の出力電流が変化するように供給電圧を変化させる変圧部を有する。制御部は、電源供給部の変圧部に対して、各出力値qk間のステップ間隔Δkに基づいて供給電圧Vkを変化させるべく制御する。

(もっと読む)

複素2次積分器およびそれを備えたオーバーサンプリングA/D変換器

【課題】より少ない演算増幅器で複素2次積分器を実現する。

【解決手段】複素2次積分器(100)は、第1および第2の2次積分器(100I,100Q)と、これらを結合する第1および第2の結合回路(30,40)とを備えている。各2次積分器(100I、100Q)は、演算増幅器(10)と、4つの抵抗素子(11〜14)と、3つの容量素子(21〜23)とを備えている。第1の結合回路(30)は、演算増幅器(10)の反転入力端と出力端との間に挿入された直列接続された2つの容量素子(22,23)の一方(23)どうしを2つの抵抗素子(31,32)でクロス結合する。第2の結合回路(40)は、当該2つの容量素子の他方(22)どうしを2つの抵抗素子(41,42)でクロス結合する。

(もっと読む)

クロック信号の変化を通じて利得を制御するアナログ−デジタル変換器とそれを含むイメージセンサー及び電子システム

【課題】クロック信号の変化を通じて利得を制御するアナログ−デジタル変換器及びそれを含むイメージセンサーを提供する。

【解決手段】本発明のアナログ−デジタル変換器は、入力信号及びクロック信号が入力され、クロック信号に応答し、入力信号をシグマ−デルタ変調信号に変調して該変調されたデジタル出力信号を出力するシグマ−デルタモジュレータと、アナログ−デジタル変換時間に合わせ、クロック信号の周期毎にデジタル出力信号を累算して得た累算出力値を出力する累算器と、を備え、アナログ−デジタル変換時間に含まれるクロック信号のクロック数を可変することで、その利得が可変される。

(もっと読む)

部分的な複素変調フィルタバンク

【課題】高品質の操作を可能にする信号を出力するための効率的な概念と、歪が少ない状態で信号を削減するための効率的な概念とを提供する。

【解決手段】第1の実数サブバンド信号と第2の実数サブバンド信号とを含む複数の実数サブバンド信号を処理して少なくとも1つの複素サブバンド信号を提供する装置210であって、この装置は、実数中間サブバンド信号を出力するためのマルチバンドフィルタ204と、上記複数の実数サブバンド信号からの実数サブバンド信号と上記中間サブバンド信号とを結合することによって複素サブバンド信号を出力するための計算器215と、を備える。上記実数サブバンド信号の各信号に対し、その実数サブバンド信号に関連する中心周波数に従って指数mを割り当て、この指数mが増大するにつれて上記実数サブバンド信号をその信号に関連する中心周波数に従って配置する。

(もっと読む)

データ処理装置、データ処理方法、およびデータ処理プログラム

【課題】複数のデバイスのそれぞれに対し、各デバイスの復号性能に適したデータ量の符号化データを、処理負担を増大させることなく出力することができるデータ処理装置、データ処理方法、およびデータ処理プログラムを提供する。

【解決手段】データ処理装置は、連続する複数の画像データから、参照データと被参照データとの組み合わせを、データの出力先である複数のデバイスの性能情報に基づいて決定する(S1)。決定した組み合わせによって対応付けられている被参照データを参照して、参照データを画像圧縮符号化し、符号化データを生成する(S5)。データ処理装置は、生成した複数の符号化データのうち、出力先のデバイスの性能情報に対応する少なくとも1つの組み合わせに属する画像データの符号化データを、各々のデバイスに出力する(S6,S7)。

(もっと読む)

画像符号化装置、画像復号装置、画像符号化方法および画像復号方法

ビット深度に制限を有するエンコーダを利用しつつ、大きなビット深度の画像を符号化する画像符号化装置を提供する。画像符号化装置は、ビット深度が所定の大きさよりも大きい対象画像を符号化する画像符号化装置であって、対象画像をダウンコンバートすることにより、ビット深度が所定の大きさ以下のベース・ビュー画像を生成するダウンコンバータ(102)と、ベース・ビュー画像を符号化して、符号化したベース・ビュー画像を復号することにより再構築画像を生成するMVCエンコーダ(101)と、ダウンコンバートされる前の対象画像の各画素値の特性と、再構築画像の各画素値の特性との間の各差異から、ビット深度が所定の大きさ以下のノン・ベース・ビュー画像を生成する減算器(103)とを備え、MVCエンコーダ(101)は、さらに、ノン・ベース・ビュー画像を符号化する。  (もっと読む)

(もっと読む)

基本層及び拡張層を有する音声信号を検出する方法

【課題】 本発明は、二重層音声信号のために必要な電力を低減する効率的な解決策を提供する。

【解決手段】 音声信号は、BL及びELを有してもよい。ELはBL音声コンテンツの質を向上する付加情報を表す。このような2重層信号の復号化は、通常、BLデータの部分復号化する段階(21)を有する。BLの周波数ビンは復元され(22)、復元された周波数ビンはMDCT領域にマッピングされ(23)、それらは復号化されたELに加算され、逆整数MDCTを実行される。低複雑度復号化方法は、復号化されたELデータを逆マッピングする段階(45)、逆マッピングされたELデータを部分的に復号化されたBLデータに加算する段階(42)、及び逆BLフィルタ・バンクを用いて和をフィルタリングする段階、を有する。

(もっと読む)

量子化器の制御値を最適に決定するΔΣ変換装置、プログラム及び方法

【課題】量子化雑音が小さくなるように、量子化器の閾値xk及び出力値qkを最適に決定するΔΣ変換装置、プログラム及び方法を提供する。

【解決手段】ΔΣ変換装置において、非一様量子化器を含むΔΣ変換器と、ΔΣ変換器からの出力値qk(k=1,2,〜,N、N:量子化レベル)における発振を検出する発振検出部と、発振検出部を用いて、ΔΣ変換器の非一様量子化器に対する閾値xk及び出力値qkを制御する制御部とを有する。制御部は、非一様量子化器の閾値xk及び出力値qkを可変することによって、発振検出部を用いて、発振しない最大出力値qN-MAXを検出する最大出力値決定手段と、最大出力値qN-MAXを固定した状態で、閾値xkを、出力値qk〜qk+1の中間値に設定し、次に、出力値qkを、閾値xk-1〜xkの間の区間Qkにおける、ΔΣ変換器への入力信号の振幅値の確率密度関数で重み付けした重心に設定する制御値決定手段とを有する。

(もっと読む)

画像処理システムおよび画像処理プログラム

【課題】交流成分予測における画像の予測精度の一層の向上を図る。

【解決手段】領域特定部31は、対象ブロックSの参照領域として、ブロックT,L,B,R,BB,RRを特定する。処理済ブロックT,Lは、順次シフトによる処理が既に行われたブロックである。未処理ブロックB,Rは、順次シフトによる処理が未だ行われておらず、かつ、対象ブロックSと隣接したブロックである。未処理ブロックBB,RRは、順次シフトによる処理が未だ行われたおらず、かつ、対象ブロックSから未処理ブロックB,Rに至る方向において未処理ブロックB,Rと隣接したブロックである。予測処理部32は、対象ブロックSの平均画素値と、処理済ブロックT,L内に存在する処理済サブブロックの平均画素値と、未処理ブロックB,Rの平均画素値と、未処理ブロックBB,RRの平均画素値とを用いた交流成分予測によって、対象ブロックS内に存在するそれぞれの対象サブブロックの予測画素値を算出する。

(もっと読む)

動画像符号化装置および動画像復号装置

【課題】 量子化変換係数をスキャンして得られる係数データを可変長符号化テーブルを用いて符号化する符号化方法によって生成された符号化ビットストリームを正しく復号する。

【解決手段】 VLCテーブルグループ選択部107b6は、可変長復号化テーブルグループ群のうちから量子化変換係数の高周波成分を含むかどうかにより予め分割された所定の周波数領域毎に予め定められた1つの可変長復号化テーブルグループを選択し、VLCテーブル選択部107c10は、選択された可変長符号化テーブルグループの中から、符号化時に量子化変換係数をスキャンした際の零に続く零でない係数に応じて選択された可変長符号化テーブルに対応する可変長復号化テーブルを選択し、選択された可変長復号化テーブルを用いて、量子化変換係数をスキャンして得られる係数データを可変長復号する。

(もっと読む)

61 - 80 / 922

[ Back to top ]