Fターム[5J064BC08]の内容

圧縮、伸長、符号変換及びデコーダ (21,671) | 細部(回路)構成 (8,519) | 加減算 (922)

Fターム[5J064BC08]に分類される特許

101 - 120 / 922

スペクトル包絡情報量子化装置、スペクトル包絡情報復号装置、スペクトル包絡情報量子化方法及びスペクトル包絡情報復号方法

【課題】符号化データに原信号の特徴を精度良く反映させることができるスペクトル包絡情報量子化装置。

【解決手段】分類器207は、狭帯域−広帯域変換部200から入力される変換広帯域LSPパラメータを用いてクラス分類を行い、その分類されたクラスを示すクラス情報を多段階ベクトル量子化符号帳208内の切り換えスイッチ251へ出力する。多段階ベクトル量子化符号帳208は、初段符号帳250、切り換えスイッチ251、2段目符号帳(CBb)252、3段目符号帳(CBc)253および加算器254、255を備える。切り換えスイッチ251は、分類器207から入力されたクラス情報に対応付けされたサブ符号帳(CBa1〜CBan)を初段符号帳250の中から一つ選び、そのサブ符号帳の出力端子を加算器254に接続する。

(もっと読む)

データ伝送装置およびデータ伝送方法

【課題】

伝送媒体上を伝送するデータのトグル量が少なくする。

【解決手段】

予測器(14)は、データ入力端子(12)に先に入力した2値データ信号から、現在の入力値に対する予測値を算出する。減算器(16)は、データ入力端子(12)からの現在の2値データ信号から予測値を減算する。符号化テーブル(18)は、減算器(16)からの差分値を、0に近いほど2進値”1”となるビット数が少ない符号に変換する。排他的論理和(XOR)回路(20)は、符号化テーブル(18)の出力符号と、フリップフロップ回路(22)の出力(XOR回路(20)の直前の出力符号)との間の排他的論理和を計算し、計算結果が伝送データとしてデータバス(30)に出力される。

(もっと読む)

DEM(ダイナミック・エレメント・マッチング)

【課題】精度の高いΔΣ型AD型変換器を実現できるDEMを提供する。

【解決手段】ΔΣ変調器に使用される本願発明のDEMのアルゴリズムは、ΔΣ変調器を構成する量子化器、DA変換器の出力値に関係なく、DA変換器において使用開始するエレメントを所定の個数A個シフトさせることを特徴とする。Aとは1、又は、DA変換器のビット数N(Nは3以上の正の整数)に対して{A<2N/4}となる正の整数である。

(もっと読む)

デルタシグマA/Dコンバータ

【課題】高精度のデルタシグマA/Dコンバータの提供。

【解決手段】入力信号と出力側からの第1のフィードバック信号とに基づいて、第1の信号を生成する第1の積分回路と、前記第1の信号を第1の被変換信号に変換する第1の信号変換回路と、補償信号を生成し、当該補償信号を前記第1のフィードバック信号よりも早いタイミングで出力側からフィードバックされる第2のフィードバック信号に応じて出力するループ遅延補償回路と、前記第1の被変換信号と前記補償信号とを加算する加算回路と、前記加算回路からの出力信号に基づいて、デジタル信号を生成する比較器と、を備えたデルタシグマA/Dコンバータ。前記ループ遅延補償回路は、前記補償信号を生成する補償用信号変換回路を備え、前記補償用信号変換回路と前記第1の信号変換回路との変換係数の温度による変化率が実質的に等しいことを特徴とする。

(もっと読む)

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

音信号加工装置及び音信号加工方法

【課題】量子化雑音などの劣化音を含む入力音信号に対して、主観的に劣化音を感じにくく加工する音信号加工方法および音信号加工装置を提供する。

【解決手段】入力音信号としての復号音声の聴覚重み付け後のスペクトルを変形強度制御部で算出、その振幅の大きさ、スペクトルの連続性に基き、変形強度を算出する。信号変形部で、復号音声のスペクトルを求め、変形強度に基き振幅平滑化、位相擾乱付与を行い、信号領域に戻して変形復号音声とする。信号評価部で、復号音声を分析し背景雑音らしさを求め、これを加算制御値とする。重み付き加算部で、加算制御値が背景雑音らしいことを示す場合には、復号音声への重みを減らし、変形復号音声への重みを増やして加算し、出力音声とする。

(もっと読む)

ゲインコントロール回路及びそれを有する電子ボリューム回路

【課題】

ゲインの最小単位を小さくし且つ高精度にゲインを制御できるゲインコントロール回路とそれを有する電子ボリューム回路を提供する。

【解決手段】

入力信号のゲイン調整を行う増幅回路にゲイン制御信号を供給するゲインコントロール回路において,入力ゲイン値とカウント値とを比較し比較結果信号を生成する比較器と,比較結果信号に応じて,カウント値をアップカウント又はダウンカウントするカウンタと,カウント値を変調して,時分割で変化するゲイン制御信号を生成するゲイン変調回路とを有し,ゲイン変調回路は,時分割で変化するゲイン制御信号に対応するゲインを時間平均したゲインが,カウント値に基づくゲインに一致するようにカウント値を変調する。

(もっと読む)

A/D変換回路を内蔵した半導体集積回路

【課題】チップサイズの増大を抑制しつつ高精度のA/D変換が可能なA/D変換器を内蔵した半導体集積回路を提供する。

【解決手段】A/D変換回路は、初段側のローカルD/A変換回路17と、後段側のローカルD/A変換回路18と、高精度が必要な初段側のローカルD/A変換回路17に必要な基準電圧を生成する初段側の基準電圧生成回路22a、22b、22cと、高精度が不必要な後段側のローカルD/A変換回路18に必要な基準電圧を生成する後段側の基準電圧生成回路21a、21b、21cを具備する。後段側の基準電圧生成回路21a、21b、21cの出力端子には比較的小さな安定化容量Ca1、Cb1、Cc1が接続され、初段側の基準電圧生成回路22a、22b、22cの出力端子には比較的大きな安定化容量Ca2、Cb2、Cc2が接続される。

(もっと読む)

特に画像,映像,及び/又は音声のデジタルファイルを処理する方法

何らかの音声,画像及び/又は映像ファイルのデジタルデータを,色層ごと及び/又は音声チャネルごとに整列させる段階と,位置Nの各圧縮値VCNを,元のファイルの同位置Nの値VNから,先に計算された所定数の連続する圧縮値(VCN−1,VCN−2,…)を減算することによって得るアルゴリズムを用いる圧縮段階と,位置Nの各復元値(VDN)を,圧縮ファイルの同位置の値VCNに所定数の連続する圧縮値(VCN−1,VCN−2,…)を加算することによって得るアルゴリズムを用いる復元段階とを含む画像,映像及び/又は音声のデジタルファイルを処理する方法。 (もっと読む)

短縮化処理を有するシグマデルタ変調器及びその適用

回路段間でビット短縮化を行う多段シグマデルタ変調器を提供する。ビット短縮化により後段の回路段で処理する必要があるビット数を減少させ、これにより高速な応答時間を達成する。ある実施例では、帰還ループの利得を、ビットの短縮化を補償するように選択し、シグマデルタ変調器が安定状態で動作するようにする。  (もっと読む)

(もっと読む)

信号変換システム

【課題】従来のシグマ−デルタ変換器が持っているアイドルトーン問題、フラットゾーン問題等を改善する。

【解決手段】信号変換システムは、補償モジュールと、補償モジュールに接続されている変換モジュールとを備えている。補償モジュールは、動的な信号に従って第1の補償信号を調整して、第1の補償信号を第1の入力信号に加えるために動作可能である。補償モジュールは、また、出力信号から、動的な信号の蓄積を表す、第2の補償信号を減算するために動作可能である。変換モジュールは、第1の入力信号と第1の補償信号の合計である第2の入力信号を受信して、この第2の入力信号を出力信号に変換するために動作可能である。

(もっと読む)

AD変換装置、AD変換装置を用いた電流検出器及び電流検出器を用いたディジタルサーボ制御装置

【課題】ΔΣ型AD変換器のディジタル信号のサンプリング回数を増やすことができる回路構成とし、精度の良いAD変換装置および電流検出器を提供する。

【解決手段】ΔΣ型AD変換器511がタイミング生成回路20とAD変換時間計測カウンタ221とAD変換時間保持部231とAD変換データセレクタ241とAD変換完了信号セレクタ251を備え、AD変換データ生成部が181,182,・・・,18mと複数チャネル並列化され、1チャネルあたりのディジタル信号のサンプリング回数を増やす。

(もっと読む)

復号装置、及びプログラム

【課題】指数ゴロム符号を復号する復号装置を提供する。

【解決手段】入力される指数ゴロム符号のセパレータ「1」を検出する第1の検出部11、セパレータの検出までのプリフィックスの0の数をカウントアップし、セパレータの検出後のサフィックスの符号の数を、カウントアップ後のカウント値からカウントダウンするカウンタ12、サフィックスの全符号のカウントダウンの終了を検出する第2の検出部14、カウントアップ後のプリフィックスの0の数(=n)を用いて2n−1を計算する計算部18、セパレータの検出からカウントダウンの終了の検出まで、サフィックスの符号列を読み込む読み込み部16、計算結果と読み込まれた符号列とを加算した復号結果を出力する加算器20を備え、カウンタ12は、カウントダウンの終了の検出後、次のプリフィックスの0の数のカウントアップを開始する。

(もっと読む)

ΔΣ変調回路およびシステム

【課題】 2つの積分器を用いて、安定かつ、3次以上のノイズシェーピング特性を有するΔΣ変調回路を簡易なフィードバック回路を用いて形成する。

【解決手段】 ΔΣ変調回路は、直列に接続された第1積分器および第2積分器と、第2積分器の出力に接続される量子化器と、量子化器の出力から第1および第2積分器の入力へのフィードバック経路に配置された遅延器を有する。また、ΔΣ変調回路は、量子化器の出力と入力との差分を生成する加算器と、加算器の出力を第1および第2積分器のいずれかの出力に接続する遅延器を含むフィードバック回路を有する。これにより、2つの積分器を用いて3次以上のノイズシェーピング特性を有するΔΣ変調回路が構成できる。第1積分器の入力にフィードバックしたΔΣ変調回路に比べ、フィードバック回路の回路規模を小さくでき、ΔΣ変調回路が搭載される半導体のチップサイズを削減できる。

(もっと読む)

デルタシグマAD変調器

【課題】電源電圧を低電圧動作させた場合に、トラッキング方式によりデルタシグマAD変調器より出力するビット数より少ない複数のコンパレータで量子化器を構成しつつ、コンパレータの判定ばらつき範囲を維持することで、回路面積、消費電流を改善しながら、SNR特性を維持する。

【解決手段】マルチビットの量子化器4の入力端に、可変ゲイン回路2と、オフセット量加算回路3とを設け、1サンプル時間ごとに、量子化器4が飽和動作とならずに動作するように、出力処理回路7の出力デジタルデータと、オフセット制御回路8の前回の制御信号とをもとにオフセット加算回路3のオフセット信号のレベルを調整するトラッキング制御を行う。その結果、出力処理回路7から量子化器4のビット数よりオフセット加算回路3によるオフセット値制御分だけビット数の多い出力デジタルデータを出力処理回路7から1サンプル時間ごとに出力する。

(もっと読む)

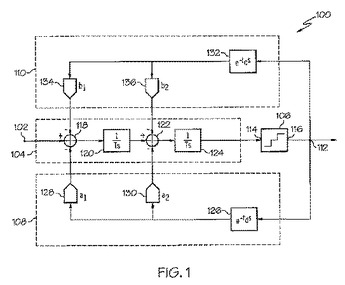

独立した遅延を有する複数のフィードバック経路を有する連続時間型シグマデルタ変調器

連続時間型シグマデルタ変調器の装置を提供する。シグマデルタ変調器(100、200、300)は、アナログ信号をデジタル値に変換するように構成された量子化器(106、206、306)を備える。主フィードバック構成(108、208、308)は量子化器に接続されており、デジタル値を第1遅延期間だけ遅延させ、この遅延値に基づき主フィードバック信号を生成する。補償フィードバック構成(110、210、310)は量子化器に接続されており、デジタル値を第2遅延期間だけ遅延させ、この遅延値に基づき補償フィードバック信号を生成する。フォワード信号構成(104、204、304)は、入力信号、主フィードバック信号および補償フィードバック信号に基づき量子化器におけるアナログ信号を生成する。第2遅延期間は第1期間から独立しており第1期間によって影響されず、第2遅延期間は補償フィードバック信号が第1遅延期間を補償するように選択される。  (もっと読む)

(もっと読む)

A/D変換器

【課題】ΔΣ型A/D変換器の長所を備え、且つアナログ部品への精度要求の低い低コストのA/D変換器を提供する。

【解決手段】入力アナログ信号とフィードバック信号との差分信号を生成する差分器と、前記差分信号を積分する積分器と、基本クロックを分周して得られる変換クロックに同期して、前記積分器の出力レベルに応じたデューティを有するパルス信号を生成するレベル/デューティ変換器と、前記基本クロックに同期して、前記パルス信号をオーバーサンプリングするオーバーサンプラと、前記オーバーサンプラの出力信号のデューティに応じたレベルを有する信号を前記フィードバック信号として前記差分器に出力するデューティ/レベル変換器と、前記オーバーサンプラの出力信号に対してデューティ/レベル変換処理及びデシメーションフィルタリング処理を行うデジタルフィルタとを備える。

(もっと読む)

量子化LSPパラメータ動的特徴抽出器及び量子化LSPパラメータ動的特徴抽出方法

【課題】モード情報を符号化/伝送することなく、音源部の符号化モードの切換を行うことが可能となり、音声信号を高能率に符号化すること。

【解決手段】加算器606は、現在の処理単位時間における平滑化量子化LSPパラメータと1つ前の処理単位時間における平滑化量子化LSPパラメータとの差を算出する。2乗和算出手段607は、加算器606の出力について次数毎の差の2乗和を計算する。AR型平均値算出手段611は、雑音区間における平均的LSPパラメータを算出する。加算器612は、現在の処理単位時間における量子化LSPパラメータと雑音区間における平均的量子化LSPパラメータとの差を次数毎に算出する。2乗和算出手段613は、加算器612について次数毎の2乗和を算出する。音声区間検出手段619は、現在の処理単位時間における入力信号が音声区間であるか否かの判定を行う。

(もっと読む)

バンドパス・デルタシグマA/D変換器

【課題】中心周波数が異なる信号が受信されても、受信信号帯域におけるSN比を高めて、受信機全体の感度を高めることができるようにする。

【解決手段】減算器1から出力された差分信号を積分する積分回路2と、積分回路2により積分された差分信号を量子化する量子化器3と、量子化器3から出力された量子化信号をアナログ信号に変換するD/A変換器4と、D/A変換器4から出力されたアナログ信号を微分し、その微分の結果を帰還信号として減算器1に出力する微分回路5とを設け、切換回路7が、積分回路2と微分回路5から構成される共振回路6の共振周波数frを切り換える。

(もっと読む)

音声符号化用ゲイン平滑化

【課題】音声信号は、かなりの量の雑音コンテンツを含む。雑音を符号化する従来の方法は、雑音を適切にモデル化をすることがしばしば困難であり、望ましくない割り込みや不連続性の結果を生じ、音声中もそうである。従来の符号励起線形予測符号器のような、合成による分析(analysis by synthesis)の音声符号器は、特に低減されたビットレートにおいては適切に背景雑音を符号化できない。そこで最適な音声コーデックを提供する。

【解決手段】ブロック527において、デコーダ処理回路は、ゲインを修正し、適応符号帳515からのベクトルの貢献をエンファシス化する。ブロック529において、励起スペクトルを平坦化にする目標と結合したベクトルに適応チルト補償を適用する。デコーダ処理回路は、平坦化された励起信号を使って、ブロック531において合成フィルタリングを行う。

(もっと読む)

101 - 120 / 922

[ Back to top ]