Fターム[5J098AA02]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | バイポーラトランジスタ (79)

Fターム[5J098AA02]に分類される特許

1 - 20 / 79

制御回路および位相変調器

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

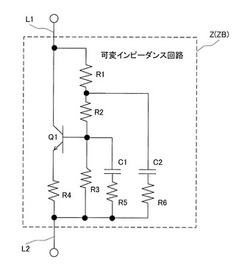

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

再帰型フィルタ回路

【課題】再帰フィルタ回路のエミッタフォロア回路の数を低減し、回路規模が小さい再帰型フィルタ回路を提供する。

【解決手段】バイポーラトランジスタ(Tr)101を流れる電流Iinとフィードバック電流Ifbとを加算して電流Iを生成するノードB、電流Iをテール電流とし、ゲインを変更する制御信号が入力されるバイポーラTr106及びバイポーラTr103を含む差動対100、バイポーラTr106に流れる電流を電圧に変換する抵抗素子105を含む可変ゲイン増幅部、変換後の電圧を増幅して出力信号を生成するバイポーラTr113を含む出力部115、可変容量素子104を含むハイパス部、ハイパス部から出力された信号をバッファリングする回路114、バッファリングされた信号を、可変容量素子109を介して周波数帯域制限するローパス部を含む移相部によって再帰型フィルタを構成する。

(もっと読む)

アクティブポリフェーズフィルタ

【課題】大電力を入力しても歪の小さいアクティブポリフェーズフィルタを提供する。

【解決手段】npnトランジスタQ1、Q2、Q4及びQ5と、npnトランジスタQ6、Q7、Q4及びQ5は、各々トランスリニアループを形成している。また、npnトランジスタQ2及びQ3と、npnトランジスタQ7及びQ8は各々カレントミラー回路を形成している。こうして、npnトランジスタQ1とQ3の各々のコレクタ電流の差と、npnトランジスタQ6とQ8の各々のコレクタ電流の差とが、いずれも、平衡な高周波入力の電流に等しくなる。このような2組の差動入力を、ポリフェーズフィルタ部10の4入力とすることで、ポリフェーズフィルタ部10の4出力から、偶数次成分の抑制された、位相がπ/2異なる差動出力を得ることができる。

(もっと読む)

可変利得増幅器及びそれを用いた移相器

【課題】 増幅素子の電流特性の非線形性を改善し、振幅設定精度を向上させた可変利得増幅器及びそれを用いた移相器を提供する。

【解決手段】 第2定電流源16からの電流を入力電流とし、この入力電流に比例した電流を第2カレントミラー回路17を介してエミッタ電流とする第7バイポーラトランジスタ18と、この第7バイポーラトランジスタ18の前記エミッタ電流に相応する第7バイポーラトランジスタ18のベース電流を入力電流とし、この入力電流に比例した電流を出力電流として第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれのベースに入力する第3カレントミラー回路20とを備え、第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれの入力電流に対する出力電流を線形とし、第2定電流源16からの電流に比例した利得を可変するようにした。

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

移相器

【課題】広帯域に位相差が異なる信号を生成する移相器を得る。

【解決手段】移相器は、入力される位相が180度異なる2個の信号から上記2個の信号と位相の異なる複数の信号を生成する移相器において、上記2個の信号から位相がそれぞれ90度異なる4個の信号を生成する90度移相器と、上記位相がそれぞれ90度異なる4個の信号を位相を変えずに増幅する差動増幅器および上記4個の信号と位相がそれぞれ45度異なる4個の信号を生成する位相差45度を得る差動増幅器を有し、位相差45度の8個の信号を生成する位相差45度を生成する移相器と、を備える。

(もっと読む)

差動電流信号を単一終結信号に変換する回路

【課題】差動電流信号を単一終結信号に変換するミキサ回路を提供する。

【解決手段】多くの適用が差動電流信号の単一終結信号への変換を必要とする。存在しているアプローチで遭遇する欠点は、乏しい変換効率、制限された帯域幅、および大きなサイズを含む。開示された変換器は、小さなサイズおよび作動の広い帯域幅を有している高効率のユニットを得るために能動装置を使用する。

(もっと読む)

信号伝達装置

【課題】より簡素な構成でありながら、動作信頼性に優れる信号伝達装置を提供する。

【解決手段】入力信号電流が流れることにより入力信号磁場を生ずるプライマリコイル10と、バイアス電流が流れることによりバイアス磁場を生ずるバイアスコイル30と、センシング電流が流れることによりセルフバイアス磁場を生ずると共に、入力信号磁場、バイアス磁場およびセルフバイアス磁場に応じて抵抗変化を生ずるMR素子21A〜21Dを含む検出回路20とを備える。バイアス磁場およびセルフバイアス磁場は、MR素子21A〜21Dにおける磁化自由層に対して同じ方向に印加される。よって、セルフバイアス磁場がバイアス磁場と同様の機能を発揮する。これらのバイアス磁場およびセルフバイアス磁場により、検出回路20の動作安定性が向上する。

(もっと読む)

周波数可変フィルタ回路

【課題】簡素な回路構成で実現でき、小型化可能な周波数可変フィルタ回路を提供すること。

【解決手段】インダクタ12と可変容量素子14(第2の並列容量素子)とが並列に接続された並列共振回路20と、複数の可変容量素子10、11及び13からなるインピーダンス調製回路21と、2つのエミッタフォロワ回路16、18からなるインピーダンス調整回路22と、を備えて周波数可変フィルタ回路1を構成し、可変容量素子10の容量値と可変容量素子11(及び可変容量素子10と可変容量素子13)の容量値との比を調整することにより、並列共振回路20の入力側のインピーダンスを所望値に調整し、エミッタフォロワ回路16及び18によって並列共振回路20の出力側のインピーダンスを所望値に調整することにより、簡素な構成で小型化可能の周波数可変フィルタ回路を構成した。

(もっと読む)

半導体集積回路

【課題】電源電圧の変化に依存する内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】半導体集積回路は校正回路200を具備し、内蔵容量70:151は容量とスイッチを有する。V・I変換器30、20は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧を比較する。校正動作の間に時間積分と電圧比較が実行され、その結果はラッチ90に格納される。校正動作の完了時のラッチ90の格納結果に従って、内蔵フィルタ150の周波数特性が決定される。V・I変換器30、20のスイッチ素子SW0のNチャンネルMOSトランジスタのゲートに、校正動作の間に安定化電圧VREFが供給される。

(もっと読む)

サーキュレータ

【課題】アイソレーション特性に優れたサーキュレータを実現すること

【解決手段】ポート2に接続されたアンテナ19とダミー負荷15はともに50Ωである。分配回路10の入力端であるポート1に入力された信号は、逆相で等振幅に分配され、一方は第1ベース接地増幅器11、第1整合回路16、第3ベース接地増幅器13を介して合成器18に入力され、他方は第2ベース接地増幅器12、第2整合回路17、第4ベース接地増幅器14を介して合成器に入力される。ここで、アンテナ19のインピーダンスの変動は、第2ベース接地増幅器12の電流源の電流量と、第2整合回路17の並列可変キャパシタ119のキャパシタンスとを制御することで補償することができる。そのため、合成器18において第3ベース接地増幅器13の出力と第4ベース接地増幅器14との出力は打ち消され、ポート3からは出力されない。

(もっと読む)

フィルタ回路

【課題】平滑用コンデンサに対する充電電流及び放電電流による時定数を大きくした場合であっても、平滑用コンデンサの体格の大型化や、オフセット電圧の増加を抑制することが可能なフィルタ回路を提供する。

【解決手段】入力電圧とフィルタ処理電圧との電圧差に応じた電流を、カスコード型カレントミラー回路を利用して減衰させて、平滑用コンデンサC1の放電電流I11及び放電電流I12を発生させる。さらに、平滑用コンデンサC1の充電電流I12の一部となるベース電流Ib1’を流すトランジスタT23を、トランジスタT24と抵抗R13,R14からなる回路により、フィルタ回路10の後段回路と分離する。

(もっと読む)

半導体集積回路

【課題】 内蔵フィルタの周波数特性の不所望な変化を軽減すること。

【解決手段】 半導体集積回路は校正回路200を具備して、内蔵容量70:151は、複数の容量およびスイッチを有する。V・I変換器20、30は基準電圧を電流に変換して、電流に応答する時間積分器40、50は容量70の充電または放電の時間積分を実行して、電圧比較器80は基準電圧と内蔵容量70の端子電圧とを比較する。校正動作の間に複数回の時間積分と複数回の電圧比較が順次に実行されて、順次に生成される複数回の電圧比較の結果はラッチ90に順次に格納される。校正動作の完了時点のラッチの格納結果に従って、内蔵容量70:151の複数のスイッチの各オン・オフ制御と内蔵フィルタ150の周波数特性とが決定される。V・I変換器は、スイッチ素子SW0を含む。内蔵容量70:151の複数のスイッチとV・I変換器のスイッチ素子は、MOSトランジスタである。

(もっと読む)

終端抵抗調整回路およびバスシステム

【課題】USB2.0対応の半導体デバイスに内蔵されて、終端抵抗としてHigh Speedモードでの終端抵抗の規定を満足し、データ・ドライバとしてもFull Speedモードでの出力インピーダンスの規定を満足する終端抵抗調整回路を提供すること。

【解決手段】ドライバと、該ドライバの出力端とバスとの間に接続される抵抗素子とを備えて構成される出力/終端ユニットが並列に複数備えられる出力/終端部と、出力/終端ユニットと同一の構成を有しドライブ状態に維持されるモニターユニットと、モニターユニットに備えられる抵抗素子の一端に接続され、基準電流を流す電流源と、モニターユニットを流れる基準電流に応じてモニターユニットに備えられる抵抗素子の一端に出力されるモニター電圧に基づいて、出力/終端部においてドライバがドライブ状態となることに応じて終端抵抗を構成する出力/終端ユニットの構成数を調整する制御部とを備える。

(もっと読む)

アクティブバラン回路

【課題】アクティブバラン回路をMMIC化が容易な小型の構成にする。

【解決手段】平衡入力の一方を増幅し180度位相が回転した信号を取り出すN形電界効果トランジスタを有する第1の増幅回路と、平衡入力の他方を増幅し同位相の信号を取り出すP形電界効果トランジスタを有する第2の増幅回路と、第1および第2の増幅回路の出力信号を合成して不平衡出力として取り出す合成回路を備えたものである。

(もっと読む)

1 - 20 / 79

[ Back to top ]