Fターム[5J098AD24]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 性能向上 (128) | 消費電力の低減 (56)

Fターム[5J098AD24]に分類される特許

1 - 20 / 56

直交信号生成回路、直交信号生成回路の調整方法、及び無線通信装置

【課題】高周波の広い範囲で周波数が高速で切り替わり、正確に位相が90度異なる直交信号を消費電力が少ない回路で生成する。

【解決手段】可変利得アンプ9によって増幅した信号を、ポリフェイズフィルタ1を通すことで、大まかに位相差が90度となる直交信号を生成する。ディジタル制御回路8からのディジタル信号で制御された可変利得アンプ2,3により、直交信号を増幅する。可変利得アンプ2,3の出力信号の振幅を振幅検出器4,5によって検出し、可変利得アンプ2,3の出力信号の振幅が等しくなるように、可変利得アンプの利得をディジタル制御回路8によって疎調整する。この疎調整に加えて、後述する微調整を行うことで、可変利得アンプ2,3の出力信号の振幅を等しくする。

(もっと読む)

半導体装置

【課題】省面積化されたローパスフィルタを備える半導体装置を提供する。

【解決手段】第1のノードと第2のノードとの間に接続され、印加される電圧に応じて内部容量が変化する可変容量素子と、第1のノードと第2のノードとの間に可変容量素子と並列に接続される電圧増幅部とを備え、電圧増幅部は、第1のノードと電気的に接続される増幅器と、増幅器の出力の電圧をシフトさせるレベルシフト回路とを含み、レベルシフト回路の出力は第2のノードと電気的に接続される。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

フィルタ装置

【課題】少ない電力でフィルタリング処理を行うことのできるフィルタ装置を提供する。

【解決手段】スイッチ制御部13は、動作フェーズにおいて、クロック制御信号φ1をクロック制御信号φの8クロックのうち1クロック、つまり1/8の時間だけ電力供給スイッチ17を電気的接続状態にする。次に、スイッチ制御部13は、クロック制御信号φ2をクロック制御信号φの8クロックのうち1/2クロック、つまり1/16の時間だけ信号入力スイッチ12を電気的接続状態にする。これ以外の時間を休止フェーズとして電気的接続状態が間欠的になるように各スイッチを切り換え制御することによって、フィルタリング処理で消費する電力を抑えることができる。

(もっと読む)

フィルタ自動調整回路及び方法並びに無線通信装置

【課題】調整機能を有する複数のフィルタにおいて、高い調整精度を有し、かつ低消費電流化が容易なフィルタのバラツキ調整を可能にする。

【解決手段】位相差検出器104により、複数のモードの切り替えを有する基準フィルタ103における前後の位相差をカウンタ105にてカウントし、基準フィルタ103のバラツキを検出する。その際、主フィルタ109を調整する時には基準フィルタ103を第1のモードに設定し、主フィルタ111を調整する時には基準フィルタ103を第2のモードに設定することで、複数の主フィルタ109,111に対して、より精度の高いフィルタ調整を行う。検出結果から得られる主フィルタ109の調整結果はレジスタ108に、主フィルタ111の調整結果はレジスタ110に保持し、調整後はフィルタ調整に関する部材をすべて動作停止し、低消費電力化を図る。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

フィルタ回路

【課題】高速でかつ低消費電流であり、MOSトランジスタのしきい値電圧の絶対値が低い場合でも入力信号レベルを大きくすることができるフィルタ回路を提供する。

【解決手段】ゲートから信号を入力するMOSトランジスタ(Tr)1、Tr2、ドレインがMOSトランジスタ1のソースに接続され、ゲートがMOSトランジスタ2のソースに接続されるTr3、ドレインがTr2のソースに接続され、ゲートがTr1のソースに接続されるTr4、Tr3のソースに電流を供給する電流源5、Tr4のソースに電流を供給する電流源6、Tr1〜Tr4のソースの各々に接続されるコンデンサ7、8を含むフィルタ回路に、Tr3、Tr4の動作点が飽和領域内の線形領域に近い側から遠い側に向かう方向にシフトするように電圧を印加する電圧源101、102を設ける。

(もっと読む)

増幅装置、センサモジュール

【課題】増幅装置にバンドパスフィルタを持たせる。

【解決手段】ローパスフィルタ回路11は、センサ信号(SIN)が供給される第1の入力端子と、第2の入力端子と、出力信号(SOUTP)を出力するための出力端子とを有する。ローパスフィルタ回路(12)は、ローパスフィルタ回路(11)の第2の入力端子に接続された入力端子と、出力端子とを有する。ローパスフィルタ回路(13)は、ローパスフィルタ回路(12)の出力端子に接続された入力端子と、出力信号(SOUTN)を出力するための出力端子とを有する。

(もっと読む)

遅延回路および半導体装置

【課題】入力信号を遅延させ出力する遅延回路において、動作時の消費電流低減をはかる。

【解決手段】遅延回路100の端子202に、Pチャネル型MOSトランジスタ105を介して容量素子107を接続する。NAND回路104は、入力端子が、遅延回路100の入力端子201とインバータ103へ接続され、出力端子がPチャネル型MOSトランジスタ105のゲート端子へ接続される。インバータ103は、入力端子が遅延回路100の出力端子へ接続される。Pチャネル型MOSトランジスタ105は、遅延回路100の出力信号がLレベルからHレベルに遷移することに応答して、端子202と容量素子107を電気的に非接続とする。

(もっと読む)

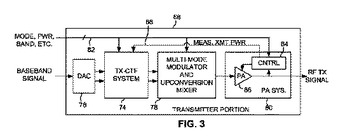

プログラム可能送信連続時間フィルタ

プログラム可能電流の送信連続時間フィルタ(TX−CTF)システムは無線周波数(RF)送信機に含まれ得る。TX−CTFの入力はベースバンド送信信号を受信することができ、TX−CTFの出力はアップコンバージョンミキサに供給されて、送信用のRFに変換され得る。TX−CTFは、フィルタパラメータをともに規定する増幅回路および受動回路を含む。TX−CTFはさらに、プログラム可能バイアス電流を増幅回路に供給するプログラム可能電流回路を含む。TX−CTFシステムはまた、1つ以上の送信機制御信号を受信し、これに応じて、TX−CTFに供給されるバイアス電流を制御する信号を生成する制御論理を含む。  (もっと読む)

(もっと読む)

方向性結合器及び送受信装置

【課題】伝送信号の損失を低減させる方向性結合器を提供する。

【解決手段】入出力端子101〜104と、入出力端子101と入出力端子102との間に接続され、与えられた信号の位相を90度シフトして出力する移相手段105と、入出力端子103と入出力端子104との間に接続され、与えられた信号の位相を90度シフトして出力する移相手段106と、入力が入出力端子103に接続され、出力が入出力端子101に接続された入出力インピーダンスが高い増幅器107と、入力が入出力端子104に接続され、出力が入出力端子102に接続された入出力インピーダンスが高い増幅器108と、を備える。

(もっと読む)

Gm−Cフィルタ回路及びこれを用いた送受信機

【課題】カットオフ周波数の補正動作中における後段回路の異常動作や電力浪費を解消することが可能なGm−Cフィルタ回路の提供。

【解決手段】Gm−Cフィルタ回路100は、カットオフ周波数の補正動作中に後段回路200への電力供給を停止させる電源遮断部(スイッチ112とこれを制御するフィルタ制御回路110)を有して成る構成とされている。

(もっと読む)

帯域通過フィルタ

【課題】ソースフォロワ回路をベースにした帯域通過フィルタを提供する。

【解決手段】入力信号を入力するMOSトランジスタ101、102、ドレインがMOSトランジスタ101のソースに接続されるMOSトランジスタ103、ドレインがMOSトランジスタ102のソースに接続されるMOSトランジスタ104を含み、MOSトランジスタ103のゲートがMOSトランジスタ104のドレインに接続し、MOSトランジスタ104のゲートがMOSトランジスタ103のドレインに接続されるトランジスタ対、電流源105、106、コンデンサ107、108、MOSトランジスタ101のソースの出力信号とMOSトランジスタ103のソースの出力信号とを加算する加算器109、MOSトランジスタ102のソース端子の出力信号とMOSトランジスタ104のソース端子の出力信号とを加算して出力する加算器110とによって帯域通過フィルタを構成する。

(もっと読む)

多分岐信号出力装置

【課題】フォトMOSリレーのリーク電流を減少させ、また、ノイズが混入し難く、かつ、消費電力を低減できる多分岐信号出力装置を提供する。

【解決手段】経路選択部40の先端に第1のスイッチ部41を、第1のスイッチ部41と共通電位点の間に第2のスイッチ部42を設け、スイッチ部内のスイッチ両端の電位が等しくなるように、選択的に信号と同じ電圧を印加する。また、信号が入力されるブロックのガードの電位を経路選択部40のガード電位にし、信号が入力されないブロックのガードの電位を固定電位とすると共に、信号が入力されないブロックに接続される線路の一部を、経路選択部40のガード電位とする。

(もっと読む)

Gm−Cフィルタをチューニングする装置および方法

チューナブルGm−Cフィルタを制御する装置であって、出力増幅器(304)の帰還符号を切り換えることによって自励発振器として再構成することのできるフィルタと、キャリブレーション構成においてフィルタの出力を検知するディジタルコントローラ(42)と、フィルタを含む相互コンダクタンス増幅器(310、320)のgm入力にアナログ制御信号(48)を提供するDAC(44)とを備える。 (もっと読む)

差動単相変換回路

【課題】差動単相変換回路におけるチップ面積の縮小又は同相ノイズ信号の除去又は電力損失の低下を図る。

【解決手段】差動信号が入力され単相信号が出力される差動単相変換回路10であって、差動信号の一方が入力される制御端子、第1端子、及び第2端子を有する第1トランジスタM2と、接地された制御端子、第1トランジスタの第1端子に接続される第2端子、及び差動信号の他方が入力されるとともに、出力信号が出力される第1端子を有する第2トランジスタM3とを有するカスコード増幅器、第1トランジスタの第2端子に接続される位相調整用容量C2、及び、第1トランジスタの第2端子に接続される電流源M1、を備える差動単相変換回路が提供される。

(もっと読む)

電流方式ローパスフィルタ

【課題】回路規模の小さい電流方式ローパスフィルタを提供する。

【解決手段】ローパスフィルタ10は、入力端子12と、出力電圧発生ノード16と、電源Vccから入力端子12に定電流Iconst1を供給する定電流源48と、電源Vccから出力電圧発生ノード16に定電流Iconst2を供給する定電流源50と、出力電圧発生ノード16に接続された入力を有するボルテージフォロワ回路34と、ボルテージフォロワ回路34の出力と入力端子12との間に接続された抵抗36と、出力電圧発生ノード16に接続された容量20と、ベース接地トランジスタ62と、カレントミラー回路28と、ボルテージフォロワ回路34の出力に接続された出力端子14とを備える。

(もっと読む)

誘導結合通信におけるインダクタンス補償方法及び装置

【課題】

本発明は、誘導結合(inductive coupling)送受信装置に関する。

【解決手段】

本発明の一実施例による誘導結合送受信装置は、データを送信及び/又は受信する誘導結合送受信器と、前記誘導結合送受信器に接続されたインダクタ(inductor)と、前記誘導結合送受信器及び前記インダクタに接続されて前記インダクタのインダクタンス(inductance)変化を補償する共振補償装置を含む。

(もっと読む)

半導体装置

【課題】半導体装置の受信部に小占有面積と消費電力が小さく且つ良好な受信品質とを得る。

【解決手段】受信して周波数変換された信号のDCオフセットを除去するハイパスフィルタ(10,15)は、CRフィルタを有し、CRフィルタの抵抗素子に流れる電流を選択的に増やすことによってハイパスフィルタの入力インピーダンスを大きくするブートストラップ回路(36)を備える。WCDMA又はHSDPA方式に応じてハイパスフィルタの遮断周波数を切換える。WCDMAによる受信のときはブートストラップ回路を非活性として遮断周波数を高くする。HSDPAによる受信のときはブートストラップ回路を活性として遮断周波数を低くする。CRフィルタ回路の抵抗素子に電流を流すブートストラップ回路を採用することによりCRフィルタ回路のチップ占有面積の増大を抑えて低いカットオフ周波数を実現することができる。

(もっと読む)

1 - 20 / 56

[ Back to top ]