Fターム[5J098CA01]の内容

能動素子を用いた回路網 (5,588) | 周波数選択回路網の機能 (352) | フィルタ (330)

Fターム[5J098CA01]の下位に属するFターム

LPF (160)

HPF (46)

BPF (78)

BEF、ノッチフィルタ、トラップフィルタ (20)

Fターム[5J098CA01]に分類される特許

1 - 20 / 26

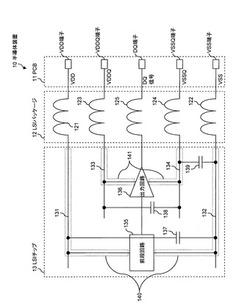

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

増幅回路、ジャイレータ回路、信号を増幅するためのフィルタ・デバイス及び方法

【課題】周波数に依存しない伝達特性が改善された増幅器、及びジャイレータ回路の提供。

【解決手段】位相シフタ部2に接続されたトランスコンダクタ・デバイス1を備えた増幅回路A1。位相シフタ部2は、位相シフトが調整可能で、入力信号の周波数に少なくとも部分的に依存するインピーダンスを有している。使用時に、調整可能な位相シフトは、トランスコンダクタ・デバイス1の位相シフトと実質的に反対の値となる様に調整され、実施形態として、位相シフタ部2は、キャパシタ・デバイスCと可調抵抗デバイスRとを含み、可調抵抗デバイスRは、抵抗値制御信号を受信する入力接点Rin、キャパシタ・デバイスに接続された第1の出力接点Rout1、及びトランスコンダクタ・デバイスに接続された第2の出力接点Rout2を有する増幅デバイスRを含み、増幅回路A1は更に、抵抗値制御信号を増幅デバイスの入力接点に供給する制御デバイスを備えている。

(もっと読む)

Gm−Cフィルタをチューニングする装置および方法

チューナブルGm−Cフィルタを制御する装置であって、出力増幅器(304)の帰還符号を切り換えることによって自励発振器として再構成することのできるフィルタと、キャリブレーション構成においてフィルタの出力を検知するディジタルコントローラ(42)と、フィルタを含む相互コンダクタンス増幅器(310、320)のgm入力にアナログ制御信号(48)を提供するDAC(44)とを備える。 (もっと読む)

フィルタ回路および半導体装置

【課題】プロセスばらつき、温度・電圧変動に依存することなく一定のカットオフ周波数を保持する、小型化・低消費電流化に適したフィルタ回路を提供する。

【解決手段】可変電流源を備えた基準コンデンサを用いて被比較電圧を生成し、被比較電圧と基準電圧を比較器によって比較し、電位差をロジック回路によってデジタル信号に変換する。変換されたデジタル信号によって、可変容量回路のスイッチを切り替える。またデジタル信号は可変電流源にも入力され可変電流源の電流値を変える。この動作を繰り返すことにより、フィルタのカットオフ周波数を決定することで、カットオフ周波数が一定に保持されるフィルタ回路を構成する。

(もっと読む)

ノイズフィルタ回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60)は、入力信号(IN)を入力するラッチ回路(14;64)を備える。ラッチ回路(14;64)は、第1および第2の論理演算回路(たとえば、NAND回路)を含む。第1および第2のNAND回路のそれぞれにおいて、セット信号(S)またはリセット(R)信号を入力するP型トランジスタ(P1)の能力は、セット信号(S)またはリセット(R)信号を入力するN型トランジスタ(N1)の能力、および、このN型トランジスタ(N1)と直列に接続されるN型トランジスタ(N2)の能力(トータルな能力)より低い。ノイズフィルタ回路(10;60)は、ラッチ回路(14;64)からの出力信号(OUT(XQ;Q))を入力する波形整形回路(16)を、備えてもよい。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

ゲイン補正回路、位相同期回路及びフィルタ回路

【課題】製造バラツキ又は温度変化等による特性変化を補償するとともに、広い入力レンジを確保すること。

【解決手段】異なる電圧電流変換ゲインGm1,Gm2を有するトランスコンダクタンス回路12,14を備え、選択した1のトランスコンダクタンス回路12,14により電圧電流変換を行い、入力電圧を電流に変換する電圧電流変換部10と、トランスコンダクタンス回路12,14に供給されるバイアス電流Ib−Icontを制御し、電圧電流変換ゲインGm1,Gm2を一定値に制御する補正回路部30と、バイアス電流Ib−Icontと所定の基準電流Irefとを比較する電流コンパレータ56と、比較の結果に基づいて、電圧電流変換を行うトランスコンダクタンス回路12,14を電圧電流変換ゲインGm1,Gm2が異なる他のトランスコンダクタンス回路12,14へ切換えるスイッチ回路22と、を備える。

(もっと読む)

増幅器、およびフィルタ

【課題】入力されるバイアス電圧と電圧信号とのうち、電圧信号を増幅することが可能な増幅器、およびフィルタを提供する。

【解決手段】静電容量が可変する第1可変静電容量素子と、第1可変静電容量素子と電気的に接続され、静電容量が可変する第2可変静電容量素子と、第1可変静電容量素子と第2可変静電容量素子とに対してバイアス電圧と電圧信号とを選択的に入力する第1入力部とを備え、第1可変静電容量素子と第2可変静電容量素子とにバイアス電圧と電圧信号とが入力される場合は、第1可変静電容量素子と第2可変静電容量素子との静電容量を第1の値とし、第1可変静電容量素子と第2の可変静電容量素子の静電容量を、第1の値よりも小さな第2の値として電圧信号を増幅する増幅器が提供される。

(もっと読む)

増幅器、増幅方法、およびフィルタ

【課題】入力されるバイアス電圧と電圧信号とのうち、電圧信号を増幅することが可能な増幅器、増幅方法、およびフィルタを提供する。

【解決手段】静電容量が可変する第1可変静電容量素子と、第1可変静電容量素子と電気的に接続され、第1可変静電容量素子と逆導電型であり、静電容量が可変する第2可変静電容量素子と、第1可変静電容量素子と第2可変静電容量素子とに対してバイアス電圧と電圧信号とを選択的に入力する第1入力部とを備え、第1可変静電容量素子と第2可変静電容量素子とにバイアス電圧と電圧信号とが入力される場合は、第1可変静電容量素子と第2可変静電容量素子との静電容量を第1の値とし、第1可変静電容量素子と第2の可変静電容量素子の静電容量を、第1の値よりも小さな第2の値として電圧信号を増幅する増幅器が提供される。

(もっと読む)

RCキャリブレーション回路と、それを用いたRCキャリブレーション機能付RCフィルタ回路、受信チューナおよび携帯端末

【課題】低価格で校正時間が短いRCキャリブレーション回路を提供する。

【解決手段】このRCキャリブレーション回路では、基準クロック信号RefCLKを2分周して分周信号VINを生成し、分周信号VINの立ち上がりエッジに応答してキャパシタを充電し、キャパシタの端子間電圧VOUTが基準電圧Vrefを超えたとき、基準クロック信号RefCLKのレベルに応じてカウント値C1〜CNが増加または減少し、カウント値C1〜CNによってRCフィルタ回路およびRCリファレンス回路3の時定数を制御する。したがって、従来の遅延器75やラッチ回路76が不要となる。

(もっと読む)

抵抗器およびキャパシタをチューンするための方法および装置

集積回路における抵抗器(410)およびキャパシタ(420)についての2ステップチューニングプロセスが説明されている。チューニングプロセスの第1のステップにおいては、オンチップ調節可能な抵抗器(410)は、チューンされた抵抗器を得るために、外部抵抗器に基づいてチューンされる。チューンされた抵抗器の値は、外部抵抗器と調節可能な抵抗器(410)の設計とによって決定された、ターゲットパーセンテージ内で、正確である。第2のステップにおいては、調節可能なキャパシタ(420)は、正確な値を有しているチューンされたキャパシタを得るために、チューンされた抵抗器の値と正確なクロックとに基づいて、チューンされる。調節可能なキャパシタ(420)は、チューンされた抵抗器およびチューンキャパシタについてのRC時間定数が、正確クロックと調節可能なキャパシタ(420)の設計とによって決定されるターゲットパーセンテージ内に正確であるように、チューンされることができる。集積回路上の他の回路の抵抗器およびキャパシタは、チューンされた抵抗器およびチューンされたキャパシタ、それぞれに基づいて、調節されることができる。  (もっと読む)

(もっと読む)

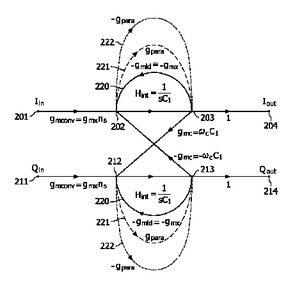

ラジオ受信機

信号有向グラフを用いてフィルタ内の寄生信号伝達を識別するステップと、補償経路をフィルタに追加して寄生信号伝達の影響を低減または解消するステップとを具えた方法を提供する。これに対応するフィルタを提供し、このフィルタは、1つ以上のフィルタ極を生成する複数の増幅段と、これらの増幅段の少なくとも1つに結合された少なくとも1つの構成部品であって、フィルタ内に寄生効果を生じさせる構成部品と、上記少なくとも1つの増幅段に補償電流を加えて、この寄生効果を低減または解消する手段とを具えている。さらにラジオ受信機を提供し、このラジオ受信機は、同相及び直交信号を受信してフィルタ処理するフィルタと、フィルタ処理した同相及び直交信号の一方を受信して増幅する増幅器と、フィルタ処理して増幅した同相または直交信号をこの増幅器から受信し、上記同相または直交信号の他方を、上記フィルタ処理して増幅した信号から再生する手段とを具えている。  (もっと読む)

(もっと読む)

可変トランスコンダクタ

【課題】トランスコンダクタンスの可変域を拡大又は維持しつつ出力端子の寄生容量を低減する。

【解決手段】2つの入力回路10,60が平方根圧縮回路20と電圧電流変換回路30とを共有するように構成する。また、電圧電流変換回路30を構成する差動MOSトランジスタM5及びM6の出力部において、固定バイアス電流Ibiasを電流源41,42で引き抜き、同時にM5及びM6の可変駆動電流と同一の可変バイアス電流Ibを電流源51,52から供給することで、出力バイアス回路40の電流が固定バイアス電流Ibiasと常に等しくなるようにする。更に、電圧電流変換回路30と出力バイアス回路40との間に、カスコード接続のMOSトランジスタM9及びM10からなる電流バッファ50を挿入する。

(もっと読む)

フィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システム

【課題】特性周波数の調整機能を有するフィルタに対して、高い調整精度を持ちかつ容易に低消費電流化を実現したバラツキ補正を可能にし、フィルタ調整誤差を確実に抑えることができるフィルタ自動調整回路およびフィルタ調整方法ならびに携帯電話システムを提供する。

【解決手段】基準フィルタ103のバラツキを検出するために、位相差検出器104により、基準フィルタ103における前後の位相差をカウンタ106にてカウントする際に、一種類の基準信号でなく、位相器110で作成した複数個の基準信号を用いてカウントし、このカウント結果から得られる信号を、主フィルタ109の制御信号116(1)〜116(n)としてレジスタ108に保持することにより、主フィルタ103のバラツキ調整後は、フィルタ調整に関する部材のすべての動作を停止させる。

(もっと読む)

アクティブインダクタンス回路、フィルタ回路及び受信回路

【課題】 低電源電圧状態での歪特定を改善して動作を安定化でき、設計の自由度を向上し得るようなアクティブインダクタンス回路を提供する。

【解決手段】 正抵抗に対して負性抵抗を帰還したハイインピーダンス回路のハイインピーダンス部分に容量(コンデンサ108)を付加することにより形成した差動型の90度移相器130と、入力信号を電流に変換して上記90度移相器130に電流を流し込む第1の差動対回路140と、上記90度移相器130の出力電圧を電流に変換して入力側に戻す第2の差動対回路150とを有して構成され、上記90度移相器130の入力側からみたインピーダンスを2端子のインダクタンスとして作用させる。

(もっと読む)

フィルタの自動調整装置

【課題】ダミーフィルタの次数とメインフィルタの次数とが異なっていても、メインフィルタの周波数特性を所望の特性に調整することができるようにする。

【解決手段】ダミーフィルタ2の制御電圧Vcdを出力する第1のオペアンプ5とメインフィルタ1との間にインタフェース回路6として第2のオペアンプ7を配置し、第2のオペアンプ7の基準電圧Vrを最適化することにより、ダミーフィルタ2を用いて得られた制御電圧Vcdがインタフェース回路6によってメインフィルタ1に最適な制御電圧Vcmに変換されるようにして、メインフィルタ1の周波数特性を所望の特性に調整するのに必要な最適な制御電圧Vcmを得ることができようにする。

(もっと読む)

ユーザ指定可能、低コスト、低ノイズであり、位相跳躍に影響されにくいマルチオクターブ帯域チューナブル発振器

【課題】同調帯域上で比較的低く均一な位相ノイズを維持しながら、マルチオクターブ帯域周波数選択性を有する電圧制御発振器を提供する。

【解決手段】電圧制御発振器100は、バイポーラトランジスタからなる能動素子104、チップ形態での実装が可能なマルチモード結合共振器120、遅波結合共振器124、進行波結合共振器128、ノイズフィルタリング回路網108、ノイズ除去回路網112、ノイズフィードバック・DCバイアス回路116及び位相補償回路網132等により構成されている。これらの構成により、広帯域線形同調レンジを実現しつつ位相ノイズを最小化し、動作周波数帯域全体にわたって均一な出力パワーと改善された高次高調波の遮断が実現できる。

(もっと読む)

受信機

【課題】アクティブフィルタを用いた受信機においてマルチスロット受信を行う際、スロット間でアクティブフィルタ部の電源がON/OFF動作を行う為、アクティブフィルタの周波数特性調整回路が働き、調整動作がガードビット内で終了しないためにマルチスロット受信が行えないという問題があった。

【解決手段】本発明の受信機は、アクティブフィルタの電源制御とアクティブフィルタ以外の電源制御を個別に制御する手段を設けている。これによりマルチスロット受信時のスロット間で電源ON/OFF信号がきても、アクティブフィルタの電源制御とアクティブフィルタ以外の電源制御を個別に制御してアクティブフィルタの電源ON/OFF動作を行わないことで、周波数特性調整動作も行われなくなるため、次スロットが受信可能となる。

(もっと読む)

クロック信号発生回路

【課題】スイッチドキャパシタ回路の高速化の際に、スイッチドキャパシタ回路を動作させるために供給するクロックタイミングがばらつきや配線に付く寄生抵抗、容量によってはタイミング破綻を引き起こす。

【解決手段】スイッチドキャパシタ回路を動作させるために供給するクロック信号のボトムプレートサンプリング期間と、ノンオーバーラップ期間を制御手段により、タイミングを調整可能にする事により、タイミング破綻を回避する事が出来、且つ前記それぞれの期間を決定付ける論理素子の面積を増大させる事なく構成できる。

(もっと読む)

1 - 20 / 26

[ Back to top ]