Fターム[5J098CA04]の内容

能動素子を用いた回路網 (5,588) | 周波数選択回路網の機能 (352) | フィルタ (330) | HPF (46)

Fターム[5J098CA04]に分類される特許

1 - 20 / 46

信号等化器

フィルタ回路及び受信装置

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

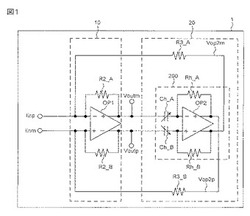

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

ロードスイッチ

【課題】小さい入力−出力差分電圧を維持し、既定の応答を提供する半導体装置、回路、そしてAC及びDCロードスイッチを提供する。

【解決手段】ロードスイッチは、入力端子及び出力端子へ結合された通過素子を含み得る。通過素子は制御端子を含み、制御端子は通過素子の応答を制御し得る。ロードスイッチは第1のループを含み得る。第1のループは制御端子へ結合され、通過素子との高インピーダンスを維持しながら入力端子及び出力端子間の電圧降下を制御するように構成される。ロードスイッチは第2のループを含み得る。第2のループは制御端子へ結合され、既定のフィルタ応答を入力端子から提供するように構成される。既定の応答は、低域通過応答、高域通過応答、又は帯域通過応答であり得る。応答の通過帯域及び/又は阻止帯域は、プログラムされ得る。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

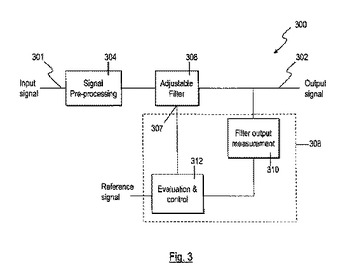

ホイールモニタリングシステムのための追跡フィルタ装置

ホイールモニタリングシステムは、変化する主周波数を有する信号を追跡する追跡フィルタ装置を含む。追跡フィルタ装置は、調整可能なフィルタと、フィルタリングされた信号の振幅を測定し、振幅を基準値に対して比較するように構成されたフィルタコントローラとを備える。フィルタコントローラは、測定された振幅が基準値から所定のしきい値を越える量にわたって相違するとき、フィルタのカットオフ周波数を調整する。フィルタコントローラは、主周波数がフィルタの周波数応答のロールオフ領域内に存在するように、カットオフ周波数を調整する。本システムは、ホイールに設けられたモニタリング装置の衝撃センサによって生成された信号を追跡するために使用可能である。  (もっと読む)

(もっと読む)

フィルタ回路およびバイアス回路

【課題】回路面積の縮小を図りつつ、出力信号に含まれるオフセットを減少させることが可能なフィルタ回路を提供する。

【解決手段】フィルタ回路は、入力端子と出力端子との間に接続された第1のキャパシタと、前記出力端子と設定電位との間に接続されたバイアス回路と、を備え、前記バイアス回路は、前記出力端子と設定電位との間に接続された第1のMOSトランジスタと、前記第1のMOSトランジスタのゲートと前記出力端子との間に接続された第2のキャパシタと、前記第1のMOSトランジスタのゲートに一端が接続され、第1のバイアス電位が他端に印加された抵抗素子と、を有する。

(もっと読む)

フィルタ回路

【課題】入力信号の大きさの広い範囲にあっても良好な線形性を有する高域通過フィルタ及びノッチフィルタを提供する。

【解決手段】 PMOSトランジスタ(Tr)1、Tr1とドレイン同士が接続されるTr2、ドレインがTr1のソースに接続されるTr3、Tr3がTr2のソースに接続されるTr4を有し、Tr3のゲートがTr4のドレインに接続し、Tr4のゲートがTr3のドレインに接続し、Tr3、Tr4のソースに接続される電流源5、6、Tr1、Tr2のソース間に接続されるコンデンサ8、Tr3、Tr4のソース間に接続されるコンデンサ7を含む回路29、Tr1、Tr2のゲートからTr3、Tr4のソースまでの経路において分岐された信号を出力信号に重畳し、回路29によって減衰される周波数帯域と異なる周波数帯域が減衰される信号を生成する回路100とによってフィルタ回路を構成する。

(もっと読む)

フィルター回路

【課題】入力信号の周波数が高くなるほど出力信号の入力信号に対する相対的な位相が進行し、入力信号の周波数が低くなるほど出力信号の入力信号に対する相対的な位相差がなくなる周波数領域を使用するフィルター回路を得る。

【解決手段】抵抗とコンデンサによって構成されるフィルター回路において、入力端子Iと接地端子Gの間に第1の抵抗R1と第2の抵抗R2とコンデンサCがこの順番で直列に接続され、第1の抵抗R1と第2の抵抗R2の接続点に出力端子Oが設けられており、第1の抵抗R1と第2の抵抗R2の合成抵抗値とコンデンサCの静電容量値によって決定されるカットオフ周波数より高い周波数領域にある最大位相遅延周波数より高い周波数領域を使用することにより、入力信号の周波数が高くなるにつれて、出力信号の入力信号に対する相対的な位相の遅れが小さくなる特性を発揮するフィルター回路による。

(もっと読む)

周波数可変フィルタ回路

【課題】簡素な回路構成で実現でき、小型化可能な周波数可変フィルタ回路を提供すること。

【解決手段】インダクタ12と可変容量素子14(第2の並列容量素子)とが並列に接続された並列共振回路20と、複数の可変容量素子10、11及び13からなるインピーダンス調製回路21と、2つのエミッタフォロワ回路16、18からなるインピーダンス調整回路22と、を備えて周波数可変フィルタ回路1を構成し、可変容量素子10の容量値と可変容量素子11(及び可変容量素子10と可変容量素子13)の容量値との比を調整することにより、並列共振回路20の入力側のインピーダンスを所望値に調整し、エミッタフォロワ回路16及び18によって並列共振回路20の出力側のインピーダンスを所望値に調整することにより、簡素な構成で小型化可能の周波数可変フィルタ回路を構成した。

(もっと読む)

周波数特性調整回路、受信インタフェース回路および磁気記憶装置

【課題】伝送路との整合を保持しながら交流結合回路による低域側遮断域を変化させる。

【解決手段】周波数特性調整回路20の遮断域調整部21は、AC結合回路10の周波数特性における低域側遮断域が移動するように、AC結合回路10からの出力信号を通過させる。遮断域調整部21の零点周波数および極周波数は、制御信号に応じて設定される。この制御信号により、遮断域調整部21の伝達関数の分子多項式が、AC結合回路10の伝達関数の分母多項式と等しくされ、遮断域調整部21の零点周波数が、AC結合回路10による低域遮断周波数に合わせられる。このため、AC結合回路10から遮断域調整部21を通過した出力信号は、AC結合回路10により生じた低域遮断域が移動した周波数特性を有するようになる。そして、この周波数特性において、制御信号に応じて設定される遮断域調整部21の極周波数が、移動後の低域側遮断域の遮断周波数となる。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

MOSトランジスタ抵抗器、フィルタおよび集積回路

【課題】製造上のばらつきによるリーク電流の変化に起因する抵抗値の変動が低減され、かつ温度特性の良好なMOSトランジスタ抵抗器を提供する。

【解決手段】抵抗器として使用される第1MOSトランジスタM1と、第1MOSトランジスタのソースに接続され、入力電圧Vinを印加する入力電圧源1と、第1MOSトランジスタのゲートに接続され、ゲート電圧Vgを印加するゲート電圧源6とを備えたMOSトランジスタ抵抗器。ゲート電圧Vg及び入力電圧Vinは、第1MOSトランジスタのゲート−ソース間電圧及びソース−ドレイン間電圧が、第1MOSトランジスタを非飽和領域で動作させる範囲で印加されるとともに、第1MOSトランジスタの抵抗値における温度特性の温度特性が一定になる条件を満たす関係に設定される。

(もっと読む)

フィルタ回路

【課題】 可変する回路定数を減らし、かつ、回路定数の可変範囲を同じにしても、Qの変動が大きくならないようにする。

【解決手段】 VCVS型の2次HPF20B、30Bを縦続接続し、HPF20Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが大から小へ変化する抵抗R22と、HPF30Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが小から大へ変化する抵抗R32を互いに連動して抵抗値が可変するようにする。可変抵抗R22とR32を連動して可変したとき、各HPF20B、30BのQが相補的に変動するようにしたので、Qの変動を小さく抑えることができる。各HPF20B、30Bはカットオフ周波数の可変範囲、Qに対する設計自由度が高く、R22とR32の可変範囲を同じにしながらQがほぼ一定にすることができる。

(もっと読む)

受信素子

【課題】バンドパスフィルタの中心周波数の調整を不要とすることで、煩雑な調整工程を省略することができる受信素子を提供する。

【解決手段】受信素子3は、受信信号の搬送波近傍の周波数帯域を通過させる中心周波数を有し、前記中心周波数が調整可能なバンドパスフィルタ(BPF)部3bと、BPF部3bからの出力信号を復調する復調回路部3cと、受信信号が入力され、中心周波数が遮断周波数に設定されたハイパスフィルタ(HPF)部3duおよびローパスフィルタ(LPF)部3dwと、HPF部3duおよびLPF部3dwのそれぞれの出力信号の電圧レベルを比較する比較回路部3dyと、比較回路部3dyで比較した結果、HPF部3duからの出力信号の電圧レベルが高ければ中心周波数を上昇させ、LPF部3dwからの出力信号の電圧レベルが高ければ中心周波数を低減させるようBPF部3bを調整するバイアス回路部3dzとを備えている。

(もっと読む)

フィルタ回路

【課題】 少ない回路素子数で周波数帯域分割を可能とする。

【解決手段】 12は非反転入力が接地され、出力側が第1出力端子13とコンデンサCfを介して反転入力と接続された演算増幅器、R1〜R3は固定抵抗であり、入力端子10と演算増幅器12の出力間にR1とR2が直列に接続され、R1とR2の接続点Pと演算増幅器12の反転入力の間にR3が接続されている。接続点PにはコンデンサCが接続されている。20は電流/電圧変換部であり、この内、21は非反転入力が接地され、出力側が第2出力端子22と抵抗Rfを介して反転入力と接続された演算増幅器である。Cの他端は演算増幅器21の仮想接地された反転入力と接続されており、LPF部11は多重帰還形2次LPFを構成する。入力端子−第1出力端子間の伝達関数は2次LPFの形式、入力端子−第2出力端子間の伝達関数は2次HPFの形式となり、カットオフ周波数f0とQは同じになる。

(もっと読む)

プリエンファシス回路

【課題】 簡単な構成でプリエンファシス信号を生成することが可能なプリエンファシス回路を実現する。

【解決手段】 信号の変化点で振幅を大きくするプリエンファシス回路において、差動入力信号を差動電流出力に変換する第1のトランスコンダクタンスアンプと、ハイパスフィルタ回路と、このハイパスフィルタ回路を介した前記差動入力信号を差動電流出力に変換する第2のトランスコンダクタンスアンプと、2つの前記差動電流出力をそれぞれ加算して電圧変換する第1及び第2の抵抗とを設ける。

(もっと読む)

1 - 20 / 46

[ Back to top ]