Fターム[5J106BB09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 復調 (19)

Fターム[5J106BB09]に分類される特許

1 - 19 / 19

RDS復調回路

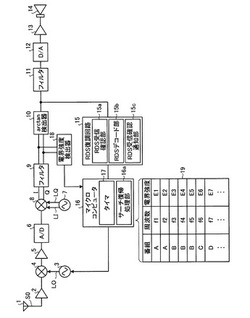

【課題】RDSデータの受信間隔を短くすることなく、RDS局のサーチ時間を低減する。

【解決手段】RDS受信確認部15aは、アークタンジェント型検波器10から出力されたFM復調信号のレベル変化点とRDSの基準クロックとの位相の比較結果に基づいて、RDSデータの受信の確認を行い、RDS受信確認通知部15cは、RDSデコード部15bにてデコードされるRDSデータをマイクロコンピュータ16に通知する前に、RDSデータを受信できるかどうかの確認結果をマイクロコンピュータ16に通知する。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】

演算量を低減しつつ、入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910AからのサンプルレートfSM1でサンプリングされた信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られ、サンプルレートfSM2(<fSM1)でサンプリングされた信号PWA1,PWA2を生成する。これらの信号PWA1,PWA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相をサンプルレートfSM1に戻した後、パイロット信号の位相に基づいて、基準信号発生部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】 入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910からの信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られた信号PSA1,PSA2を生成する。これらの信号PSA1,PSA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相に基づいて、基準信号生成部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

パイロットPLL回路及びFMステレオ復調回路

【課題】制御特性を向上させることが可能なパイロットPLL回路を提供することを目的とする。

【解決手段】制御データを与えられて出力周波数が変化するNCO31、出力周波数を与えられ第1の周波数の余弦波データを出力するROMテーブル32、FM復調データと第1の周波数の余弦波データとを与えられて乗算し乗算結果を出力する乗算器33、乗算結果を積分した累積加算データを出力する積分器35、乗算結果を与えられFM復調データと出力周波数との間の周波数偏差信号を出力するLPF34、累積加算データと周波数偏差信号とを加算して制御データを出力する加算器36、FM復調データのパイロット信号成分を検出してパイロット信号検出信号を出力するパイロット信号検出回路50を備え、積分器は累積加算データの値をパイロット信号検出信号に応じて制御する。

(もっと読む)

DLL回路

【課題】 従来は、位相差制御がパスの高速移動に追従できず、逆拡散の際にジッタが大きくなって、復調信号の品質が劣化してしまうという問題点があり、位相差制御の周期を可変として、ジッタの発生を抑制し、復調信号の品質の劣化を防ぐことができるDLL回路を提供する。

【解決手段】 チャネル推定回路11が、受信ベースバンド信号を逆拡散した相関値からフェージングによる歪を推定し、フェージング周波数推定回路12が、チャネル推定回路11の出力に基づいてフェージング周波数を推定してフェージング周波数推定値を出力し、DLL制御部13が、フェージング周波数推定値に応じて、拡散符号発生回路7のクロックタイミングを調整する位相差制御の周期を調整し、調整された周期でクロックタイミングの位相差制御を行うDLL回路としている。

(もっと読む)

信号処理装置

【課題】変調信号の復調を実行する際の消費電力を低減し、かつ実装コストを抑制することが可能な信号処理装置を提供する。

【解決手段】本発明に係る信号処理装置は、互いにほぼ直交する第1及び第2のリファレンス信号を生成する発振器と、搬送波周波数からベースバンド周波数に変換された変調信号の同相成分を示す第1信号と当該変調信号の直交成分を示す第2信号を入力する入力部と、第1信号と第1リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第1位相差信号を出力する第1位相比較器と、第2信号と第2リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第2位相差信号を出力する第2位相比較器と、第2位相差信号から第1位相差信号を減算し、合成位相差信号を出力する合成部を備え、合成部から出力された信号を復調信号として出力すると共に、発信器への入力として用いる。

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

デジタル制御発振器、このデジタル制御発振器を備えた位相同期ループ及び通信機

【課題】スプリアスが生じにくい。

【解決手段】ADCから入力されたnビットのデジタル信号は、mビットが整数部41、且つ、n−mビットがデジタル制御値時間変化部43に入力される。そして、デジタル制御値時間変化部43から時間的に変化するデジタル制御値が小数部42に入力される。デジタル制御発振器4は、整数部41によってステップ周波数刻みで発振周波数を変化させる。また、小数部42によってステップ周波数よりも小さな周波数刻みで発振周波数を変化させる。このとき、小数部42によって変化させることができる周波数は、ステップ周波数よりも大きい。

(もっと読む)

標準信号発生器及び標準信号発生システム

【課題】恒温設備を設けることなく位相ドリフトを低減させて、標準信号発生器のウォームアップ時間の短縮を図ること。

【解決手段】位相補正データ生成部4のA/D変換器41は、基準信号生成部1から出力された基準信号14aの周波数をサンプリング周波数として標準信号100aをA/D変換する。プログラマブル周波数ディバイダ42が分周した基準信号14aの周期で、データ間引き部43はA/D変換器41からのビート信号41aを間引き抽出する。補正量算出部40は、データ間引き部43からのビート信号43aの電圧値に基づいて、位相ドリフト量Δθdriftを算出する。その位相ドリフト量Δθdriftに基づいて標準信号100aの位相補正を行う。

(もっと読む)

映像検波回路

【課題】AM変調されたPIF信号から映像信号を同期検波するVIF回路において、過変調状態にて復調される映像信号の精度が低くなる。

【解決手段】比較器68は、過変調状態であるVTH超の映像信号か否かを判定する。VTH以下の期間では、スイッチ回路56はAPCフィルタ54の出力電圧をVCO48に入力させ、PLLを構成する。PLLは、PIF信号にロックするように動作し、搬送波を再生する。一方、VTHを超える期間では、スイッチ回路56はSH回路58の出力電圧VSHをVCO48に入力する。SH回路58は、水平同期期間でのロック状態のAPCフィルタ54の電圧を保持しており、これを用いてVCO48を制御することで、フリーランや周波数ドリフトが抑制される。

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

【課題】本発明は、PLL回路、復調回路、ICカード及びICカード処理装置に関し、例えば非接触により種々のデータを入出力するICカードと、このICカードとデータ通信するICカード処理装置に適用して、簡易な構成で、入力信号が劣化した場合でも確実に入力信号を処理することができるようにする。

【解決手段】90度位相の異なる発振出力信号による位相比較結果の正負を基準にして制御方向を決定し、この制御方向に発振出力信号を制御する。

(もっと読む)

可変分周器および検波器

【課題】可変分周器の出力信号のデューティー比を任意の比率に設定する。

【解決手段】入力クロックを予め設定された分周比で分周した分周クロックを出力する可変分周器であって、入力クロックを分周した内部クロックを出力する分周部と、内部クロックを2分周して分周クロックとして出力する固定分周器と、分周クロックの論理値に応じて第1分周比および第2分周比のいずれかを選択し、分周部が入力クロックを分周する分周比として設定する選択部とを備える可変分周器を提供する。

(もっと読む)

集積回路、再生装置及び再生方法

【課題】 本発明は、集積回路、再生装置及び再生方法に関し、例えば非接触型のICカードシステムに適用して、クロックの周波数がばらついた状態で、デューティー比が50〔%〕から変化した場合でも、正しくデータを再生することができるようにする。

【解決手段】 本発明は、ペイロードの部分に比して速く収束するようにPLL回路の動作を切り換えて、90度位相の異なる基準信号の一方を入力信号に位相同期させるようにこれら基準信号を位相制御し、他方の基準信号が入力信号に位相同期したとの位相比較結果が得られた場合に、直前の制御を継続する。

(もっと読む)

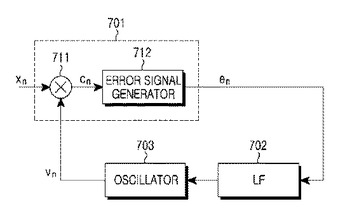

位相固定ループと位相固定ループでの位相検出方法及びこれを用いる受信器

位相固定ループ(PLL)の位相検出動作が行われる間に、低いSNR環境下の定常状態での性能劣化を防止しつつも、獲得状態での収束性能を向上させる位相固定ループと位相固定ループでの位相検出方法及びこれを用いる受信器を提供する。位相固定ループは、入力信号及びフィードバック信号に従って、入力信号が属する期間を判定し、判定された期間に対して設定された式(又はアルゴリズム)を使用することによって、入力信号に対応する誤差信号を出力し、誤差信号に従って所定の周波数信号を発振し、発振された信号をフィードバックする。  (もっと読む)

(もっと読む)

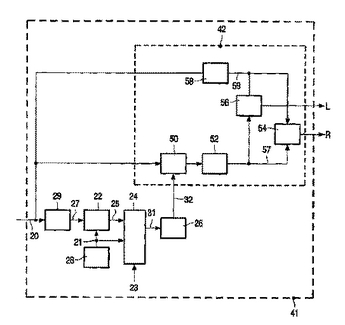

位相同期ループを用いない信号の回復

デジタル入力信号(20)から第1のデジタル信号(7、31)を回復するための構成が、デジタル入力信号(20)をフィルタリングするためのデジタル・フィルタ(29)と、デジタル基準信号(21)を生成するためのデジタル制御発振器28と、フィルタリングされたデジタル入力信号(27)とデジタル基準信号(21)との位相差(25)を求めるためのデジタル位相検出器(22)とを備える。第1のデジタル信号(7、31)は、求められた位相差(25)を、デジタル基準信号(21)の位相に加えることによって回復することができる。  (もっと読む)

(もっと読む)

VCO装置

テレビジョン放送受信機等の無線装置に用いられるVCO(電圧制御発振回路)装置に関する。発振周波数が広帯域にわたり、かつ低消費電力化が実現できるVCO装置を提供する。VCO回路群(4)は、周波数制御電圧端子(8)に印加される制御電圧(Vt)に応じた周波数の信号を発振する。LO信号選択手段(3)はVCO回路群(4)の中から所望の出力信号を選択する。PLL(6)は、LO信号選択手段(3)で選択された局部信号(fvco)を分周して基準信号との位相を比較し位相差から変換した信号を出力する。ループフィルタ(7)は、PLL(6)の出力信号を平滑して周波数制御電圧である制御電圧(Vt)を出力し、LO信号選択手段(3)で選択された局部信号を高周波信号処理手段(1)へ出力する。  (もっと読む)

(もっと読む)

通信用半導体集積回路および無線通信システム

受信用VCO(250)と送信用VCO(240a,240b)と中間周波数用VCO(230)のうち少なくとも1つのVCOが変復調回路と共に1つの半導体チップ上に形成された通信用半導体集積回路において、オンチップのVCOを複数の周波数帯で動作可能に構成し、また該VCOの発振周波数を測定する回路(22)および測定された値を記憶する記憶回路(18)と該記憶回路に記憶されている測定値と外部からの設定値とを比較して上記VCOの使用周波数帯を決定する回路(19)を設けるとともに、該記憶回路の記憶データを外部へ読出しまた外部から書き込むことができるように構成した。  (もっと読む)

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

本発明は、所望の伝送系を介して伝送された入力信号より、入力信号を介して伝送されるデータ列を再生する復調回路であり、発振器(252)及び可変型分周器(253)により生成される第1の発振出力信号及び第1の発振出力信号に対して90度[π/2]位相の異なる第2の発振出力信号をイクスクルーシブオア(EX−OR)回路(254Q)(254I)により位相比較し、その位相比較結果の正負に基づいて制御方向判定回路(257)により制御方向を判定し、その制御方向判定結果を積算回路(258)により入力信号の1周期分積算して、その積算結果に対し、補正回路(259)により、位相比較結果に基づいて位相差が[±π/2]の場合に所定の制御量とする補正処理を行い、1周期に1回に出力される補正処理済みの制御信号により可変型分周器(253)の動作を制御する。 (もっと読む)

チューナ

【課題】 局部発振信号に妨害波となる基準周波信号が重畳するのを防止できるチューナを提供する。

【解決手段】 チューナ10は、入力端子1、第1〜第4の帯域通過フィルタ2a〜2d、自動利得制御器3、第1〜第3の増幅器4a〜4c、第1及び第2の混合器5a,5b、第1及び第2の電圧制御発振器6a,6b、第1及び第2のPLLIC7a,7b、基準発振子回路8、出力端子9を備える。そして、第2のPLLIC7bと基準発振子回路8とは従来例のチューナ50と同様にコンデンサC2及び増幅器AMPを介して接続されるが、第1のPLLIC7aに含まれる基準発振用の増幅器と基準発振子回路8とはインダクタンス素子であるインダクタL1を介して接続される。

(もっと読む)

1 - 19 / 19

[ Back to top ]