Fターム[5J106DD07]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375) | 減衰回路 (10)

Fターム[5J106DD07]に分類される特許

1 - 10 / 10

信号伝搬遅延を補償するための装置及び方法

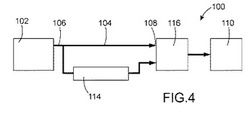

【課題】1以上の伝送接続上の電気信号など、1以上の信号の伝搬遅延または時間を補償する装置及び方法を提供し、実装のための複雑な演算手段を必要とせず、自動的に伝搬時間の補償を行なうことを可能とする。

【解決手段】第1伝送接続(104)の第1端(106)と第2端(108)の間を伝搬中に第1周期信号ref(t)が受ける遅延τを補償するための装置(100)であり、前記第1信号ref(t)に対応し、その位相が遅延τに等しい時間により位相前進された第2信号ref(t+τ)を生成可能な第1手段(114)と、前記第1伝送接続の前記第2端で取得され前記第1信号ref(t)に対応し、その位相が遅延τにより遅延された第3信号ref(t-τ)と、前記第2信号ref(t+τ)とから、前記第1信号ref(t)と同位相である第4信号を生成可能な第2手段(116)とを少なくとも備える。

(もっと読む)

PLL回路

【課題】 安定した位相雑音特性を得ることができるPLL回路を提供する。

【解決手段】 基準発振器4からの基準周波数(Fref)信号のレベルを検波回路7で検出し、制御回路5が、検出したレベルが特定値に比べて小さい場合は可変ATT6の減衰量を小さくし、検出したレベルが特定値に比べて大きい場合は可変ATT6の減衰量を大きくする制御信号を可変ATT6に出力し、可変ATT6では制御回路5からの制御信号に従って基準周波数信号の減衰を行い、PLL IC2への基準周波数信号の入力レベルを安定化させ、位相雑音特性の劣化を防止し、更にアンロックを防止できるPLL回路である。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

位相ロックループ回路

【課題】回路面積の増大、ピン数の浪費、入出力位相誤差特性の悪化を招くことなく、ループバンド幅の狭い位相ロックループ回路を提供する。

【解決手段】位相ロックループ回路は、フィルタ回路と電圧制御発振回路との間に設けられ、フィルタ回路から供給される第1のアナログ電圧のゲインを1/n(nは1よりも大きい値)に抑制した第2のアナログ電圧を電圧制御発振回路に供給するゲイン抑制回路を備える。ゲイン抑制回路は、第1のアナログ電圧が、その可動範囲の上限電圧もしくは下限電圧に到達している期間は、第2のアナログ電圧の可動範囲の上限電圧が、最大で電圧制御発振回路の入力電圧範囲の上限電圧になるまで一定の比率で平行移動させる、もしくは、第2のアナログ電圧の可動範囲の下限電圧が、最小で電圧制御発振回路の入力電圧範囲の下限電圧になるまで一定の比率で平行移動させる。

(もっと読む)

発振器及びルビジウム原子発振器

【課題】逓倍回路側と発振増幅器側にそれぞれフィルタを備えることにより、簡単な回路

構成で両回路のアイソレーションを高く保つことが可能となり、調整時間を短縮して調整

コストの低減を図った発振器及びルビジウム原子発振器を提供する。

【解決手段】発振部50は、電圧に基づいて発振周波数が制御される電圧制御発振器10

と、発振信号の周波数を逓倍する逓倍回路11と、所定の周波数を選択的に通過させる帯

域通過フィルタ12と、前記電圧制御発振器10により発振された発振信号を5.3MH

zに周波数変換する生成回路14と、生成回路14の出力レベルを増幅する増幅回路15

と、所定の減衰値を有する減衰器16と、所定の周波数を選択的に阻止する帯域阻止フィ

ルタ17と、周波数成分をインピーダンス整合して合成する整合回路13と、を備えて構

成されている。

(もっと読む)

チャージポンプ及びPLL回路

【課題】チャージポンプ回路のスイッチングトランジスタを大振幅の制御信号で駆動すると、ソース、ドレインの寄生容量、ゲート電極下のチャンネル電荷により、出力電流に乱れが生じる。特にチャージポンプの出力電流が小さい場合顕著になる。

【解決手段】電流源10,11の出力をスイッチングするための差動構成の差動スイッチング回路12,13を設け、差動スイッチング回路12,13を構成するトランジスタのゲートにかかる論理振幅を振幅制限/減衰回路14,15を用いて小さくすることで、寄生容量、チャンネル電荷による出力電流の乱れを改善する。

(もっと読む)

変調制御回路

【課題】 本発明は、変調された光信号を出射する外部変調器に好適な動作点を設定しつつ変調信号を与える変調制御回路に関し、広範なビットレートによる高品質の変調を可能とすることを目的とする。

【解決手段】 変調信号に重畳される第一のパイロット信号またはこの変調信号に重畳された第一のパイロット信号と、その変調信号に応じて外部変調器11が出射する光信号から抽出した第二のパイロット信号との位相差を検出する位相差検出手段12と、検出された位相差を外部変調器11に帰還し、その外部変調器11の動作点をこの位相差が抑圧される動作点に保つ制御手段13とを備えた変調制御回路において、帰還を実現する帰還路に配置され、かつ変調信号の成分の内、この変調信号の波形に伴う波形の乱れに応じてその帰還路の通過域に分布し得る成分を抑圧する濾波手段14を備えて構成される。

(もっと読む)

アイドル時間ループスタビライザを備えた電荷ポンプPLLに基づいたバーストモード受信器

【課題】

【解決手段】バーストモード受信器は、入来信号を受信するデジタル位相検出器を含む。前記受信器はまた、前記デジタル位相検出器からのパルス信号を受信して、前記入来クロック位相と前記ローカル生成ロック位相を比較して前記電荷ポンプを制御する電荷ポンプと、前記電荷ポンプからの電荷値を受信し、制御信号を生成するループフィルタと、前記制御信号を受信し、回復されたクロックを生成し、前記回復されたクロックをデジタル位相検出器に供給するローカルクロック生成器とを含む。

(もっと読む)

1 - 10 / 10

[ Back to top ]