Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

261 - 265 / 265

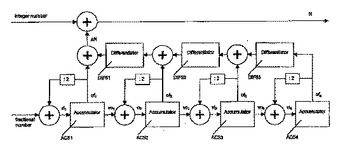

PLL回路のΣΔ変調器

PLL回路の比較分周器の分周比を変調する変調信号を生成するΣΔ変調器。複数の直列接続された積分器(9a〜9c)は、入力信号Fを積算するとともに、積算値が所定値を超えたときオーバーフロー信号OF1〜OF3を出力する。微分器(10a〜10e)は各積分器(9a〜9c)のオーバーフロー信号OF1〜OF3を転送する。加算器(11)は微分器から出力される出力信号(a〜f)に所定の係数を乗算し、その乗算値を加算する。終段の積分器(9c)と、その前段の積分器(9b)との間には、各積分器のクロック信号(fp)の分周信号に同期して積算値を転送する制御回路(12)が接続されている。制御回路(12)を設けることにより、次数を減少させることなく、変調信号の変調幅が減少される。 (もっと読む)

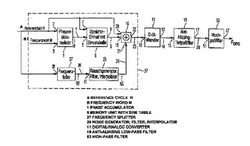

直接デジタル合成方式による周波数合成器

直接デジタル合成方式による周波数合成器は、入力(3)に存在する位相増分Mによって位相信号Pを周期的に増加するための位相アキュムレータ(1)と、位相信号Pの位相値に対応する正弦関数値を決定するため正弦関数値表をメモリーセルに記憶する記憶装置(6)と、時間対離散の正弦関数値を擬似アナログ正弦時間関数に変換するためのデジタル−アナログ変換器(11)と、擬似アナログ正弦時間関数を平滑化するためのアンチエイリアシングローパスフィルタ(16)とを備える。直接デジタル合成方式による周波数合成器はさらに、記憶装置(6)とデジタル−アナログ変換器(11)との間に接続された、時間対離散の正弦関数値に非周期的信号(NS)を重ね合わせる加算器(19)を含む。 (もっと読む)

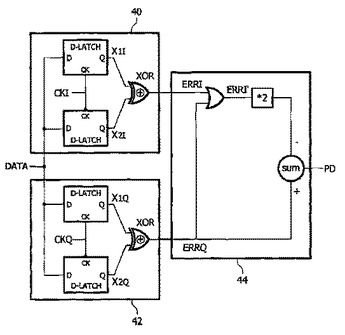

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

シグマデルタ変調器を有する可変周波数シンセサイザ

シグマデルタ変調器を有する可変周波数シンセサイザが提供される。そのようなシンセサイザは瞬時的な周波数が変化しても正確な平均周波数を与える。シグマデルタ変調器はカスケード接続された複数のアキュムレータ段を有する。シグマデルタ変調器の一部をなすアキュムレータ(51,52,53,54)の少なくとも1つの入力値は、ある因子の乗算されたオーバーフロー信号(of1,of2,of3,of4)に等しい第2成分を有する。このフィードバックは瞬時的な周波数の最大変動を減らす。位相検出器、チャージポンプ及びVCOの非線形性に起因して生じる位相ジッタはそれ故に減少する。

(もっと読む)

(もっと読む)

位相周波数検出器およびそれが組み込まれた位相ロックループ回路

【課題】 位相誤差信号に周波数差を加味した変形を加えることにより、周波数が離れているときでも短時間で位相同期を達成する。

【解決手段】 周波数が離れているときに生じる位相誤差信号の不連続なジャンプをジャンプ検出部30において検出し、検出信号により状態記憶部32の状態を遷移させる。保持部34において、状態記憶部32の状態に応じて位相誤差信号を修正して周波数位相誤差信号とする。

(もっと読む)

261 - 265 / 265

[ Back to top ]