Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

101 - 120 / 265

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部とを有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記分周信号の周波数と前記基準信号の周波数とを比較し、前記分周信号の周波数が前記基準信号の周波数に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

2点FSK変調を用いる周波数シンセサイザのための自己較正方法

【課題】2点FSK変調を用いる周波数シンセサイザの自己較正方法の提供。

【解決手段】周波数シンセサイザ1が、第1の位相ロック・ループおよび高周波アクセス部を備え、高周波アクセス部は、電圧制御発振器の第2の入力に接続されたデジタル/アナログ変換器20を備える。較正動作のために、高周波アクセス部に、第1の位相ロック・ループ内の位相比較器3に接続された第2の電荷ポンプ14および第2のループ・フィルタ15を備える。第2の電荷ポンプ14が、オンに切り替えられると、第2の位相ロック・ループを形成する。デジタル/アナログ変換器20の利得を較正するために、決められた出力周波数に予めロックされた第2の位相ロック・ループの第2の電荷ポンプ14を切り離した後に、電圧比較器21が、デジタル/アナログ変換器20の出力電圧を、第2のループ・フィルタ内に蓄えられた電圧と比較する。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。抵抗回路や容量回路をスイッチングすることなく、自然角周波数ωnとダンピングファクタζをそれぞれ自由に変えることが可能な、新しい位相同期回路が実現される。使用用途に合わせた位相同期回路の選択の幅を広げることができる。

(もっと読む)

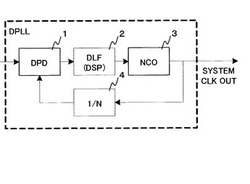

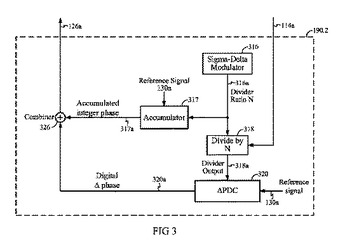

ディジタル位相ロックループにおける累算された位相−ディジタル変換

ディジタル位相ロックループ(DPLL)において信号の累算された位相をディジタル値に変換するための技術。模範的な実施形態では、信号が、分周器比Nで信号の周波数を分割するN分割モジュールと対にされる。分割された信号は、分割された信号の立ち上がりエッジと基準信号の立ち上がりエッジとの位相差を測定するデルタ位相−ディジタル変換器へ入力される。累算された分周器比群と較正された位相差群とが合算され、累算されたディジタル位相が生成される。シグマ−デルタ変調器を用いて分周器比Nを変える更なる技術が示される。  (もっと読む)

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

PLL回路並びに無線通信装置

【課題】発振器毎の変換利得を吸収し、いずれの発振器を用いても発振周波数を安定して収束させることができる、優れたPLL回路を提供する。

【解決手段】ビット・シフト量演算部は、ディジタル制御発振器の変換利得の概算値と、位相比較器の出力の下限値及び上限値に相当するデータ変換部の出力の下限値及び上限値に基づいて、当該PLLを収束させるために必要なビット・シフト量nを決定する。ビット・シフト回路は、ディジタル制御発振器へのディジタル制御データに対し、当該帰還ループを収束させるために必要となるビット・シフト量を与える。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムでも、オーバーヘッドが増大したり、MAC効率が極端に低下することなく、低コストでジッタを低減できるようにする。

【解決手段】開示されるPLL制御装置は、TIM抽出回路101と、2次PLL回路102と、時間分散制御回路103と、VCXO94とを備えている。TIM抽出回路101は、入力信号からタイミング成分を抽出する。2次PLL回路102は、抽出されたタイミング成分の位相及び/又は周波数に応じて自身のクロック信号の位相及び/又は周波数を制御する14ビットのデータを出力する。時間分散制御回路103は、2次PLL回路102から出力された14ビットのデータを10ビットのデータに時間的に分散して複数回に分けて出力する。これにより、VCXO94は、時間分散制御回路103から出力された10ビットのデータに基づいて、出力信号の周波数を制御する。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

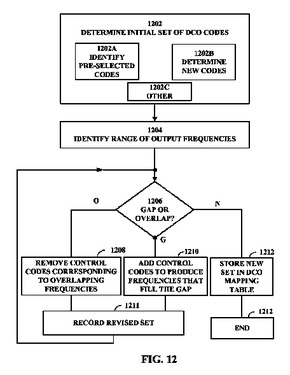

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

位相同期ループ回路

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

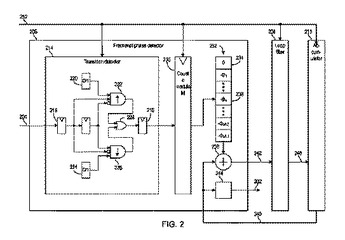

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するためのシステム及び方法

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するのに関係するシステム及び方法が開示される。ゲーティング窓は同時に電力の効率的方法でTDCを動作させながらDPLLの適切な動作を保証するために較正される。特に、その技術はTDCゲーティング窓の幅を既定値に設定すること;制御ループが実質的にロックされるまで、DPLLを動作させること;DPLLの位相誤差デバイスによって生成される位相誤差信号をモニターしながら、TDCゲーティング窓の幅を所定の量だけ減少させること;位相誤差が所定の閾値に実質的に到達するか、或いは横切るときにTDCゲーティング窓の現在の幅を決定すること;及びTDCゲーティング窓の動作幅の誤差のマージンに組込む所定の量だけTDCゲーティング窓の現在の幅を増加させることを要する。  (もっと読む)

(もっと読む)

101 - 120 / 265

[ Back to top ]