Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

181 - 200 / 265

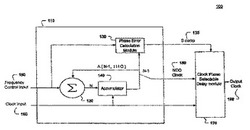

数値制御型オシレータ(NCO)出力クロック位相平滑化

【課題】 入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを発生する形態とされている数値制御型オシレータ(NCO)を包含する位相平滑化回路が記載される。

【解決手段】 該複数個のNCOクロックパルスのエッジは該入力クロックのエッジに整合している。位相エラー計算モジュールが該NCOへ結合されており且つ該複数個のNCOクロックパルスの各々に対する対応する位相エラーを発生する形態とされている。クロック位相選択可能遅延が該位相エラー計算モジュールへ結合されており且つ該選択可能周波数において出力クロックを発生するために該対応する位相エラーに従って該複数個のNCOクロックパルスの各々を調節する形態とされている。

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

PLL回路及び情報記録装置並びに記録用クロックの生成方法

【課題】ディスク状記録媒体に記録されたウォブル信号から生成したウォブルクロックに基づいて記録用クロックを精度よく生成すること。

【解決手段】所定の周期を有するウォブル信号が記録されたディスク状記録媒体に情報を記録するための記録用クロックを生成するために用いられる参照クロックを生成するPLL回路において、ウォブル信号に基づいて生成されるウォブルクロックの位相と参照クロックの分周クロックの位相とを比較し、その結果に基づいて、ウォブルクロックと参照クロックの分周クロックとの位相ずれ量とその位相ずれ位置とを検出し、記憶する。このように記憶した位相ずれ量及び位相ずれ位置に基づいてウォブルクロックの位相と参照クロックの分周クロックの位相との比較結果を補正し、この補正に応じた周波数の信号を参照クロックとして生成する。

(もっと読む)

キャリブレーション装置、試験装置、キャリブレーション方法、帯域測定装置、及び帯域測定方法

【課題】PLL回路に対して、予め定められたループ帯域を精度よく設定できるキャリブレーション装置を提供する。

【解決手段】PLL回路の電圧制御発振器に入力される制御電圧に、ループ帯域のカットオフ周波数の周波数成分を含むキャリブレーション信号を重畳する信号重畳部と、電圧制御発振器が出力する発振信号のカットオフ周波数の周波数成分を測定する測定部と、キャリブレーション信号のカットオフ周波数成分の強度と、測定部が測定した周波数成分の強度とを比較する演算部と、演算部における比較結果に基づいて、PLL回路に設けられたチャージポンプのゲインを調整する調整部とを備えるキャリブレーション装置を提供する。

(もっと読む)

位相比較信号処理回路

【課題】PLLのデジタル位相比較器の出力矩形波信号を処理し、PLLの引き込み可能な周波数幅を拡げ、同期時間を短縮する位相比較信号処理回路を提供する。

【解決手段】矩形波信号を両極性信号に変換する電圧シフタ7と出力端子22間に並列接続され、整流回路8と積分保持回路9と微分回路10とゲート回路12と電圧ホールド回路13と共通の加算回路14とからなる第1信号路、及び、整流回路15と積分保持回路16と微分回路17とゲート回路19と電圧ホールド回路20と前記加算回路14とからなる第2信号路、第1信号路及び第2信号路の積分保持回路9、16とゲート回路12、19を個別制御する制御信号発生器21を備え、第1及び第2信号路で、両極性信号の整流、整流電圧の積分保持、積分保持値の微分、微分出力の保持、保持電圧の加算を行うことにより処理信号を出力する。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】入力される基準クロック信号に基づく変調波を生成するスペクトラム拡散クロック発生回路であって、回路の製造プロセス、電源、又は、温度等に起因する変調波の変動を低減するスペクトラム拡散クロック発生回路を提供すること。

【解決手段】出力信号を分周した分周出力信号を出力する分周器と、前記分周出力信号と受信した基準クロック信号との位相差を検出する位相比較器と、前記位相差に応じて充放電信号を発生するチャージポンプと、前記充放電信号に応じた差信号を発生するループフィルタと、前記差信号と変調波とが入力されて被変調波を生成する変調回路と、前記被変調波に応じた周波数のクロックを発生するクロック発生器とを有するスペクトラム拡散クロック発生回路であって、前記基準クロック信号に基づき前記変調波を生成する変調波生成回路を有するスペクトラム拡散クロック発生回路。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

変調回路方式及びその電圧制御発振器

【課題】PLLループの電圧制御発振器にかかる回路負担を抑えることにより、電圧制御発振器の性能が低下することの無い変調回路方式及びその電圧制御発振器を提供することを目的とする。

【解決手段】電圧制御発振器12を具備するPLLループと、変調信号とPLLループ外調整電圧とを加算する加算手段17と、加算手段17の出力を電圧制御発振器12へ供給する周波数粗調整手段18とを有し、加算手段17において加算されて出力された、変調信号とPLLループ外調整電圧との加算信号を、周波数粗調整手段18を介して電圧制御発振器12へ供給し、PLLループにおける電圧制御発振器12の発振周波数信号に加算信号を重畳して変調信号を生成する。

(もっと読む)

信号発生装置、試験装置、及びPLL回路

【課題】振幅を高精度に制御した信号を生成することができる装置を提供する。

【解決手段】予め設定された振幅値を有する出力信号を生成する信号発生装置であって、入力信号の振幅を、与えられる制御信号の電圧値に応じて制御して出力する振幅制御部と、振幅制御部が出力する信号を予め設定される増幅率で増幅し、出力信号を生成する増幅部と、出力信号の振幅を検出する振幅検出部と、振幅検出部が検出した振幅値と、予め設定された振幅値との差分に応じた電圧値の制御信号を振幅制御部に供給する振幅比較部と、振幅検出部が検出した出力信号の振幅に基づいて、制御信号の電圧値を補正する補正部とを備える信号発生装置を提供する。

(もっと読む)

雑音除去を有するループフィルタ

【解決手段】 ループフィルタは、第1及び第2の信号経路720,730、演算増幅器(オペアンプ)736及び雑音除去経路740を含む。第1の信号経路720は、第1の信号に第1の伝達関数を供給する。第2の信号経路730は、第2の信号に第2の伝達関数を供給する。第2の信号は、第1の信号のスケール化バージョンである。キャパシタ734は、因子アルファだけ小さくスケールされる。オペアンプは、第1及び第2の信号経路に結合され、オペアンプ雑音を有する制御信号VCTRLを生成するために第1及び第2の信号経路からの信号を合計することを容易にするように形成される。雑音除去経路740は、オペアンプに結合され、制御信号中のオペアンプ雑音を相殺するのに使用される雑音除去信号VCTRLを生成する。制御信号VCTRL及び雑音消去信号VNは、電圧制御発振器(VCO)内に含まれるバリキャップ750の各ノードに適用される。 (もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

周波数シンセサイザ

【課題】新規な原理により、広帯域に亘って細かく周波数を設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供すること。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを作成し、電圧制御発振部の出力周波数が設定値になったときのベクトルの周波数を予め計算しておいて、電圧制御発振部を駆動したときにベクトルの周波数と前記計算された周波数との差分に相当する電圧信号を電圧制御発振部にフィードバックして、その差分がゼロになるようにPLLを形成する。従ってPLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整される。またPLLのロック後に両者の開きが大きくなった後は設定値を積分回路部により積分して制御電圧に加える。

(もっと読む)

ディジタル処理装置のノイズ低減方式

【課題】ディジタル信号処理回路によってPLLや周波数シンセサイザ等を構成するディジタル処理装置のノイズ低減を確実、容易にする。

【解決手段】PLLの位相比較演算を行うディジタル処理デバイス115をディジタル信号処理回路115A〜115Cで構成する周波数シンセサイザにおいて、ノイズ低減部115Dは、多数の論理回路要素がほぼ同時にオン/オフ動作するディジタルローパスフィルタ115Bと同等のオン/オフ動作になる回路構成にし、かつフィルタ115Bのオン/オフ動作と逆のオン/オフ動作させることでノイズを低減する。

(もっと読む)

位相ロック・ループにおいて単一イベントによる影響を軽減する方法

【課題】PLL回路において、位相差信号に対する放射イベントの影響を軽減する。

【解決手段】位相−周波数検出器12からの位相差信号は、チャージ・ポンプ24及び30、抵抗性の比例ループ・フィルタ26及び容量性の積分ループ・フィルタ32、バイアス発生器28及び34を介して、加算器40で加算され、VCO14,分周器16を介して検出器12にフィードバックされる。フィルタ26は、影響のスケーリング及びクリップを行って影響を位相差信号から排除し、フィルタ32は、容量性特性により影響を減衰させる。位相差信号が別個のフィルタ特性で処理されて結合されているので、突発的な影響によりPLL回路がロック状態から外れる可能性が低下する。

(もっと読む)

発振器及び周波数シンセサイザ

【課題】VCOの制御端子からみたインピーダンスを低くし、VCOの位相雑音特性の劣化を防ぎ、VCOに印加されるノイズを減少させ、スプリアスの発生を防止できる発振器及び周波数シンセサイザを提供する。

【解決手段】VCO9と、粗調用周波数のデジタルデータと微調用周波数のデジタルデータとを出力する制御回路3と、粗調用周波数のデジタルデータをアナログ信号で出力する粗調用DAC4と、微調用周波数のデジタルデータをアナログ信号で出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCO9の制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、制御電圧の平滑化を行う応答速度の速いLPF7と、両LPF5,7からの信号を合成する合成器8とを有し、VCO9、LPF5、LPF7、合成手段8をシールドケースに収納した発振器である。

(もっと読む)

PLL回路

【課題】主回路と主回路を模擬するダミー回路とを有するPLL回路において、電流源の製造誤差に基づく、基準クロックと帰還クロックとの位相オフセットを低減する。

【解決手段】開示されるPLL回路は、位相比較器PFD14で基準クロックと帰還クロックとの位相を比較してUP信号又はDOWN信号を出力し、PFD14を模擬する位相比較器PFD11で2入力の基準クロックの位相を比較してダミーUP信号又はダミーDOWN信号を出力して、UP信号又はダミーUP信号で流し込み側の電流源23Aを選択し、DOWN信号又はダミーDOWN信号で引き抜き側の電流源23Bを選択する。主回路のチャージポンプ(CP)の出力電圧とダミー回路のダミーCPの出力電圧との差分に応じて、電流源23A,23Bを制御してCP又はダミーCPを充放電して出力電圧を変化させるが、電流源23A,23Bは、CPの充放電に使用しない期間に、ダミーCPの充放電に使用される。

(もっと読む)

クロック信号のデューティサイクルを補正するための補正装置

【課題】クロック信号のデューティサイクル補正を行うために、確実かつ簡便に実現される技術を提供する。

【解決手段】クロック信号(CLK)から第1グループおよび第2グループのn個の遅延された各バージョンをそれぞれ生成するために各遅延デバイス(DA、DB)を設ける。第1グループの各バージョンでは前側エッジが後側エッジに対して時間増分τだけずつ段階的に遅延し、第2グループの各バージョンでは後側エッジが前側エッジに対して時間増分τだけずつ段階的に遅延する。第1グループの信号が消失する点での遅延増分値の順序数xを確定する。第2グループの各信号が発振が消失する点での遅延増分値の順序数yを確定する。遅延補正デバイス(DC)を、x>yまたはx<yである場合にクロック信号のパルスの前側エッジまたは後側エッジを(V=τ×|x−y|/2)だけ遅延して補正クロック信号CLK’を得るために制御可能に設ける。

(もっと読む)

PLL回路

【課題】 既存の一つの固定周波数のOCXOと安価なAT−CUT水晶振動子によるVCXOとからなる、顧客の要求に応じたPLL回路を提供する。

【解決手段】 OCXO1からの基準周波数を第1,3の分周器2,9で分周し、VCXO8からの出力を第2,4の分周器3,10で分周し、第1の分周器2と第2の分周器3からの出力を位相比較器4で位相比較し、位相比較結果をLPF5で平滑化し、第3の分周器9と第4の分周器10からの出力を位相進み/遅れ検出器11で位相の進み又は遅れを検出し、当該検出結果を積分器12で積分して電圧を出力し、加算器6でLPF5からの出力と積分器12からの出力を加算し、第1の分周器2と第2の分周器3の出力周波数は、最大公約数で求められる周波数より高い周波数とし、第3の分周器9の出力と第4の分周器10の出力は、同じ周波数となるまで分周するPLL回路である。

(もっと読む)

クロック補正回路、移動体端末、基地局装置及びクロック補正方法

【課題】特定小電力無線システムに適用できる安価なクロック補正回路、移動体端末、基地局装置及びクロック補正方法を提供することができない。

【解決手段】チャネルに応じた周波数データを格納しチャネル選択信号により指定されるチャネルに応じた周波数データを出力する周波数データ格納回路と、周辺温度に応じて定められた周波数補正値と周波数データを用いて演算を行うことにより周波数設定値を算出する周波数補正回路と、クロック信号に基づいて第1の周波数を発生する電圧制御発振器と、第1の周波数と周波数設定値とを用いて演算を行うことにより所望の第2の周波数を生成するPLLとを備える。

(もっと読む)

ホールドオーバ機能付きDPLL回路

【課題】デジタル同期網に関し、特にホールドオーバ時において自走周波数制御のために温度補正を行った高精度な基準クロックを生成するホールドオーバ機能付きDPLL回路を提供する。

【解決手段】ホールドオーバ機能付きDPLL回路は、DDSを使用したDPLL回路のホールドオーバモードにおいて、ホールドオーバ検出時における固定のDDS制御値にスレーブ発振器の温度特性から算出した補正値を加算することで、前記DDS制御値を前記温度特性に応じて可変する。

(もっと読む)

181 - 200 / 265

[ Back to top ]