Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

141 - 160 / 265

クロックデータリカバリー回路

【課題】周波数オフセットによるジッタ耐性の低下を防止するクロックデータリカバリー回路を提供する。

【解決手段】ディジタル制御発振器107における発振周波数の変化が矩形パルス状になるようにし、その周波数変化パルスの高さと幅を制御パラメータとしてディジタル制御回路104、105、106に与える。

(もっと読む)

フェーズロックドループ回路

【課題】入力される水平同期信号に対して、サンプリングクロックの周期の値に制約されることなく、位相誤差量を低減することができるフェーズロックドループ回路を提供する。

【解決手段】入力される水平同期信号(H-sync)は、逓倍PLL回路2から出力される、周期が等しく、1/4周期分づつずれた位相関係の4種の第1〜第4サンプリングクロックによりサンプリング回路でそれぞれサンプリングされ、各サンプリングクロックに位相同期した4種の水平同期出力データが生成され、これらはさらに加算回路6で加算されて加算水平同期出力データが生成された後、位相比較器13に入力され、分周器14で分周されたシステムクロック(第1サンプリングクロック)と位相比較される。

(もっと読む)

PLL回路

【課題】位相比較器出力のビット数を極端に増やすことなくループを安定化するとともに、ループ誤差の低減と収束の応答性の向上を実現する。

【解決手段】DCO回路102の入力は、第1の可変利得回路103を介して位相比較器101の出力に接続される。また、設定値Aを設定する手段104と、分周比Nを入力する手段106を持ち、設定値Aを第1の可変利得回路103と等価な利得G2を有する第2の可変利得回路105で変換し、第1の加算回路107で分周比Nから減じた後、第1の可変利得回路103の出力と加算するための第2の加算回路108を持たせる。

(もっと読む)

位相雑音除去装置及び方法、受信装置及び方法、並びにプログラム

【課題】使用予定のダウンコンバータが複数ある場合でも、位相雑音を適切に除去する。

【解決手段】位相雑音除去回路31では、位相雑音量検出器41は、ダウンコンバータ22から供給されるIF信号から位相雑音量を検出し、ゲイン決定回路42は、位相雑音量に応じた、IF信号に対する位相同期で用いられるループゲインを示す対照表を複数有し、その複数の対照表のうちの1つに基づいて、検出される位相雑音量に応じたループゲインを決定し、位相同期回路43は、決定されたループゲインに基づいて、IF信号の位相雑音を除去する。本発明は、例えば、TV受像機等に適用できる。

(もっと読む)

PLL回路

【課題】 ループゲインを大きくすることができ、ループ利得が上がらない場合でも、ロック時の位相ノイズを良化できるPLL回路を提供する。

【解決手段】 入力端子1からの基準周波数を第1,3の分周器2,9で分周し、VCO8からの出力と発振器13からの出力をミキサ14で合成し、MCF15aで周波数を選択して、第2,4の分周器3,10で分周し、第1,第2の分周器2,3からの出力を位相比較器4で位相比較し、LPF5で平滑化し、第3,第4の分周器9,10からの出力を位相進み/遅れ検出器11で位相の進み又は遅れを検出し、積分器12で積分して電圧を出力し、加算器6でLPF5からの出力と積分器12からの出力を加算してVCO8に出力し、MCF15aからの出力を増幅器16で増幅して出力端子17に出力し、基準周波数に対して発振器13での周波数を調整するPLL回路である。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報を元に得られるAGC回路における補正値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】 入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910からの信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られた信号PSA1,PSA2を生成する。これらの信号PSA1,PSA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相に基づいて、基準信号生成部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

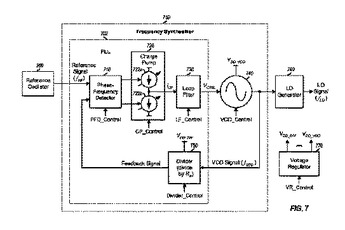

無線通信装置におけるシュプール軽減を伴う発振器信号生成

無線通信装置内で発振器信号を生成する技法を説明する。位相同期ループ(PLL)を使用して選択された周波数チャネルの発振器信号を生成することができる。異なるPLL設定を周波数チャネルのPLL内のブロックに使用することができる。異なるPLL設定は、異なるPLLループ帯域幅、チャージポンプ電流の異なる量、高分周比および低分周比の異なるセットに関連する異なる周波数方程式、異なるプリスケーラ比および/または異なる整数分周比に関連する異なる分周方式、スーパーヘテロダイン受信機または送信機の高側注入または低側注入、ならびに/あるいは発振器などの1つまたは複数の回路ブロックに対する異なる供給電圧に対するものとすることができる。PLL設定の適切なセットを、シュプールに起因する悪影響を軽減できるように周波数チャネル毎に選択することができる。  (もっと読む)

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

3次温度特性補償電圧発生回路、水晶発振器モジュールおよび電子機器

【課題】水晶の発振周波数温特の3次成分を補償するように3次温特補償電圧を制御したとき、広帯域にわたって制御しやすい3次温特補償電圧発生回路を提供する。

【解決手段】1次成分信号発生装置の出力を受けて3次関数で変化する信号を発生する3次成分信号発生装置1と、3次成分信号を増幅する第1の増幅率非線形可変増幅装置4と、1次成分信号を増幅する第1の増幅率線形可変増幅装置5と、それぞれの可変増幅装置の増幅率を制御信号により可変させる制御装置7と、それぞれの出力信号を加算し出力する加算器8とを備え、前記第1の増幅率非線形可変増幅装置4の増幅率可変量を、前記制御装置7からの制御信号に対して指数関数的に大きくすることにより、周波数軸での3次成分の制御分解能を一定とする。

(もっと読む)

シンボルタイミングリカバリ回路

【課題】入力信号のシンボルタイミングを再生するシンボルタイミングリカバリ回路の再生精度を向上させる。

【解決手段】A/D変換器1は、入力信号をクロックCLK1でサンプリングする。FIRフィルタ2は、サンプリングデータからゼロクロス点/データ識別点のデータを生成する。間引き回路3は、クロックCLK2を利用してFIRフィルタ2の出力を間引く。位相比較器4は、間引き回路3の出力信号の位相誤差Δθを検出する。NCO20は、位相誤差Δθを積分して位相信号θを生成する。タップ係数演算部7は、位相信号θに従ってFIRフィルタ2のタップ係数を生成する。NCO20において、位相信号θが「π」を超えたとこには、その位相信号θから「2π+Δθ」を減算する。

(もっと読む)

PLL回路、記録装置及びクロック信号生成方法

【課題】入力信号の振幅変動によるPLL回路の位相誤差を簡便に低減することができるPLL回路、記録装置及びクロック信号生成方法を提供する。

【解決手段】所定の周波数を有する入力信号に同期したクロック信号を生成するPLL回路100を提供する。このPLL回路100は、クロック信号を発振する発振器110と、発振器110が発振したクロック信号をサンプリングクロックとして用いて、入力信号をデジタル信号に変換する変換器120と、発振器110が発振したクロック信号を分周し、比較クロック信号としてフィードバックする分周器140と、変換器120が変換したデジタル信号の振幅値を正規化する正規化器130と、正規化器130が正規化したデジタル信号と分周器140がフィードバックした比較クロック信号との位相差を減少させるように、発振器110が発振するクロック信号の位相を制御する発振制御器150と、を備える。

(もっと読む)

ADPLL周波数シンセサイザ

【課題】DCO利得正規化回路を用いることなく制御感度を適切に推定することで、デジタル制御発振器の発振周波数が変化しても位相雑音特性が変化しないADPLL周波数シンセサイザを提供する。

【解決手段】周波数設定ワードがFCW0からFCW2へ変更される場合、制御感度推定部12は、ダミーであるFCW1である時の発振周波数f1をまず測定し、次にFCW2である時の発振周波数f2を測定する。そして、制御感度推定部12は、発振周波数f1及びf2の値からFCW2時の制御感度KDCO2を計算する。ループフィルタ13は、制御感度KDCO2の値に基づいて、予め設計した固有周波数ωn及びダンピングファクタζとなるように、フィルタ係数α2及びρ2の値を決定する。

(もっと読む)

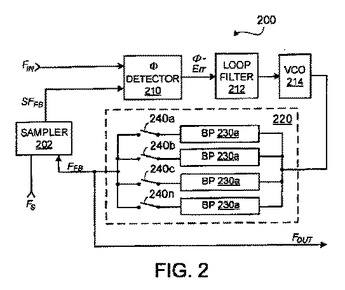

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

パイロットPLL回路及びFMステレオ復調回路

【課題】制御特性を向上させることが可能なパイロットPLL回路を提供することを目的とする。

【解決手段】制御データを与えられて出力周波数が変化するNCO31、出力周波数を与えられ第1の周波数の余弦波データを出力するROMテーブル32、FM復調データと第1の周波数の余弦波データとを与えられて乗算し乗算結果を出力する乗算器33、乗算結果を積分した累積加算データを出力する積分器35、乗算結果を与えられFM復調データと出力周波数との間の周波数偏差信号を出力するLPF34、累積加算データと周波数偏差信号とを加算して制御データを出力する加算器36、FM復調データのパイロット信号成分を検出してパイロット信号検出信号を出力するパイロット信号検出回路50を備え、積分器は累積加算データの値をパイロット信号検出信号に応じて制御する。

(もっと読む)

入出力回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを最適化するSERDES回路の提供。

【解決手段】SERDE回路において、クロックアンドデータリカバリ回路(14)は、位相オフセット信号(31)と閾値電圧制御信号(32)を用いて、時間方向と電圧方向の動作余裕度を測定可能し、伝送路におけるISIを低減するためにプリエンファシスドライバ回路(21)とイコライザ回路(22)と、全体を制御するための最適化制御回路(23)を備え、最適化制御回路(23)は、イコライザ回路(22)の特性を調整するイコライザ制御信号(33)、プリエンファアイスドライバ回路(21)の特性を調整するドライバ制御信号(34)を制御可能であり、クロックアンドデータリカバリ回路(14)の動作余裕度を最大化するように設定することができる。

(もっと読む)

周波数掃引発振回路

【課題】温度変化等の環境条件の変化やデバイス自体の特性変動要因があっても、掃引される周波数の安定度が高く、また高速な周波数掃引ができるようにする。

【解決手段】VCO26に電子同調電圧を入力し、周波数掃引を行う周波数掃引発振回路で、上記VCO26の出力周波数を分周器31で分周した周波数信号と基準信号源32で得られた基準(絶対)周波数信号とにおける両方の位相及び周波数をPFD33で比較し、このPFD33の出力に基づき上記分周器出力周波数が基準周波数と一致したときのVCO26の電子同調電圧を求め、この電圧によって掃引周波数を校正する。例えば、上記基準周波数を24GHz帯の占有帯域幅の中心周波数に設定し、この中心周波数の校正により占有帯域幅での安定した周波数掃引が行われる。また、幅設定回路を設け、掃引のためのサンプリングポイント数を一定に保ちながら、掃引幅を変えることができる。

(もっと読む)

141 - 160 / 265

[ Back to top ]