Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

61 - 80 / 265

半導体装置

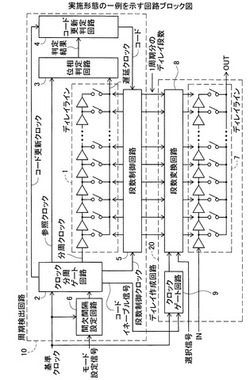

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

周波数測定回路及びそれを有するPLLシンセサイザ

【課題】

被測定クロックの周期または周波数を高精度に計測する周波数計測回路を提供する。

【解決手段】

周波数測定回路は,被測定クロックの被測定エッジをカウントするカウンタと,基準クロックの基準エッジに応答して,前記カウンタのカウント値を記憶するカウンタラッチ回路と,直列に接続された複数の基本遅延回路を有し,前記被測定クロックを初段の前記基本遅延回路に入力して伝搬させる遅延回路と,前記基準エッジに応答して,前記遅延回路の複数の基本遅延回路の出力をそれぞれラッチする複数の遅延ラッチ回路と,前記遅延ラッチ回路がラッチした前記複数の基本遅延回路の出力に基づいて,前記被測定クロックの前記被測定エッジの前記遅延回路内での位置を検出するエッジ検出回路と,2つの基準エッジ間の前記カウント値と,前記2つの基準エッジでの前記第1のエッジ検出回路が検出する前記被測定エッジの位置情報とから,前記被測定クロックの周期または周波数を演算する演算器とを有する。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

発振回路

【課題】 本発明は、出力信号の発振周波数の精度を向上させることができる発振回路を提供することを目的とする。

【解決手段】 圧電素子の周波数温度特性を補償するための補償電圧S150を生成する補償電圧生成部160と、制御電圧S130に補償電圧S150を加算することにより、補正制御電圧S160を生成する加算部150と、補正制御電圧S160に基づいて、発振周波数を変化させることにより、所望の発振周波数を有する出力信号S170を生成し出力する電圧制御発振部220とを備える。

(もっと読む)

位相調整装置及び方法

【課題】CCDを駆動するクロック信号を自動的に最適な位相に調整し、CCDからクロック信号成分が出力されない位相調整装置及び方法を提供する。

【解決手段】本発明の位相調整装置は、2相駆動型の電荷結合素子を用いたフィルタ回路に入力する第1の信号及び第2の信号の位相関係を調整する位相調整装置において、第1の信号に対して遅延を与える遅延付与手段と、遅延付与手段により遅延が与えられた第1の信号と、第2の信号とを加算又は減算する合成手段と、合成手段から出力する参照信号の電力値に基づいて、第1の信号と第2の信号とが逆位相となるように遅延付与手段の遅延設定量を制御する位相調整制御手段とを備えることを特徴とする。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

スペクトラム拡散クロックジェネレータ、回路装置、画像読取装置、画像形成装置、及びスペクトラム拡散クロック生成方法

【課題】周波数変調幅を高精度に合わせることができるようにする。

【解決手段】入力クロックとフィードバッククロックとの位相差を検出する位相比較器2と、位相比較器2からの位相差信号に応じて電流を供給するチャージポンプ3と、チャージポンプ3の出力を電圧に変換し、平滑化するループフィルタ4と、入力電圧に応じた周波数のクロックを発生させる電圧制御発振器6と、変調幅設定値に応じた振幅を持つ変調信号を生成する変調生成部8とを有し、ループフィルタ4の出力と変調生成部8から出力される変調信号とを加算した信号を電圧制御発振器6に印加し、スペクトラム拡散クロックを生成する際、電圧制御発振器6で生成されたスペクトル拡散クロックの変調幅を検出し、検出した変調幅と変調幅目標値を比較し、その差分を小さくするように新たに算出した変調幅設定値を変調生成部8にフィードバックする変調幅検出部10を備えた。

(もっと読む)

PLL回路

【課題】位相比較周波数を高く保ち、PLLの位相雑音を改善し、出力信号の精度を向上させたPLL回路を提供する。

【解決手段】基準信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した基準信号の位相に相当する信号を出力する第1位相アキュムレータ1、発振器の出力信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した発振器の出力信号の位相に相当する信号を出力する第2位相アキュムレータ2、第1及び第2位相アキュムレータの出力信号を比較して差を求め基準信号と発振器の出力信号との位相差を示す出力信号を出力する位相比較器3、位相比較器の出力信号に従って発振器への制御信号を生成する制御部4、制御部からの制御信号に応じた周波数の信号を出力する上記発振器5を有す。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

PLL回路

【課題】ループ内の無駄時間を補償し、所望の特性を取得可能なPLL回路を提供する。

【解決手段】メインパス110は、入力段に配置され、入力信号と実信号との位相検出を行うフェーズディテクタ111と、フェーズディテクタの出力側に配置され、ループの応答特性を決めるためのループフィルタ113と、ループフィルタの出力信号に応じた周波数で発振し、発振信号を実信号としてメイン帰還パスに出力する制御発振器114と、を含み、ローカル帰還パス130は、ループフィルタの出力が入力され、制御発振器のレプリカとして機能するレプリカ部131と、レプリカ部の出力を一巡無駄時間分遅延させる遅延部132と、遅延部の入力信号と出力信号の差分を得る第1の減算器133と、第1の減算部の出力信号からループフィルタ中の内部信号を定数倍した信号を減算し、ループフィルタの入力側に出力する第2の減算器136と、を含む。

(もっと読む)

位相補正装置、位相補正方法

【課題】無線送信用の電力増幅器の出力をフィードバックする位相補正装置及び位相補正方法において、フィードバック系の安定性を向上させたものを提供すること。

【解決手段】位相検出器10により検出された位相誤差(電圧CV)に対して、想定される位相誤差の全範囲でスイープさせた位相量(スイープ信号の電圧VSWP)を付加して、位相補正の目標値(電圧CV’)とする。これにより、位相補正処理の初期において、PLLのロックレンジへの引き込みを素早く行う。

(もっと読む)

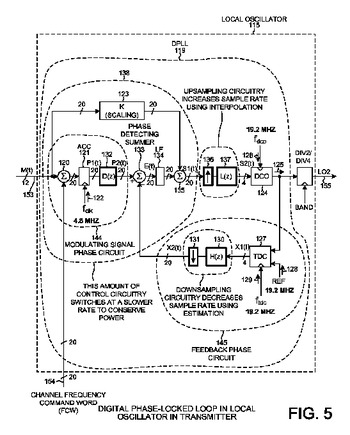

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

61 - 80 / 265

[ Back to top ]