Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

41 - 60 / 265

多相信号を生成する方法及び回路

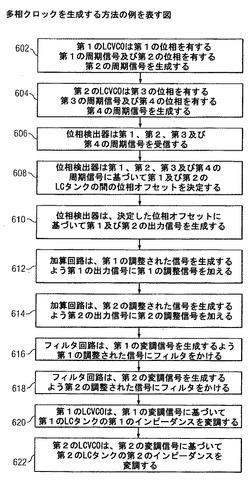

【課題】2つの結合されたLCVCOにおいて生じる多相クロック信号の位相誤差を改善し、制御可能な位相オフセットでクロック信号を生成する方法を提供する。

【解決手段】方法は、LCVCOによって第1のLCタンクの共振周波数に基づく第1の位相を有する第1の周期信号を生成するステップと、第2のLCVCOによって第2のLCタンクの共振周波数に基づく第2の位相を有する第2の周期信号を生成するステップと、第1及び第2の周期信号に基づいて第1及び第2のLCタンクの間の位相オフセットを決定するステップと、決定された位相オフセットに基づいて第1及び第2の出力信号を生成するステップと、所定の位相オフセットと略等しくなるよう位相オフセットを調整するステップとを有する。調整ステップは、第1の出力信号に基づいて第1のLCタンクの第1のインピーダンスを変調するステップ、及び/又は、第2の出力信号に基づいて第2のLCタンクの第2のインピーダンスを変調するステップを有する。

(もっと読む)

全デジタル位相ロックループ

【課題】周波数差の変化を正しくDCOに伝達し、且つグリッチノイズを低減する。

【解決手段】一つの実施形態の全デジタル位相ロックループ90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。グリッチ発生期間検出回路2は、小数部周波数差生成回路12から出力されるTDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のときに周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

回路、制御システム、制御方法及びプログラム

【課題】ジッタ・ワンダ抑圧性能を満足しつつ、高速な周波数追従性能を実現することが可能な回路を提供する。

【解決手段】本実施形態の回路は、OTN(Optical Transport Network)信号からSDH(Synchronous Digital Hierarchy)信号及びEthernet信号のクロックを再生するPLL部100の位相比較データを基に、ジッタ・ワンダ成分及び周波数急変状態を検出、解析し、その結果を基に、PLL部100のループゲインを制御することを特徴とする。

(もっと読む)

周波数制御回路及び出力周波数制御方法

【課題】接地電位が変動した場合においても、通信品質の劣化が生じない周波数制御回路及び出力周波数制御方法を提供すること

【解決手段】本発明にかかる周波数制御回路は、入力電圧に応じて出力周波数を変化させる電圧制御発振器10と、電圧制御発振器10から出力される出力周波数と基準周波数との位相差を検出し、当該位相差に応じて出力電圧を変化させる位相検出器11と、電圧制御発振器10における接地電位と位相検出器11における基準接地電位との間に発生する抵抗によって生じる電位差を、出力電圧に加算して電圧制御発振器10へ出力する加算器12と、を備えるものである。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

クロック生成回路と半導体装置及びクロック生成方法

【課題】スペクトルの抑圧効果の高い変調波形を得ることができ、Hershey−kissによる変調方式と比べ、回路規模を小さくするクロック生成回路の提供。

【解決手段】変調波形生成部20は、SSCG変調波形として、tan波形またはtan+三角波を生成し、PLLループの低域パスフィルタ14の出力に、該SSCG変調波形を合成した信号を発振器(VCO)15に与える。

(もっと読む)

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

41 - 60 / 265

[ Back to top ]