Fターム[5J106DD33]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | メモリ回路 (179)

Fターム[5J106DD33]に分類される特許

1 - 20 / 179

PLL回路

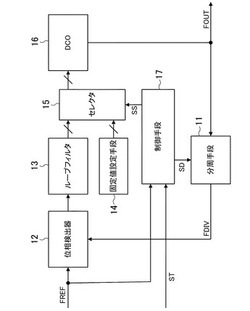

【課題】デジタル制御発振器を用いるPLL回路において高速に引き込みを行う。

【解決手段】PLL回路は、当該PLL回路の出力を分周する分周手段(11)と、基準クロック信号と分周手段(11)の出力信号との位相差を検出する位相検出器(12)と、位相検出器の出力信号をフィルタリングして、当該フィルタリング結果をデジタル値として出力するループフィルタ(13)と、デジタル値と固定値とのいずれか1つを選択するセレクタ(15)と、セレクタ(15)で選択された値に応じた周波数で発振するデジタル制御発振器(16)と、スタート信号を受けるまではセレクタ(15)に対して固定値の選択を指示し、スタート信号を受けてから基準クロック信号のエッジタイミングでセレクタ(15)に対してデジタル値の選択を指示するとともに分周手段(11)に対して出力の開始を指示する制御手段(17)とを備えている。

(もっと読む)

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

制御装置、光受信装置および制御方法

【課題】特性の制御を安定させること。

【解決手段】制御装置120は、第1演算器122と、更新制御回路123と、取得部125と、第2演算器126と、を備えている。第1演算器122は、処理装置の第1特性の検出結果に基づいて、第1特性を変化させる処理装置のパラメータを操作する。更新制御回路123は、第1演算器122の機能を更新する場合に、第1演算器122によるパラメータの操作を停止させる。取得部125は、パラメータの操作量と、第1特性を変化させる処理装置の第2特性の変化量との関係を示す関係情報を取得する。第2演算器126は、更新制御回路123によって第1演算器122によるパラメータの操作が停止している場合に、取得部125によって取得された関係情報と、第2特性の検出結果の変化量と、に基づく操作量によってパラメータを操作する。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

【課題】デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作を提供する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

(もっと読む)

画像処理装置

【課題】スペクトラム拡散クロックを画像データにより変調した信号を用いて画像を描画する場合に、スペクトラム拡散クロックの生成に用いる変調信号の周期性が画像に与える影響を小さくする。

【解決手段】画像形成装置は水平同期信号として機能するBD信号を生成するBD信号生成部と、スペクトラム拡散クロックCLK2を生成するクロック生成部301とを備える。クロック生成部301はPLL回路に変調信号生成部41を加えた構成を有する。変調信号生成部41は変調信号SG1の周期T1とBD信号の周期T2とが下記式を満たす変調信号SG1を生成する。

T2=T1×(n+0.5)

nは正の整数

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

発振装置

【課題】環境温度の検出結果に基づいて出力周波数を補正する発振装置において、出力周波数の温度補償を高精度に行うこと。

【解決手段】共通の水晶片により第1及び第2の水晶振動子を構成すると共に、これら水晶振動子に夫々接続される第1及び第2の発振回路の発振出力をf1、f2とし、基準温度における第1及び第2の発振回路の発振周波数を夫々f1r、f2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分である周波数差をそのときの温度として取り扱う。そしてこの周波数差に基づいて多項式近似により周波数補正値を求める。

(もっと読む)

周波数シンセサイザ装置及びその製造システム

【課題】 多数の類似機種を製造する場合でも、製造工程や検査工程における人為的なミスをなくし、適正な仕様とすることができる周波数シンセサイザ装置及びその製造システムを提供する。

【解決手段】 周波数シンセサイザ装置1のハードウェア識別子回路13が機種に対応するハードウェア識別子を記憶し、外部PC2が複数のハードウェア識別子とそれに対応するパラメータを記憶しており、マイクロコントローラ12が、外部PC2からハードウェア識別子の要求を受信すると、ハードウェア識別子回路13からハードウェア識別子を読み取って外部PC2に出力し、外部PC2が、周波数シンセサイザ装置1から取得したハードウェア識別子に対応して記憶されているパラメータを読み取って周波数シンセサイザ装置1に出力し、マイクロコントローラ12が、受信したパラメータを不揮発性メモリ14に記憶する周波数シンセサイザ装置及びその製造システムとしている。

(もっと読む)

同期回路

【課題】基準信号に異常が発生した場合でも大きな位相ずれ量が発生しない同期信号(タイミング信号)を出力する同期回路を提供する。

【解決手段】同期回路1は、発振器クロック信号を発生する電圧制御発振器16と、第1の基準クロック信号及び第2の基準クロック信号を含む複数の基準クロック信号と前記発振器クロック信号との間のそれぞれの位相ずれ量を検出する位相ずれ量検出部12と、前記複数の基準クロック信号の状態に応じた制御信号に基づいて同期信号を出力する同期信号処理部13,14と、前記同期信号と前記発振器クロック信号との間の位相ずれ量に応じて電圧制御発振器16のコントロール電圧を生成するコントロール電圧生成部15とを備える。

(もっと読む)

デルタシグマ変調型分数分周PLL周波数シンセサイザおよびそれを備えた無線通信装置

【課題】デルタシグマ変調型分数分周PLL周波数シンセサイザにおいて、スプリアスを抑制し、さらに、位相雑音特性を良好に保つ。

【解決手段】分周器(25)を変調することで分数分周を行うデルタシグマ変調型分数分周PLL周波数シンセサイザは、分数部データKに加算すべきシフト量Sを求め、シフト量Sと、シフト後分数部データK2とをそれぞれ出力する演算処理手段(27)と、シフト後分数部データK2を積分して量子化する第1のデルタシグマ変調器(28)と、シフト量Sを積分して量子化する第2のデルタシグマ変調器(29)と、第1のデルタシグマ変調器(28)の出力系列と第2のデルタシグマ変調器(29)の符号反転出力とを加算する第1の加算器(30)と、整数部データMと第1の加算器(30)の出力とを加算する第2の加算器(31)とを備え、第2の加算器(31)の出力により分周器(25)を変調させる。

(もっと読む)

1 - 20 / 179

[ Back to top ]