Fターム[5J106KK16]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 動作、特性の安定化 (735) | 出力周波数 (67) | フリーラン周波数 (19)

Fターム[5J106KK16]に分類される特許

1 - 19 / 19

基準信号生成装置

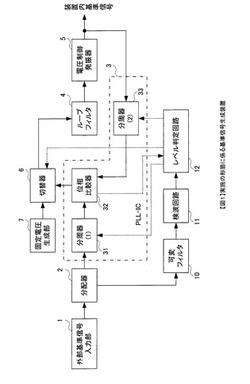

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

PLL回路

【課題】 エージング特性を自動補正し、外部基準信号の未接続又はアンロック時に出力周波数変動を小さくできるPLL回路を提供する。

【解決手段】 基準信号が適正範囲内でロック状態の場合に、初期調整時に、チャージポンプ出力電圧(A)の初期電圧を温度情報Tと共に読み取り、自走周波数設定用電圧(B)が電圧(A)となるようのDAコンバータ又はPWM出力回路9の設定値を調整し、温度特性初期テーブルを生成し、運用中に、温度情報Tにおける電圧(A)の最新電圧に対応する設定値を、温度特性初期テーブルを参照して特定し、初期電圧と最新電圧の設定値の差分で当該テーブルをオフセット補正して自走用温度補正テーブルを生成し、アンロック状態等になると特定された設定値による自走周波数設定用電圧(B)で自走するPLL回路である。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

デジタルPLL回路

【課題】

映像信号をサンプリングするためのサンプリングクロック信号として用いても、映像に乱れを生じさせないクロック信号を生成することのできるデジタルPLL回路を提供することを課題とする。

【解決手段】

映像信号のサンプリングに用いるサンプリングクロック信号として、入力電圧に応じた発振周波数のクロック信号を出力する電圧制御発振回路と、映像信号の制御に用いられる複合同期信号と、前記電圧制御発振回路の出力に基づく帰還信号との位相差を検出する位相差検出部と、前記位相差検出部で検出される位相差が所定の範囲内にある場合は当該位相差を選択して出力し、前記位相差検出部で検出される位相差が前記所定の範囲内にない場合は前記位相差検出部で検出される位相差の目標値を出力する出力部とを含み、前記出力部の出力に基づいて、前記電圧制御発振回路の入力電圧を制御する。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

クロックリカバリ回路

【課題】 クロック信号の切り替え時における不要成分の発生を効果的に抑制できるクロックリカバリ回路を提供する。

【解決手段】 異位相の選択クロック信号を複数の選択クロック信号群に分類し、前段選択制御信号により選択クロック信号の1つを前段出力クロック信号として出力する前段選択回路を、選択クロック信号群毎に備える前段選択回路群14と、後段選択制御信号により前段出力クロック信号の1つを再生クロック信号RCLKとして出力する後段選択回路15と、受信データと再生クロック信号RCLKの位相差に基づいて位相制御信号を出力する位相制御回路11と、位相制御信号により特定される選択クロック信号を選択する前段選択制御信号を出力する前段選択制御回路12と、切り替えが必要な場合に、現在の前段出力クロック信号と新たな前段出力クロック信号の論理値が同じになる期間に後段選択制御信号を出力する後段選択制御回路13を備える。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号に電圧制御発振部からの周波数信号を同期させて出力するPLL装置において、外部からの基準信号に不具合が生じても周波数の変動が抑えられるようにすること。

【解決手段】外部からの基準周波数信号の信号レベルを監視し、その信号レベルが設定範囲内であるときには、位相差データ作成手段により作成された位相差に関するデータを用いてPLL制御を行うが、前記信号レベルが設定外れたときには、信号の供給が停止あるいは異常が起きたものと認識して記憶部に記憶されている位相差に関するデータ、例えば蓄積している最新のデータあるいは予め作成しておいたデータに切り替えてPLL制御を行う。

(もっと読む)

ホールドオーバ機能付きDPLL回路

【課題】デジタル同期網に関し、特にホールドオーバ時において自走周波数制御のために温度補正を行った高精度な基準クロックを生成するホールドオーバ機能付きDPLL回路を提供する。

【解決手段】ホールドオーバ機能付きDPLL回路は、DDSを使用したDPLL回路のホールドオーバモードにおいて、ホールドオーバ検出時における固定のDDS制御値にスレーブ発振器の温度特性から算出した補正値を加算することで、前記DDS制御値を前記温度特性に応じて可変する。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

PLL回路

【課題】 電圧電流変換回路の抵抗値のばらつきを抑えることで、電圧制御発振器の発振周波数のばらつきを低減するPLL回路を提供する。

【解決手段】 電圧電流変換回路50は可変抵抗回路4と、リミット回路5と、カレント比調整回路6を備えて構成される。可変抵抗回路4を内蔵することで抵抗を内蔵した場合のプロセスばらつきを制御でき、かつ内蔵することで、外付抵抗端子の寄生容量の影響を受けずに済み、PLLループ帯域の影響を受けない高帯域で応答可能な電圧電流変換回路が実現できる。この可変抵抗回路4にCMOS可変抵抗を用いることで連続的な抵抗値調整を可能とする。

(もっと読む)

クロック再生装置

【課題】映像信号等の入力信号の劣化状況により、1次PLL回路と2次PLL回路の自走/ロック方法をフレキシブルに変更でき、劣化した入力信号に対しても、正常なクロック再生を可能とする。

【解決手段】1次PLL回路10及び2次PLL回路20を有する2段PLL回路において、1次PLL自走検出回路30は、入力信号の異常状態を検出して1次PLL回路10をアンロック状態に切り替えるための第1切替信号FD1を出力する。これにより、切替SW13が切り替えられ、定電圧発生器15から出力された定電圧がVCO14に与えられる。2次PLL自走検出回路40は、VCO14が自走状態で動作してしていることを検出して2次PLL回路20をアンロック状態に切り替えるための第2切替信号FD2を出力する。これにより、切替SW23が切り替えられ、定電圧発生器25から出力された定電圧がVCO24に与えられる。

(もっと読む)

半導体装置及び発振周波数補正方法

【課題】 本発明は、半導体装置の動作時の発振周波数の変動要因に対応できるとともに、特定の通信機能や通信相手を必要とすることなく、RC発振回路の発振周波数の補正が可能な半導体装置を提供することを目的とする。

【解決手段】 半導体装置は、第1の周期で発振する第1の発振信号を出力するRC発振器と、RC発振器の出力に結合され第1の発振信号の第1の周期の長さを第2の周期を有する第2の発振信号に基づき計測し、その計測値を出力する計測回路と、計測回路の出力とRC発振器の出力とに結合され計測値に応じた数で該第1の発振信号を分周する補正回路を含むことを特徴とする。

(もっと読む)

PLL発振装置の周波数調整方法

【課題】PLL発振装置を小型化する必要があった。

【解決手段】データ端子に下限使用周波数43より低い予め定められた第1の周波数データを入力する入力工程35と、この入力工程の後で、出力端子27から出力される周波数が前記下限使用周波数43より低い予め定められたローエンド周波数49になるように同調回路24を調整する調整工程36とを有するものである。

これにより、従来必要であった調整用端子が不要となり小型化が出来る。

(もっと読む)

PLL装置および受信機

【課題】受信状態や受信環境の悪化などによってPLL入力信号が不安定となる場合や途絶えてしまう場合でも、PLL回路内のVCOの発振周波数をPLL引き込み範囲内に確実に自動調整することができるようにする。

【解決手段】PLL回路部10に対してフリーラン周波数設定部20を設ける。フリーラン周波数設定部20の周波数比較回路22で、VCO11の発振周波数を基準周波数と比較し、両者の高低関係および差分に応じて、アップ信号Supおよびダウン信号Sdwを得る。そのアップ信号Supおよびダウン信号Sdwによって、フリーラン周波数調整回路23でフリーラン周波数調整電圧Vcfを生成し、VCO11に供給して、VCO11の発振周波数をPLL引き込み範囲内に設定する。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

1 - 19 / 19

[ Back to top ]