Fターム[5J106LL03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 周波数比較(弁別)回路 (13)

Fターム[5J106LL03]に分類される特許

1 - 13 / 13

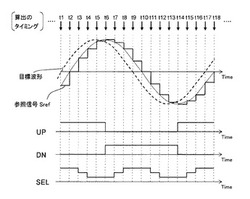

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

PLL回路

【課題】短時間に希望する周波数に収束するものであって、しかも使用するトランジスタの個数を減らして、コンパクトかつ安価に構成できるPLL回路を提供する。

【解決手段】PLL回路は、基準信号S0と周波数信号S1もしくは比較信号S2とが入力される周波数一致検出回路60を備えている。この周波数一致検出回路60によって制御される電流制御回路として、バイアス回路80、分圧回路90、および分圧比制御回路100を備え、VCO40の出力信号である周波数信号S1が基準信号S0の周波数によって設定される周波数から大きく外れている場合、チャージポンプ回路20からローパスフィルタ30に出力される被積分電流を増加させるように制御し、反対に、周波数信号S1が基準信号S0の周波数に近い場合には被積分電流を減少させるように制御している。

(もっと読む)

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

周波数検出器または位相検出器で使用するための回路

トラッキングデータセル(10)は、第1のマルチプレクサ(5)に結合された一対のトラック及びホールド回路(1,1’)と、レートを有するデータ信号(D+,D−)の受信を決定するために各トラック及びホールド回路(1,1’)において実質的に逆位相で入力されるクロック信号(H+,H−)とを備え、上記トラック及びホールド回路(1,1’)は、ほぼハーフレートを有する出力信号(O)を供給する。  (もっと読む)

(もっと読む)

位相同期回路および情報再生装置

【課題】周波数比較精度の向上を図れ、安定かつ高速な周波数引き込みを実現することが可能なPLL回路および情報再生装置を提供する。

【解決手段】VCO23による3相クロックCLKA,CLKB,CLKCに同期してヒステリシスコンパレータ24によるヒステリシス信号HYCを取り込み、以降、たとえば第1相クロックCLKAに同期して、入力データ信号のヒステリシスのエッジがどの位相からどの位相に変化したか観察することにより周波数が高いか低いかを周波数誤差として検出する際に、ヒステリシスコンパレータ24にて取り除くことができなかった2Tパターンを、VCO23による3相クロックCLKA,CLKB,CLKCに同期してパルスの周期計測を行うことにより除去し、これにより検出結果に基づいたアップ信号UPまたはダウン信号DOWNをチャージポンプ回路26に出力する周波数比較器25を有する。

(もっと読む)

平衡型4相相関器を備えたPLL

平衡型4相相関器(2)を含む周波数検出器(10)を具備する位相ロックループ(1)であり、ループ(1)は4相相関器(2)が入力信号(D)と同じビットレートを有する信号によって制御されるマルチプレクサ(31,32,33,34)に接続されたダブルエッジクロック式双安定回路(21,22,23,24,25,26,27,28)を具備することを特徴とする。  (もっと読む)

(もっと読む)

非平衡型4相相関器を用いたPLL

4相相関器(2)を含む周波数検出器(10)を具備し、データおよびクロック再生で使用される位相ロックループ(1)であり、周波数検出器を構成する4相相関器(2)は、入力信号(D)と同じビットレートを有する信号によって制御される第1のマルチプレクサ(31)および第2のマルチプレクサ(32)に接続されたダブルエッジクロック式双安定回路(21,22,23,24)と、第1のマルチプレクサ(31)により供給される第1の信号ペア

【数1】

および第2のマルチプレクサ(32)により供給される第2の信号ペア

【数2】

によって制御される位相検出器(DFF)と、を含む。  (もっと読む)

(もっと読む)

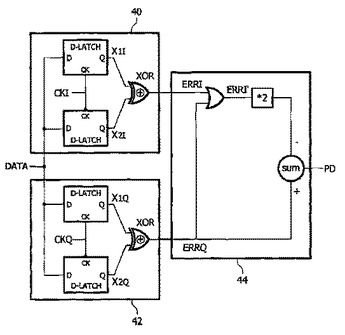

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]