Fターム[5J106PP05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 出力周波数可変方式 (219) | その他の手段によるもの (23)

Fターム[5J106PP05]に分類される特許

1 - 20 / 23

周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

低速ダイレクトコンバージョン方式FSK無線周波数信号受信機

【課題】FSK変調用のダイレクトコンバージョン方式無線周波数信号受信機を提供する。

【解決手段】受信機は低速FSK無線周波数信号を捕捉する。FSK無線周波数信号を受信するアンテナと、低雑音増幅器と、局部発振器と、移相回路とを含む。移相回路は同相及び直角位相発振信号、又は同相及び直角位相着信FSK無線周波数信号を交互かつ逐次的に生成する。発振信号を着信FSK無線周波数信号と逐次的に混合して、中間同相及び直角位相ベースバンド信号を移相回路の関数として交互に生成するための低域通過フィルタ、濾波信号からデータを復調するための復調段とを含む。FSK無線周波数信号における被変調データの周波数偏移よりも低く、かつデータ転送速度周波数よりも高い位相選択信号によって移相回路が切り換えられるように配置される。復調段の中のマジック回路が、復調器における連続的な復調のために、各切換動作中に中間信号を復元する。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

周波数シンセサイザ

【課題】回路規模が小さく、回路構成を簡単にする。

【解決手段】電圧制御発振器19が出力する信号を入力して分周する分周器11、12と、分周器11、12の出力信号を混合する周波数混合器13と、周波数混合器13が出力する2つの周波数の内の一方の周波数の信号を入力して分周する分周器14を、電圧制御発振器19と位相比較器17との間のPLL回路内の帰還ループ中に備える。位相比較器17は、分周器14が出力する信号を一方の入力端に入力し、基準信号発生器16が出力する基準クロック信号を他方の入力端に入力する。ループフィルタ18は、位相比較器17の位相比較結果に基づいた電圧を電圧制御発振器19に与える。電圧制御発振器19は、入力される電圧に対応した周波数で発振する信号を分周器11、12に与える。

(もっと読む)

デジタル周波数シンセサイザにおける利用のための方法

デジタル周波数シンセサイザ(100)における利用のための方法であり、上記方法は、上記シンセサイザ(100)中の位相アキュムレータ(110)の出力値の位相から振幅への変換(120)を含み、上記変換は、上記出力振幅値と対応する位相値(x)の近似(y)として実行され、並びに、上記近似が、線形補間値及び第2オーダー正弦関数値の組合せを含み、上記第2オーダー正弦関数値は、上記線形補間値における誤差を修正するための誤差タームとして用いられることを特徴とする、方法。 (もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

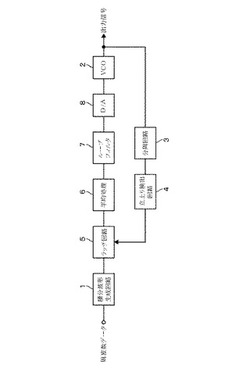

周波数シンセサイザ

【課題】超広帯域で使用する局発信号を生成するための構成において、低位相雑音化と低消費電力化を同時に実現する方法を提供する。

【解決手段】周波数シンセサイザにおいて、単一の周波数の信号を出力する基準信号発生器1と、入力信号の周波数を基に異なった周波数の中間信号を1つ以上生成して出力信号として出力する周波数マルチプライヤ2と、周波数セレクタ3と、ミキサ4と、周波数シンセサイザ制御端子を備えた周波数シンセサイザ制御回路5を備え、基準信号発生器1の出力を周波数マルチプライヤ2の入力とし、周波数マルチプライヤ2の1つ以上の出力を周波数セレクタ3の1つ以上の入力とし、周波数セレクタ3の出力と周波数マルチプライヤ2の出力のうち1つの出力をミキサ4の第1と第2の入力とし、ミキサ4の出力を周波数シンセサイザの出力とする。

(もっと読む)

高周波信号発生装置

【課題】数MHzから数GHzの周波数領域にわたる高周波信号を、非常に低いSSBノイズで安定して発生することができる高周波信号発生装置を提供する。

【解決手段】搬送波周波数f1の1/nにほぼ相当する第1高周波信号aを発振する高周波発振器11と、搬送波周波数f1にほぼ相当する第2高周波信号eを発振する電圧制御発振器15と、電圧制御発振器15の出力周波数fを1/nに分周する分周回路16と、第1高周波信号aと出力周波数fの1/nの第2高周波信号gの位相差に比例した誤差信号Veを出力する位相比較器12と、誤差信号Veに応じて制御電圧を電圧制御発振器15に入力するVCO制御回路13とを備え、VCO制御回路13は、SSBノイズが第1高周波信号aの方が第2高周波信号eのものより小さい周波数帯域では、誤差信号Veに比例する制御電圧を出力し、大きい周波数帯域では制御電圧を0にする。

(もっと読む)

周波数シンセサイザ

【課題】周波数ホッピングする無線システムに好適な周波数シンセサイザを提供すること。

【解決手段】多相入力信号から多相クロック信号を発生する多相クロック信号発生回路414と、多相クロック信号発生回路414を制御する第1の制御信号419を発生する制御回路418と、多相クロック信号発生回路414から出力された複数の多相クロック信号415を入力信号とし、複数の多相クロック信号415に基づいて一の出力クロック信号を発生する発生回路とを有する周波数シンセサイザであって、多相クロック信号発生回路414は複数の位相補間回路を有し、位相補間回路のそれぞれは、第1の位相を有する第1の入力信号と第2の位相を有する第2の入力信号とを入力信号とし、制御回路418からの第1の制御信号419に従って、第1の位相以上第2の位相以下の位相を有する出力信号を発生する。

(もっと読む)

広帯域高周波発振回路

【課題】地上デジタル放送の中継装置のローカル信号発生源として好適な広帯域高周波発振回路を提供する。

【解決手段】第1のPLLループ10のDDS回路16は、基準信号より高い周波数で発振する電圧制御水晶発振回路13の出力信号をシステムクロックとして基準信号と同一の周波数の信号Fc1を生成する。位相比較器11は、信号Fc1と基準信号とを位相比較して電圧制御水晶発振回路13を制御し参照信号Frefを生成する。第2のPLLループ20の電圧制御発振回路23a〜23cは、切換回路24により選択され、参照信号Frefによりローカル信号を生成する。DDS回路26は、ローカル信号を2分周し、システムクロックとして参照信号Frefと同一周波数の信号Fc2を生成する。位相比較器21は、信号Fc2と参照信号Frefを位相比較し、上記選択された電圧制御発振回路を周波数制御する。

(もっと読む)

周波数シンセサイザ、通信機、及び周波数シンセサイズ方法

【課題】高精度のクロックを高速に切り換えることの出来る周波数シンセサイザ、通信機、及び周波数シンセサイズ方法を提供する。

【解決手段】高精度に生成された基準クロックを元に、デジタル的な演算とD/Aコンバータ、ローパスフィルタを用いて所望の周波数の正弦波信号を発生させ、その正弦波信号を元の基準クロックとミキシングし、適切なフィルタを通す事で所望の周波数の正弦波を生成する事ができる。また、ミキシング後のバンドパスフィルタの中心周波数や、上記正弦波信号を発生させる演算処理、あるいは出力部のセレクタを変化させる事で、基準クロックの周波数を変更する事無く周波数切り換えを行うので、高速な周波数切り換えを実現する事ができる。周波数生成に用いる正弦波信号はデジタル的な演算によって生成されるので、周波数制御を精度良く行う事ができる。

(もっと読む)

PLL周波数シンセサイザ

【課題】チャンネル周波数が整数と分数との和で表現される複雑な周波数に適合可能なPLL周波数シンセサイザを提供することを目的とする。

【解決手段】マルチループ構成を持つPLL周波数シンセサイザであって、出力周波数の整数部分の比較周波数を設定するメインループ10と、出力周波数の分数部分の比較周波数を設定するサブループ15とを備え、メインループ10で設定された出力周波数の整数部分とサブループ15で設定された出力周波数の分数部分との和となる周波数を出力周波数として出力することにより上記課題を解決する。

(もっと読む)

多周波出力位相同期発振器

【課題】一つの位相同期回路を用いて多周波の出力信号を得ることが可能な多周波出力位相同期発振器を提供することを目的とする。

【解決手段】本発明に係る多周波出力位相同期発振器6は、外部から入力される基準信号と、後述する電圧制御発振器が出力する信号を分周した比較信号とを位相比較し位相差信号を発生する位相比較器2と、前記位相差信号の高周波成分を除去して直流電圧とするループフィルタ3と、ある一定の自走周波数を有し、前記直流電圧により発振周波数を変化させる電圧制御発振器4と、該電圧制御発振器4が出力する信号の周波数を複数の分周器のトータルで1/N分周し、前記位相比較器2に出力する分周器7、8、9、10とにより構成する。

(もっと読む)

スプレッドスペクトルクロック生成器及びスプレッドスペクトルクロック信号を生成する方法

【課題】スプレッドスペクトルクロック生成器(SSCG)及びスプレッドスペクトルクロック(SSC)信号を生成する方法を提供する。

【解決手段】第1フィードバック信号の平均周波数と受信された比較周波数信号との差に基づくか、第2フィードバック信号と比較周波数信号との総位相変化量に基づいて所定の変調電圧信号を出力する制御部、受信された既存周波数信号及び受信された第2フィードバック信号の機能で第1制御電圧を生成するサブシステムを備えるSSCGである。合算部は、第1制御電圧信号と変調電圧信号とを合算して第2制御電圧信号を生成し、電圧制御オシレータは、第2制御電圧信号に基づいてSSC信号を生成する。

(もっと読む)

1 - 20 / 23

[ Back to top ]