Fターム[5J500AA22]の内容

Fターム[5J500AA22]の下位に属するFターム

BTL増幅器 (79)

Fターム[5J500AA22]に分類される特許

1 - 20 / 152

全差動型帰還増幅回路および電気機器

制御回路および位相変調器

電力増幅器

【課題】本実施例の一側面における電力増幅器はトランジスタの入力側と出力側の両方に高調波処理を行う整合回路を設けた場合でも発振が生じるのを抑止し、電力増幅器の安定動作を可能とすることを目的とする。

【解決手段】本実施例の一側面における電力増幅器は、基本波と高調波を含む入力信号を入力ノードで受けとり、入力信号の電力を増幅することにより出力信号を生成し、生成された出力信号を出力ノードから出力する増幅回路と、増幅回路の入力ノードに接続され、入力信号の高調波処理を行う入力整合回路と、増幅回路の出力ノードに接続され、出力信号の高調波処理を行う出力整合回路を含む。増幅回路は、入力信号の電力が所定値より大きい値からその所定値より小さい値に低下したとき、生成される出力信号に含まれる高調波の整合点における出力インピーダンスの位相を回転させる。

(もっと読む)

音声出力アンプ

【課題】 チャネルセパレーションの改善が可能なヘッドホンアンプ等の音声出力アンプを提供する。

【解決手段】 ヘッドホンアンプ100は、スピーカSPLおよびSPRを各々駆動するLチャネル用増幅回路100LおよびRチャネル用増幅回路100Rを具備する。Lチャネル用増幅回路100LおよびRチャネル用増幅回路100Rの各々は、負荷であるスピーカに供給する電流の経路上に介挿された電流検出抵抗R5を有し、当該増幅回路に与えられる音声入力信号の電圧値に比例した電圧を電流検出抵抗R5の両端間に発生させる電流制御部130を有する。このヘッドホンアンプ100では、Lチャネル音声入力信号ALおよびRチャネル音声信号ARの各電圧値に比例した各電流をスピーカSPLおよびSPRに供給することができるのでチャネルセパレーションを高めることができる。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

電力増幅回路、および無線通信装置

【課題】回路面積を縮小しつつ、電力効率の向上を図ることが可能な電力増幅回路を提供する。

【解決手段】電力増幅回路は、シリコン基板上に集積された電力増幅回路である。電力増幅回路は、入力が第1の信号入力端子に接続された第1のアンプを備える。電力増幅回路は、入力が第2の信号入力端子に接続された第2のアンプを備える。電力増幅回路は、入力が前記第1のアンプの出力に接続され、出力が前記第2のアンプの出力に接続されたアンプ出力移相器を備える。電力増幅回路は、一端が電源に接続され、他端が前記アンプ出力移相器の出力に接続された一次側巻線と、一端が第1の信号出力端子に接続され、他端が第2の信号出力端子に接続された二次側巻線と、を有するトランスフォーマと、を備える。

(もっと読む)

増幅装置

【課題】 入力電圧が低く、特性を向上させた増幅装置を提供する。

【解決手段】 増幅装置は、一対の受光素子からそれぞれ入力された第1及び第2の電流信号In(+),In(−)を、第1及び第2の電圧信号Vo(−),Vo(+)にそれぞれ変換して出力する第1及び第2のトランスインピーダンスアンプ20と、第1及び第2の電流信号In(+),In(−)の各電流を分流する分流回路24と、第1及び第2の電圧信号Vo(−),Vo(+)の平均電圧値を示す平均信号を生成して出力する平均値検出回路と、平均信号Vav、及び第1及び第2の電圧信号Vo(−),Vo(+)のオフセット電圧値に基づいて、分流回路24に分流される第1及び第2の電流信号In(+),In(−)の各電流値を制御する制御回路23とを含む。

(もっと読む)

増幅システム

【課題】プラズマ生成時の負荷変動に高速に対応すると共に、自動インピーダンス制御回路の長寿命化を図ることが可能な増幅システムを提供する。

【解決手段】プラズマの生成によりインピーダンスが変動する負荷と接続する増幅システムは、入力線路、第1及び第2の増幅器、出力線路、接続線路及びインピーダンス制御回路を具備する。入力線路、出力線路及び接続線路の電気長は、駆動前調整により予め設定される。インピーダンス制御回路は、駆動前調整において、入力から前記負荷側を見たインピーダンスが第1のインピーダンスと等しくなるように制御する。駆動中には、第1の増幅器は、プラズマ生成前後において第1のインピーダンスを目標として信号を増幅する。第2の増幅器は、プラズマ生成前には増幅機能をオフとし、プラズマ生成後には第1のインピーダンスを目標として信号を増幅する。

(もっと読む)

増幅装置及び無線通信装置

【課題】LM方式の増幅装置において、DPDを実行するために信号を補正するための独立した機能を増幅装置に組み込むことなく、信号の補正を行うことができるようにする。

【解決手段】入力信号を増幅する増幅装置501であって、増幅器502と、増幅器502の出力側に接続された負荷変動部503と、負荷変動部503における負荷を変動させて、増幅器502の出力信号に振幅変動を生じさせる負荷制御部504cと、を備えている。負荷制御部504cには、負荷変動部503における負荷の大きさに関し、入力信号の同一振幅に対して、任意に選択可能な複数の候補値が設定されている。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

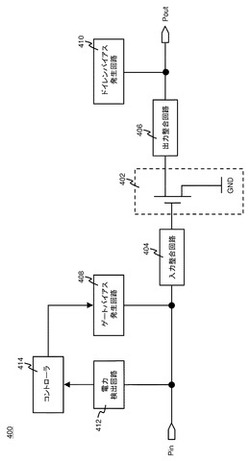

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

完全差動型オペアンプ

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

バランス/アンバランス信号出力回路

【課題】簡易な構成で無駄なくバランス出力とアンバランス出力とを選択的に切り替えて出力する。

【解決手段】バランス/アンバランス信号出力回路は、バランス出力の場合、D/Aコンバータ10,12でそれぞれアナログ正相信号、アナログ逆相信号を生成し、切替スイッチ20,22でバランスHOT端子及びバランスCOLD端子から出力する。アンバランス出力の場合、D/Aコンバータ10,12でそれぞれアナログ正相信号を生成し、切替スイッチ24,26でアンバランス端子から出力する。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

【課題】電力消費量を低下させ、回路面積を縮小した線形性がより高いLNAを提供する。

【解決手段】差動増幅器300の一腕は第1トランジスタ310及び第2トランジスタは320、第1のカスケード対として結合され、第3トランジスタ330及び第4トランジスタ340は、第2のカスケード対として結合される。第3トランジスタ330は、第2トランジスタ320のソースに結合したゲートを有し、第4トランジスタ340は、第2トランジスタ320のドレインに結合したドレインを有する。第3トランジスタ330は、第1トランジスタ310によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子350は、第1トランジスタ310に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2トランジスタ320及び第3のトランジスタ330の大きさは、利得損失を低減させるために選択される。

(もっと読む)

差動増幅回路

【課題】基本波周波数のゲイン変化を生じさせることなく、2次高調波のみを抑圧および低減した回路面積の小さい差動増幅回路の実現。

【解決手段】差動対をなし、差動信号S,ZSが入力される2個のMOSトランジスタTr1,Tr2と、2個のMOSトランジスタTr1,Tr2のドレイン間に直列に接続された2個の容量素子C1,C2と、2個の容量素子C1,C2の接続ノードとバイアス電源端子GND間に接続されたインダクタンス素子L1と、を有する差動増幅回路。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

高周波回路

【課題】 平衡型増幅器を用いて構成され、挿入損失の増大を抑え、回路の大型化を防ぎながらアンテナダイバシティが利用可能な電気的特性に優れた高周波回路を提供する。

【解決手段】

平衡型増幅器とスイッチ回路を備えた高周波回路であって、前記平衡型増幅器は複数の入力ポートと異なるアンテナと接続される複数の出力ポートを有し、各入力ポート及び各出力ポートとグランドとの間に、スイッチ素子と抵抗とを備えた終端回路を有する。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

傾斜増幅器システム

【課題】電力損失を低減するような傾斜増幅器システムの設計を提供する。

【解決手段】傾斜増幅器システムは、その各々が第1の切替え周波数で動作する複数のブリッジ増幅器を有する電力段と、電力段の出力端子に結合され、電力段により供給されるコイル電流信号に比例した磁場を発生する傾斜コイルと、電力段の入力端子に結合され、コイル電流信号及び基準電流信号に基づいてパルス幅変調ゲート信号を生成する制御器段とを含んでおり、基準電流信号に関連付けされたスルーレートが決定されたしきい値レート未満であること並びに基準電流信号に関連付けされた振幅レベルが決定されたレベルを超えることの発生時にパルス幅変調ゲート信号は第2の切替え周波数で生成される。制御器段は、複数のブリッジ増幅器の各々の動作周波数を第1の切替え周波数から第2の切替え周波数に変更するために、発生させたパルス幅変調ゲート信号を電力段に加える。

(もっと読む)

1 - 20 / 152

[ Back to top ]