Fターム[5J500AA27]の内容

Fターム[5J500AA27]に分類される特許

1 - 20 / 472

全差動型帰還増幅回路および電気機器

D級増幅器

スイッチングアンプ

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

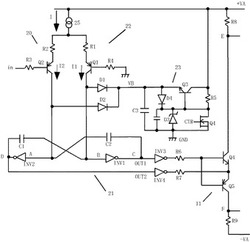

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

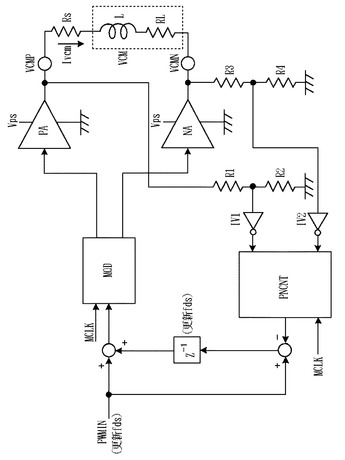

オーディオ装置

【課題】本発明は、オーディオ装置において、スピーカの劣化を防止することを目的とするものである。

【解決手段】本発明は、音声入力端子4と、この音声入力端子4に接続されたPWM変調器7と、このPWM変調器7の出力側に接続された増幅器8と、この増幅器8の出力側に接続されたLCフィルタ9と、このLCフィルタ9の出力側に接続された音声出力端子10とを備え、前記LCフィルタ9にフィルタ電流検出器12、あるいは、スピーカ電流検出器を接続し、これらのフィルタ電流検出器、あるいは、スピーカ電流検出器に制御器13を接続し、この制御器13により前記増幅器8を制御する構成とした。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

スイッチングシステムおよびスイッチングシステムの制御方法

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

デジタルアンプ及びデジタルアンプのテスト方法

【課題】安価な試験装置を用いても、PWM信号のパルス幅を測定可能にするデジタルアンプを提供する。

【解決手段】PWM信号のキャリア周期とPWM信号のパルス幅を測定する際の目標分解能との和に基づく周期であるサンプリングクロックSCLKの第1の論理から第2の論理への遷移に応じて発生させたサンプリング信号SCLKDIV(微分回路21の出力)と、PWM信号との論理積の結果(アンド回路22の出力)をカウントし、カウント結果に基づいてPWM信号のパルス幅を示すカウント値を出力するテスト回路部10bを設けたことを特徴とする。

(もっと読む)

増幅装置、デジタル信号処理装置、及び無線通信装置

【課題】増幅器の出力を複雑なアナログ信号処理を行うことなく取得できるようにする。

【解決手段】 増幅装置1は、増幅器3と、増幅器3によって増幅されるべき信号を出力するデジタル信号処理部2と、増幅器3の出力側に設けられたアナログフィルタ4と、を備えている。デジタル信号処理部2は、増幅器3の出力に基づいて、増幅器3の歪補償を行う歪補償部15と、増幅器3によって増幅されるべき信号に対してΔΣ変調を行って量子化信号を出力するΔΣ変調部25と、を備えている。増幅器3は、量子化信号を増幅し、前記アナログフィルタ4は、量子化信号からアナログ信号を生成する。デジタル信号処理部2は、歪補償部15による歪補償のために、増幅器3から出力された量子化信号を取得する。

(もっと読む)

D級アンプ

【課題】負荷を駆動するトランジスタの駆動能力を落とすことなく、トランジスタの電源である電池の消耗を少なくしたD級アンプを提供する。

【課題の解決手段】D級アンプは、外部電池10の供給電圧から昇圧電圧を生成する昇圧回路20と、電池10を電源として駆動されるその正負極間に直列接続されたPMOSトランジスタ30及びNMOSトランジスタ40と、昇圧電圧及び接地電圧を電源とし入力信号をPWM変調したパルスに基づいて各トランジスタ30,40を交互にオンオフ駆動する駆動回路60と、この駆動回路60の出力端とPMOSトランジスタ30のゲートとの間に接続された容量素子70と、駆動回路60の出力が昇圧電圧であるタイミングで電池10の正電極とPMOSトランジスタ30のゲートとを接続するスイッチ素子80とを備え、各トランジスタ30,40の接続点の電圧に基づき負荷100を駆動する。

(もっと読む)

PWMアンプ

【課題】デットタイム歪みを補償したPWMアンプを提供する。

【解決手段】PWMアンプは、PWM入力信号を受け、デッドタイムを持つ第1駆動パルスと第2駆動パルスを形成するPWM駆動回路と、上記第1駆動パルスを受けて出力端子に第1出力電圧を出力させる第1出力素子と、上記第2駆動パルスを受けて上記出力端子に第2出力電圧を出力させる第2出力素子と、上記PWM入力信号と、かかるPWM入力信号に対応した上記第1出力素子と第2出力素子より形成された出力信号との誤差パルスを検出し、次に入力されるPWM入力信号に上記誤差パルスを加算させるデッドタイム補償回路とを有する

【選択図】図4  (もっと読む)

(もっと読む)

パルス幅変調器および音声信号出力装置

【課題】分解能を向上させることができ、ダイナミックレンジを向上させるパルス幅変調器を提供する。

【解決手段】クロックに同期しながらカウント値をカウントするシーケンスカウンタ24と、入力信号が前記第1の入力信号パターン種である場合はシーケンスカウンタからのカウンタ値を基準に当該入力信号のスイッチング周期の切り換え時間点を中心としてその前後が対称となるようにパルス幅を変化させ、入力信号が第2の入力信号パターン種である場合はシーケンスカウンタからのカウンタ値を基準に当該入力信号のスイッチング周期の切り換え時間点を中心としてその前または後を1クロック分多くパルス幅を変化させて中間レジスタ値として出力する中間レジスタ処理部20と、シーケンスカウンタからのカウンタ値を基準にして中間レジスタ処理部からの中間レジスタ値にしたがって出力信号を生成するデコーダ22とを備える。

(もっと読む)

デジタルアンプ、デジタルアンプの制御方法およびプログラム

【課題】高い処理速度を必要とせず且つ簡単な回路構成にすることができると共に、自身の回路にダメージを与えることなくスピーカーのショート判定を行うことができる。

【解決手段】スピーカー12と接続されて用いられるデジタルアンプ11であって、アナログ音声信号をパルス信号に変調する比較回路23と、変調した音声信号を増幅する増幅回路25と、増幅した音声信号を、アナログ信号に復調しつつ、その高周波成分を減衰するローパスフィルター26と、起動時にテスト信号を入力するミュート切替部29と、テスト信号をローパスフィルターに通した後の残留キャリアレベルを検出するレベル検出部27と、検出したテスト信号の残留キャリアレベルに基づいて、スピーカーがショートしているか否かを判定する制御部31と、を備えた。

(もっと読む)

D級増幅回路

【課題】全差動オペアンプが有するオフセット電圧や抵抗器の抵抗値の相対ばらつきに起因する出力オフセット電圧のキャンセルを可能とする。

【解決手段】出力オフセット電圧キャンセル回路901は、回路起動時から全差動オペアンプ1の出力オフセット電圧の極性に応じて、出力オフセット電圧を零に漸近せしめるべく電圧を全差動オペアンプ1の入力段に印加可能に構成され、コントロールロジック回路113は、回路起動時から全差動オペアンプ1の出力オフセット電圧が零となるまでの出力オフセット電圧キャンセル期間、スイッチ回路115に、第1のフィードバック用抵抗器23を全差動オペアンプ1の反転入力端子と正出力端子との間に、第2のフィードバック用抵抗器24を全差動オペアンプ1の非反転入力端子と負出力端子との間に、それぞれ接続せしめるようになっている。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】駆動用アンプのゲインが変動するのをなるべく抑えて差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、PWM回路22のランプ波発生回路61は、圧電スピーカー15の両端子間の電圧変化分ΔVn(V)に含まれる、インダクタ42にエネルギーをチャージする元のキャパシタ41の両端子間の電圧値Vlp(V)の成分と、圧電スピーカー15の両端子間の電圧値Vn−1(V)=Vspk(V)の成分とを打ち消すような傾きkをもち、かつ、その傾きkにチャージ時間t(μS)の二乗が乗じられた二次のランプ波を発生させる。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】なるべく少ない数のスイッチング素子で差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを抵抗等でなるべく消費させずに、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、ゲートドライバ回路23は、第1フェーズから第4フェーズまでの各動作フェーズに合わせて、スイッチング駆動回路24のPMOSトランジスタ45〜49の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、なるべく少ない数のスイッチング素子で、差動信号の駆動信号を生成して、その駆動信号によって圧電スピーカー15を駆動することができる。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】圧電素子等の容量性負荷にチャージされたエネルギーを無駄に消費することなく、容量性負荷を低消費電力で駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】スイッチング駆動回路24は、容量性負荷である圧電スピーカ15に転送されたエネルギーを抵抗等でなるべく消費させずに、インダクタ42を介してキャパシタ41に再びチャージし、容量性負荷の駆動に再利用する。これにより、圧電スピーカ駆動用アンプ14は、圧電スピーカ15を低消費電力で駆動することができる。その際、圧電スピーカ15を駆動するために必要なエネルギーは、ダイオード48を介して、電源から自動的にキャパシタ41に補充される。従って、ゲートドライバ23は、スイッチング素子の制御を簡潔に行うことができる。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】ゼロクロス付近においてもスイッチングの動作周期に基づく時間内にエネルギーの転送が終了するような駆動信号を生成して、その駆動信号によって容量性負荷を駆動するための各動作フェーズの動作を本来の動作時間通りに行うことのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】ゲートドライバ回路23は、駆動信号VCN,VCPがゼロクロス付近の範囲RZにあるときに、PMOSトランジスタ47,49およびNMOSトランジスタ50,51の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、動作状態を、通常動作状態からゼロクロス動作状態にする。そして、その駆動信号VCN,VCPによって圧電スピーカー15を駆動するための各動作フェーズを、本来のスイッチング動作周期に基づく時間通りに行うことができる。

(もっと読む)

1 - 20 / 472

[ Back to top ]