Fターム[5J500AC44]の内容

Fターム[5J500AC44]に分類される特許

1 - 20 / 53

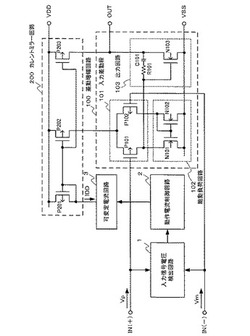

スイッチングアンプ

演算増幅器

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

増幅装置

【課題】 入力される高周波信号のレベルが小さい時はNF特性を十分に向上すると共に、高周波信号のレベルが大きい時は歪特性を十分に向上する。

【解決手段】 TR1のコレクタに接続されているコイルL2(負荷手段)とVccとの間に接続された抵抗R9と、該抵抗R9に並列接続された制御電圧Vgcに応じてオン/オフするTR3と抵抗R8との直列回路とからなるバイアスコントロール部11を備えている。入力信号のレベルが小さい時は、制御電圧VgcによりTR2,TR3がオフすることにより、TR1のバイアスが浅くなってNF特性が向上され、入力信号のレベルが大きい時は、制御電圧VgcによりTR2,TR3がオンすることにより、TR1のバイアスが深くなって歪特性が向上される。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

受信機および高周波増幅器

【課題】高周波増幅器の消費電流の増加を伴うことなく、良好なNFを得ることのできる受信機を提供する。

【解決手段】負荷抵抗としての抵抗R1とこれに直列に接続されたMOSトランジスタM1からなるシングル増幅回路1と、MOSトランジスタM2およびM3からなる差動対を有する差動増幅回路2とから高周波増幅器10を構成する。MOSトランジスタM1のゲートに増幅対象の信号を入力し、シングル増幅回路1の出力をDCバイアスカット用のキャパシタC1を介して差動増幅回路2の差動対の一方のMOSトランジスタM2のゲートに入力し、他方のMOSトランジスタM3は無入力とする。MOSトランジスタM2およびM3からなる差動対の出力信号を、高周波増幅器10の出力信号として出力する。高周波増幅器10のNFが改善されるため受信機100のNFが改善されることになる。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

抵抗式熱検出器にバイアスをかけて読み取るための電子回路

【課題】画素のSN比を改良するために読み取り回路によりもたらされるノイズを低減する。

【解決手段】少なくとも1つの抵抗式熱検出器(102)にバイアスをかけて読み取るための電子回路(100)であって、抵抗式熱検出器の電気抵抗に変動があると、抵抗式熱検出器に一定値のバイアス電流を流すことによって抵抗式熱検出器にバイアスをかけることができるバイアス手段と、抵抗式熱検出器(102)の端子で電圧を電流に変換することができ、抵抗式熱検出器の端子の一つにゲートが電気的に接続させる少なくとも1つのMOS型トランジスタ(106)を備える変換手段と、変換手段のMOS型トランジスタのソースに電気的に接続されるベースクリップ電圧生成手段とを備える電子回路を提供する。

(もっと読む)

並列−直列形電流帰還増幅器、増幅器、及び光学機器

【課題】電流源から出力される電流信号を入力信号とする並列−直列形電流帰還増幅器において、ノイズを低減しつつ、帯域も維持しかつ信号歪も抑制する。

【解決手段】並列−直列形電流帰還増幅器2aは、ベースが電流源の出力端に接続され、エミッタが抵抗20を介して接地端に接続され、コレクタが抵抗12を介して電源配線に接続されるトランジスタ10と、ベースがトランジスタ10のコレクタに接続され、コレクタが電源配線に接続されるトランジスタ30と、ベースがトランジスタ30のエミッタに接続され、エミッタが抵抗22を介して接地端に接続され、コレクタから出力信号が取り出されるトランジスタ11と、一端がトランジスタ11のエミッタに接続され、他端がトランジスタ10のベースに接続される帰還抵抗16と、抵抗20と並列に接続されるキャパシタ21と、抵抗22と並列に接続されるキャパシタ23とを備える。

(もっと読む)

単相差動変換器

【課題】

低雑音の単相差動変換器を提供する。

【解決手段】

単相差動変換器は,第1の出力負荷抵抗と第1の増幅トランジスタとが電源と基準電圧との間に設けられ,第1の増幅トランジスタに単相入力信号が供給され,第1の出力負荷抵抗の第1の増幅トランジスタ側のノードに第1の出力端子が設けられた非反転増幅回路と,第2の出力負荷抵抗と第2の増幅トランジスタとが電源と基準電圧との間に設けられ,第2の増幅トランジスタに単相入力信号が供給され,第2の出力負荷抵抗の第2の増幅トランジスタ側のノードに第2の出力端子が設けられた反転増幅回路と,第1,第2の出力端子に単相入力信号の周波数帯域で高インピーダンスを有する第1,第2のインピーダンス手段を介して共通に設けられた追加電流源とを有する。

(もっと読む)

電流電圧変換回路、光学機器、及び光学ドライブ装置

【課題】ゲインを大きくする場合のノイズの増加及び狭帯域化を抑制する。

【解決手段】電流電圧変換回路は、フォトダイオード1から出力される電流信号を増幅する第1の差動増幅回路10と、第1の差動増幅回路10の出力信号を増幅する第2の差動増幅回路20と、第2の差動増幅回路20の出力信号が入力される反転入力端子を有するオペアンプ30と、オペアンプ30の反転入力端子と出力端子の間に接続された帰還抵抗31とを備える。

(もっと読む)

チョッパアンプ

【課題】

スプリアスを抑制することができるチョッパアンプを提供する

【解決手段】

チョッパアンプは,入力信号にチョッピング信号を乗算する第1のチョッパ回路と,第1のチョッパ回路の出力を増幅するオペアンプと,オペアンプの出力にチョッピング信号を乗算し出力信号を出力する第2のチョッパ回路とを有する。さらに,パルス幅がランダムに変化する擬似ランダム信号を生成する擬似ランダム信号生成回路と,擬似ランダム信号の周波数スペクトラムがヌルになる第2の周波数(f2),または当該第2の周波数(f2)と入力信号の周波数(fin)との和周波数(f2+fin)のいずれかである第1の周波数(f1)を有する第1の信号を擬似ランダム信号に乗算し,チョッピング信号を出力する乗算器とを有する。これにより,出力信号において低周波領域での雑音レベルを低下させることができる。

(もっと読む)

低雑音増幅器およびミキサ

パワー消費に対して制御可能な線形性および雑音指数を有する低雑音増幅器(LNA)システムが提供される。システムは、調節のために2つの制御入力を備える。一方の入力は、実効トランジスタ幅を制御し、他方の入力は、バイアス電流を制御する。実効トランジスタ幅に対する変化が、信号に与えられる利得を変更し、バイアス電流に対する変化が、システムのパワー消費を変更する。より厳密な信号仕様に関して、LNAのインピーダンス整合した誘導縮退変化が提供される。  (もっと読む)

(もっと読む)

共通ゲート共通ソース増幅器

共通ソースおよび共通ゲート増幅器トポロジーを単一の増幅器設計に集積するための技術。一態様において、入力電圧は共通ソース増幅器および共通ゲート増幅器の両方に提供される。前記共通ソース増幅器および前記共通ゲート増幅器の出力電圧は、前記出力電圧に比例するシングルエンド電圧を生成するために、差分ブロックに提供される。例えば、低雑音増幅器(LNA)の設計に適用すると、開示された技術は公知技術よりも改善された雑音特性を提供し得る。  (もっと読む)

(もっと読む)

動的な信号コンタミネーション抑制

自己設定可能な増幅器及び増幅方法は、RF信号に接続される入力部と、RF信号の電力レベルに応答して制御信号を生成するよう構成される出力部とを有するRF信号レベル検出器を有する。制御信号は、制御信号に接続される入力部と、制御信号に応答して負フィードバックを提供するよう構成される出力部とを有するパラメトリック調整回路へ供給される。負フィードバックは、自己設定可能な増幅器の入力部を形成する入力部と、自己設定可能な増幅器の出力部を形成する出力部と、パラメトリック調整回路の出力部に接続される制御ポートとを有するRF増幅器へ供給され、それにより、RF増幅器のパラメータの1又はそれ以上は負フィードバックに応答する。  (もっと読む)

(もっと読む)

増幅回路および無線受信機

【課題】消費電力の増大を抑制しつつ、トランスインピーダンスアンプ自体が発生するノイズを低減する。

【解決手段】ミキサMX後段にオペアンプAPを接続し、オペアンプAPの反転出力端子は、帰還抵抗FR11を介してオペアンプAPの反転入力端子に接続し、オペアンプAPの非反転出力端子は、帰還抵抗FR12を介してオペアンプAPの非反転入力端子に接続し、オペアンプAPの反転入力端子と非反転入力端子との間には、負性抵抗NR1を接続する。

(もっと読む)

増幅器

【課題】トランジスタのダイオード動作によるNFの劣化を軽減する。

【解決手段】NPNトランジスタQ1〜Qn(nは2以上の整数)、抵抗素子R1〜Rn、容量素子C1〜Cnを備える。NPNトランジスタQi(i=1〜n)は、コレクタを負荷抵抗Rcの一端および抵抗素子Riの一端に接続し、ベースを抵抗素子Riの他端および容量素子Ciの一端に接続し、エミッタを接地する。容量素子Ciの他端は、i=1〜nについて共通に入力端INに接続され、入力信号が供給される。負荷抵抗Rcの他端は、電源Vccに接続され、負荷抵抗Rcの一端は、出力端OUTとして出力信号を出力する。

(もっと読む)

CMOS増幅器からフリッカー・ノイズを低減するためのシステム及び方法

【課題】相関低周波ノイズの干渉を低減してデータを取得するためのデータ取得回路を提供する。

【解決手段】データ取得回路(10)は、複数の増幅器(14)を有する複数のデータ・チャンネル(12)と、複数の増幅器(14)にバイアス電圧を供給するバイアス回路(16)とを含む。バイアス回路(16)は、バイアス電圧を発生すると共に、複数の増幅器(14)における相関低周波ノイズを低減するようにバイアス電圧間の関係を設定するように構成される。

(もっと読む)

アナログ回路及び電子機器

【課題】低ノイズと低消費電力を両立できるアナログ回路、電子機器等の提供。

【解決手段】アナログ回路300は、増幅対象信号の周波数が第1の周波数である第1型のオペアンプOP1を有する第1の回路310と、増幅対象信号の周波数が前記第1の周波数よりも低い第2の周波数である第2型のオペアンプOP2を有する第2の回路320を含む。第1型のオペアンプOP1の差動部の差動段トランジスタのチャネル幅をW1aとし、チャネル長をL1aとし、差動部に流れるバイアス電流をIaとし、第2型のオペアンプOP2の差動部の差動段トランジスタのチャネル幅をW1bとし、チャネル長をL1bとし、差動部に流れるバイアス電流をIbとした場合に、W1b×L1b>W1a×L1a、Ia>Ibとなる。

(もっと読む)

可変利得増幅器を内蔵する半導体集積回路

【課題】新規または広帯域で周波数依存性の小さなゲインを持つ可変利得増幅器を提供すること。

【解決手段】可変利得増幅器は、バイアス回路(BC) 1、整合回路(MC)2、可変利得抵抗帰還増幅器(FA)3、出力フォロワ(EA)4を含む。負荷抵抗Rcと帰還抵抗Rfの抵抗値とは協調的に変更される。低雑音増幅器を高ゲインとするため、負荷抵抗Rcの高抵抗とされる際には帰還抵抗Rfも高抵抗とされ、抵抗負帰還増幅器3のクローズドループのフィードバック時定数τfb(cl)≒2π・RfCbe/(1+gmRc)は略一定となり、広帯域で周波数依存性の小さなゲインを持つようになる。低雑音増幅器を低ゲインとするため、負荷抵抗Rcの低抵抗とされる際には帰還抵抗Rfも低抵抗とされる。低抵抗の帰還抵抗Rfによって負帰還量が増大して、低ゲインとされる。負荷抵抗Rcも低抵抗とされフィードバック時定数τfb(cl)は略一定となり、高周波領域でそれ以上ゲインは低下しない。

(もっと読む)

低雑音増幅回路

【課題】入力整合特性と低雑音特性とを満たすことができるMOSFETによる低雑音増幅回路を提供する。

【解決手段】低雑音増幅回路は,信号源に接続された入力端子と,入力端子の入力信号を増幅する増幅ユニットと,入力端子と増幅ユニットとの間に設けられ信号源のインピーダンスと整合する入力インピーダンスをもつ終端回路とを有する。この終端回路は,ドレインに負荷インピーダンス回路が接続されソースに入力端子が接続されたゲート接地トランジスタを有し,ゲート接地トランジスタのソースとドレインとがそれぞれ第1,第2の容量素子を介して増幅ユニットの入力に結合されている。ゲート接地トランジスタに熱雑音が発生したとき,ソースに電圧変動が発生すると共に,ドレインにそのソース電圧変動にゲート接地トランジスタのゲインを乗じた電圧変動が逆相で発生する。よって,ソースの電圧変動とドレインの逆相の電圧変動とを第1,第2の容量素子で増幅ユニットに結合することで,ゲート接地トランジスタの熱雑音の影響を抑制または除去することができる。

(もっと読む)

1 - 20 / 53

[ Back to top ]