Fターム[5J500AC65]の内容

Fターム[5J500AC65]に分類される特許

1 - 20 / 200

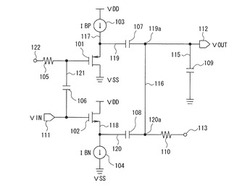

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

駆動回路並びに関連するエラー検出回路及び方法

【課題】

発光装置のための低出力電圧駆動回路が、本発明の例示としての実施形態に従って提供される。

【解決手段】

また、オフセット電圧キャンセル及び/又はレベルシフタが、駆動電流の精度を高くするように駆動回路に組み込まれる。更に、エラー検出回路及び方法は、本発明の駆動回路の最小の出力電圧を検出して対応できるように、用いられる。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

光電変換増幅装置

【課題】本発明は、バースト光信号を受信する光電変換増幅装置において、簡単な構成で高速応答化、広ダイナミックレンジ化及び高感度化を実現することを目的とする。

【解決手段】本発明は、光信号を電気信号に変換するアバランシェフォトダイオード11と、電気信号を増幅する増幅回路素子12と、アバランシェフォトダイオード11のアノードA及びカソードCの間のバイアス電圧を印加するための定電圧を入力するバイアス電圧端子13と、バイアス抵抗14及びバイアス容量15からなるローパスフィルタを構成するバイアス回路と、を備え、アバランシェフォトダイオード11が受信したバースト光信号の強度が変化してから規定の時間の範囲内で、強度変化後のバースト光信号に関するビットエラーレートが規定のビットエラーレートに遷移するように、バイアス抵抗14の値及びバイアス容量15の値が設定されている光電変換増幅装置1である。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

演算増幅回路、液晶パネル駆動装置

【課題】演算増幅回路を安定に動作させつつスルーレートを向上させる。

【解決手段】第1差動増幅部(311)は、P型差動対(P1/P2)のソースと正側電源電圧(VDD)との間に、並列に接続される第1電流源(I1)と第1容量(C1)とを備え、P型差動対(P1/P2)のソースと第1容量(C1)との間に挿入される第1スイッチ(SW1)をさらに備える。第2差動増幅部(312)は、N型差動対(N1/N2)のソースと負側電源電圧(VSS)との間に、並列に接続される第2電流源(I2)と第2容量(C2)とを備え、N型差動対(N1/N2)のソースと第2容量(C2)との間に挿入される第2スイッチ(SW2)をさらに備える。第1スイッチ(SW1)と第2スイッチ(SW2)とは、第1差動増幅部(311)および第2差動増幅部(312)に入力される入力差動信号に同期して交互に回路を開閉する。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

光電変換回路

【課題】広いダイナミックレンジを確保しつつレンジ切換処理による遅延をなくして、レベル変化が激しい場合にも対応可能にする。

【解決手段】フォトダイオード11、演算増幅器12aおよび第1の抵抗12bとで構成され、フォトダイオード11の出力電流と第1の抵抗12bの抵抗値との積に絶対値が等しい電圧を出力する反転アンプ12と、第1の抵抗12bより小さい抵抗値を有し、電源の正側とフォトダイオード11との間に挿入された第2の抵抗21と、第2の抵抗21の両端の電圧を出力する差動増幅器22と、フォトダイオード11と演算増幅器12aの反転入力端子の接続点とアース間に接続され、反転アンプ12が飽和していないときには非導通状態、飽和しているときには導通状態となってフォトダイオード11の出力電流をバイパスさせるダイオード23とを備えている。

(もっと読む)

光受信装置,光局側装置および光ネットワークシステム

【課題】立ち上がり時間短縮と同符号連続耐力の確保とを両立する。

【解決手段】バースト光信号を受光し、バースト光信号の受光レベルに応じた信号を出力する受光部2と、受光部2から出力された信号について増幅出力する増幅部3と、バースト光信号のプリアンブル領域において、増幅部3から出力される増幅後の信号の平均値相当の成分を受光部から出力された信号の直流成分として取り出し、取り出した直流成分を受光部から出力された信号から除去する応答時定数可変の直流成分除去部4a,4bと、前記バースト光信号の立ち上がりを示す信号に基づいて応答時定数を増加させる制御を行なう応答時定数制御部5と、をそなえる。

(もっと読む)

スイッチ制御回路、増幅器、および送信装置

【課題】 増幅素子のバイアス入力部の近傍に大容量のコンデンサが接続された場合であっても、バイアス電圧制御の応答遅れを抑制することが可能なスイッチ制御回路、増幅器、および送信装置を提供する。

【解決手段】 バイアスが印加されることによって増幅作用を発生する増幅素子の前記バイアスのオン/オフを制御するスイッチ制御回路であって、二つのスイッチ素子が相補的に動作するコンプリメンタリ回路を複数並列に接続した回路を含む。

(もっと読む)

スイッチングトランジスタの制御回路

【課題】イネーブル信号をHIGHにしてから急速にスイッチングトランジスタをオンし、かつ突入電流を防止することが可能なスイッチングトランジスタの制御回路を提供すること。

【解決手段】イネーブル信号によりトランジスタM2はオフする。トランジスタM8はオフし、ノードCTの電位はグラウンドと等電位になり、反転器の出力ACTはHIGHとなり、トランジスタM9はオンする。イネーブル信号の反転信号によりトランジスタM5はオフし、トランジスタM3、M4、M6のゲート電位はM4とIBIASで決まる電位VBIASと等電位となってトランジスタM3、M4、M6はオンとなり、並列接続されたトランジスタM3、M6の能力に応じたIGD(大)が流れる。トランジスタM1、M7は、電流IGD(大)によって急速にゲート容量へ電荷が蓄えられて急速にオンになり、電流IOUT、IDETが流れる。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし、差動段を単一導電型に簡素化した構成においても、充電及び放電における出力電圧波形の対称性を実現する。

【解決手段】第1の差動対111、112と、第1のカレントミラー130と、第2のカレントミラー140と、第1の浮遊電流源回路150と、第2の浮遊電流源回路160を備えた差動入力段と、第1導電型の第1のトランジスタ101と、第2導電型の第2のトランジスタ102と、を備えた出力増幅段110と、第1及び第2の電流源121、123と、第3のトランジスタ103と、第4のトランジスタ105と、第3及び第4の電流源122、124と、第5のトランジスタ104と、第6のトランジスタ106とを備えた電流制御回路120とを含む。

(もっと読む)

スイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システム

【課題】精度および高速性能を損なうことなくアンプシェア動作を実現可能なスイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システムを提供する。

【解決手段】複数のスイッチドキャパシタ回路210,220で共有される演算増幅器AMP11を有し、複数のスイッチドキャパシタ回路は演算増幅器の入力および出力と切り離すように複数のスイッチが制御されて複数の容量で第1のアナログ信号をサンプリングするサンプルモードと、サンプリングした容量を演算増幅器の入力および出力と選択的に接続するように複数のスイッチが制御されて、演算増幅器のサンプルモードでサンプリングした信号と第2のアナログ信号との差分を2N倍に増幅するホールドモードとが相補的に設定され、サンプルモード時に演算増幅器の入力および演算増幅器の内部における電圧が固定されていないノードを共通電位にリセットするスイッチswrを有する。

(もっと読む)

差動増幅回路およびシリーズレギュレータ

【課題】 負荷の変動に応じて定電流源に流す電流を変化させて過渡応答特性を高めることができるシリーズレギュレータの電圧制御用差動増幅回路を提供する。

【解決手段】 第1定電流源(Mp0)を有する差動入力段と、差動入力段の出力ノードの電位をゲート端子に受ける出力用MOSトランジスタ(Mn3)およびこれと直列に接続された第2定電流源(Mp3)を有する出力段とを備えた差動増幅回路に、前記第1定電流源または第2定電流源と並列に設けられた定電流用MOSトランジスタと、前記出力用MOSトランジスタと前記第2定電流源との接続ノードの電位がゲート端子に印加されたブースト電流制御用MOSトランジスタとを設け、差動入力段の一方の入力電圧が変化した際にブースト電流制御用MOSトランジスタがオンされて、前記定電流用MOSトランジスタの電流が前記第1定電流源または前記第2定電流源に加算されて差動入力段または出力段に流れるようにした。

(もっと読む)

1 - 20 / 200

[ Back to top ]