Fターム[5J500AC91]の内容

Fターム[5J500AC91]に分類される特許

1 - 20 / 84

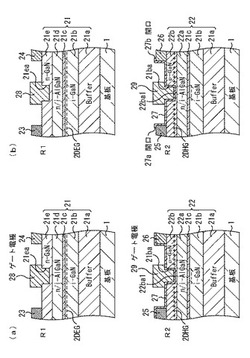

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

ドライバ集積化回路

【課題】プロセスの耐圧を超える電圧が出力でき、要求される装置性能(高速・高電圧)を満足するドライバ集積化回路の構成を提供する。

【解決手段】差動入力回路と、レベルシフト回路と、出力回路が、同一のプロセスで製造され、基板電位(サブ電位)が異なる、3つ以上のチップに分割配置されており、それぞれのチップの基板印加電圧が異なるように設定することにより、プロセス耐圧よりも大きい出力電圧を提供する。

(もっと読む)

広帯域電力増幅器

【課題】出力特性の平坦度が良好な広帯域増幅器を提供する。

【解決手段】第1中心周波数有する第1増幅ユニットと、第1増幅ユニットに並列に配置され、第1中心周波数よりも高い第2中心周波数を有する第2増幅ユニットと、第1増幅ユニットの入力と第2増幅ユニットの入力に接続された電力分配器と、第1増幅ユニットの出力と第2増幅ユニットの出力に接続された電力合成器とを備える広帯域増幅器。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

バイアス回路、LNA、LNB、通信用受信機、通信用送信機、およびセンサーシステム

【課題】温度依存性の低減、電源電圧依存性の低減、電源電圧および負電圧に重畳されている雑音の十分な減衰、製造プロセスの選定自由度の向上、を実現することができるバイアス回路、LNA、LNB、通信用受信機、通信用送信機、およびセンサーシステムを提供する。

【解決手段】ソース端子4が接地されたHEMT1のためのHEMTバイアス回路11であって、両電源型のオペアンプAMP1と、抵抗素子RIと、第1基準電圧源VXと、第2基準電圧源VYとを備え、オペアンプAMP1は、正入力端子がHEMT1のドレイン端子3に接続され、負入力端子が第2基準電圧源VYに接続され、出力端子がHEMT1のゲート端子に接続され、抵抗素子RIは、一方の端子がHEMT1のドレイン端子3に接続され、他方の端子が第1基準電圧源VXに接続されている。

(もっと読む)

デジタルD級オーディオ増幅器

【課題】デジタル化されたオーディオ信号入力を受入れ、デジタル・アナログ変換なしにスピーカのような負荷を駆動するD級オーディオ増幅器を開示する。

【解決手段】この増幅器は、(1)複数のデジタル値の形式のデジタル化されたオーディオ信号を受取る手段と、(2)デジタル値に応じてパルス波形をパルス幅変調する手段と、(3)変調された波形に対して動作し、デジタル化されたオーディオ信号のアナログ表示を発生する復調器とを含む。

(もっと読む)

無線通信用デジタルアフィン変換変調電力増幅器

デジタルアフィン変換変調器及び電力増幅器は、送信機アンテナを駆動する。変調器は、信号に対してアフィン変換を実行し、I,Q空間は複数のセクタにマッピングされる。あるセクタにおける信号は、角度がセクタ境界を規定する2つのベクトルの和として表される。デジタル電力増幅器は、各々が少なくとも2つの増幅器ユニットを含む複数の増幅器セルを含む。所定の信号に対して、各増幅器ユニットは、信号のアフィン変換済みセクタの1つの境界角度に対応する位相を有するクロック信号を選択的に増幅する。各位相クロック信号を受信する複数の増幅器セルの部分集合は、アフィン変換空間における信号を記述する関連するベクトルの大きさに基づいてイネーブルされる。その変調方式は、極性変調の群遅延の不整合や帯域幅の拡張なしで直交変調より高い効率を示す。  (もっと読む)

(もっと読む)

増幅装置

【課題】出力振幅の拡大と消費電力の低減とを両立する。

【解決手段】選択部20は、相異なる正側電源電位V1[+]および正側電源電位V2[+]の何れかを選択する。電位生成回路30は、選択部20が選択した電源電位(V1[+],V2[+])から負側電源電位V3[-]を生成する。増幅器14は、正側電源電位V1[+]および負側電源電位V3[-]を電源として動作し、中間信号SBを増幅した出力信号SCを生成する。制御回路40は、中間信号SBの振幅αBが閾値αTH_Bを下回る場合には正側電源電位V1[+]を選択し、振幅αBが閾値αTH_Bを上回る場合には正側電源電位V2[+]を選択するように、選択部20を制御する。

(もっと読む)

半導体集積回路

【課題】良好な高周波特性を維持しつつ、増幅器の使用周波数帯域切換えが可能な半導体集積回路を提供する。

【解決手段】結合係数k1を有し、互いに並列に接続されるコイルL11及びコイルL12と、コイルL11及びコイルL12に直列に接続されるコイルL13と、コイルL11に並列に接続されるコンデンサC11と、コイルL12に並列に接続されるコンデンサC12と、コイルL11の一端と、コンデンサC11の一端とに接続される入力端子p1と、コイルL12の一端と、コンデンサC12の一端とに接続される入力端子n1と、入力端子p1と、入力端子n1とにそれぞれ逆位相の入力信号を供給する入力信号供給部200とから構成されることを特徴とする半導体集積回路。

(もっと読む)

ミュート回路およびそれを用いたオーディオ処理回路

【課題】振幅レンジを拡大したミュート回路を提供する。

【解決手段】ミュートトランジスタ2は、接地電圧を中心として正負にスイングするミュート対象となるオーディオ信号SOUTが伝搬する信号ライン5と、接地端子との間に設けられた、NPN型バイポーラトランジスタである。ミュート制御回路20は、ミュート状態において、ミュートトランジスタ2のベースに正電圧の制御信号MUTEを出力してミュートトランジスタ2をオンし、非ミュート状態において、ミュートトランジスタ2のベースに負電圧の制御信号MUTEを出力してミュートトランジスタ2をオフする。負電圧生成回路22は、正の電源電圧Vddを受け、負電圧−VNEGを生成する。レベルシフト回路24は、電源電圧Vddと接地電圧のいずれかのレベルをとる制御信号S1を受け、電源電圧Vddと負電圧−VNEGのいずれかのレベルをとる制御信号MUTEにレベルシフトする。

(もっと読む)

半導体集積回路

【課題】回路設計の余裕を拡大すること。

【解決手段】半導体集積回路100は、トランジスタ124a,124bと、検出回路131と、バイアス生成回路132と、を備えている。トランジスタ124aおよびトランジスタ124bは、基板にバイアスが印加される。検出回路131は、トランジスタ124aおよびトランジスタ124bの閾値電圧を検出する。バイアス生成回路132は、検出回路131による検出結果に基づいてバイアスを生成する。

(もっと読む)

増幅回路装置並びにそれを用いた比較回路装置および定電圧出力装置

【課題】印刷などによって低温で生成された場合であっても高速駆動が可能でかつ良好な出力特性を得ることができる増幅回路を提供する。

【解決手段】オペアンプ100は、差動増幅回路110、バイアス回路120、電圧レベルをシフトするレベルシフト回路ユニット150と増幅回路ユニット160からなるソース接地増幅回路140を具備し、すべてのトランジスタを同一プロセスにて簡易に製造できるディプレッション型のトランジスタにて構成する。

(もっと読む)

高周波増幅器及びそれを用いた高周波モジュール

【課題】高周波増幅器の線形性を改善し、広範囲の入力信号に対して高線形特性を持ち、消費電力が少なく高効率で、集積が容易となる、高周波増幅器及び高周波モジュール並びにそれらを用いた移動体無線機を提供する。

【解決手段】高周波増幅用トランジスタのベースに接続されたベースバイアス供給用回路を備えた高周波増幅器において、ベースバイアス供給用回路のみを見込んだ場合のインピーダンスと、高周波半導体トランジスタの入力インピーダンスとが、高周波信号の広範囲の入力レベルにおいて、虚数値が共役(コンジュゲート)になるように回路を構成した。

(もっと読む)

増幅回路

【課題】回路構成を複雑にすることなく、所望の周波数帯域において利得を向上させる増幅回路を提供する。

【解決手段】本発明の増幅回路は、半導体基板3と、前記半導体基板3上に形成され、高周波信号を増幅するトランジスタ1と、前記トランジスタ1のソース電極10sに接続された誘導性リアクタンス素子とを有し、前記誘導性リアクタンス素子は、前記半導体基板1の上方に形成され、有機物で構成される有機誘電体層6と、前記有機誘電体層6の前記半導体基板3側と反対側の面上に形成された配線を有する金属再配線層7とを含み、前記配線の一端は、前記トランジスタ1のソース電極10sに接続され、前記配線の他端は接地され、前記誘導性リアクタンス素子のリアクタンス値は、前記高周波信号の周波数帯域の中心周波数において10Ω以下である。

(もっと読む)

D級増幅回路

【課題】 直流成分カット用のコンデンサが不要であるなどの各種効果が享受可能なD級増幅回路を提供する。

【解決手段】 D級増幅回路は、ソースが電源電位(VDD)とされドレインが第1ノード(N1)に接続された第1トランジスタ(Tr1)と、ソースが基準電位とされドレインが第1ノードに接続された第2トランジスタ(Tr2)と、ソースが第2ノード(N2)に接続されドレインが基準電位とされた第3トランジスタ(Tr3)と、第1・第2ノード各々に接続された第1コンデンサ(C1)と、ソースが第1ノードに接続されドレインが出力端である第4トランジスタ(Tr4)と、ソースが第2ノードに接続されドレインが前記出力端である第5トランジスタ(Tr5)と、を備える。ゲートドライバ(102)は、負荷(70)に正負両方向の電流が流れるように各トランジスタを制御する。この場合、第1コンデンサが負荷に対する電源として機能する。

(もっと読む)

半導体装置

【課題】低い電源電圧で駆動でき、かつ、電源電圧の変動に対して安定な基準電圧を生成するとともに、基準電圧の温度係数が製造工程におけるパラメータの変動に影響されにくい半導体装置を提供することである。

【解決手段】第1のトランジスタのコレクタ端子と第2のトランジスタのエミッタ端子とを接続して出力端子とし、第1のトランジスタのベース端子と第2のトランジスタのベース端子とを接続して第1のベース端子とし、第1のトランジスタと第2のトランジスタとは同一構造であり、第1のベース端子には、第1のトランジスタのエミッタ側pn接合がわずかに順方向バイアスされる動作領域から逆方向バイアスされる動作領域となる範囲の電圧を印加され、供給電圧には、第1及び第2のトランジスタがnpn、又はpnpかによって、正の電圧又は負の電圧を印加される半導体装置。

(もっと読む)

無線アプリケーション用高出力半導体素子および高出力半導体素子の製造方法

無線アプリケーション用の5Wを超える電力で動作する高出力半導体素子(400)は、高出力半導体素子の活性領域(404)を含む半導体基板(402)と、高出力半導体素子の活性領域にコンタクトを提供する、半導体基板上に形成された接触領域(408)と、半導体基板の一部を覆うように形成された誘電体層(412)と、高出力半導体素子に外部接続部を提供するリード線(500、502)と、高出力半導体素子の活性領域とリード線との間の半導体基板上に形成されたインピーダンス整合回路網(510、512)であって、インピーダンス整合回路網は、誘電体層上に形成された複数の導体線(414)であって、活性領域の接触領域に高出力接続部を提供する、接触領域に結合された複数の導体線を含み、該複数の導体線はインピーダンス整合のための所定のインダクタンスを有する、インピーダンス整合回路網とを備える。  (もっと読む)

(もっと読む)

オペアンプ及び表示パネルの駆動装置

【課題】回路のレイアウト面積を小さくすることができるオペアンプ及び表示パネルの駆動装置を提供する。

【解決手段】ソースアンプ121は、差動回路300、カレントミラー回路210、出力回路212を含んで構成されている。差動回路300は、高耐圧のNMOSトランジスタN11A、N11Bがカレントミラー回路210と並列接続された差動対N11と、NMOSトランジスタN13と、を含んで構成されている。シンクアンプは、差動回路302、カレントミラー回路216、及び出力回路218を含んで構成されている。差動回路302は、高耐圧のPMOSトランジスタP12A、P12Bがカレントミラー回路216と並列接続された差動対P12と、PMOSトランジスタP15と、を含んで構成されている。

(もっと読む)

利得調整回路およびD級電力増幅器

【課題】利得調整および広範囲な電圧源にも安定して適用することができる利得調整回路およびD級電力増幅回路を提供する。

【課題を解決するための手段】

利得調整回路100はアナログ入力信号が入力される信号入力端子102、アナログ信号を増幅し電圧源E1が供給される演算増幅器108、演算増幅器108の反転入力端子108aと出力端子108cとの間に接続される第1のT型抵抗回路T123を備える。信号入力端子102と反転入力端子108aとの間に利得調整するための第1の可変抵抗RV1を接続する。演算増幅器108の非反転入力端子108bにはバイアス電圧供給回路130から直流バイアス電圧が供給される。バイアス電圧供給回路130は第1の電圧生成回路132および第2のバイアス電圧生成回路138を備える。第1のバイアス電圧生成回路132は第2の電圧源E2および第2のT型抵抗回路T123aを備え、第2のバイアス電圧生成回路138は第3の電圧源E3および第2の可変抵抗RV2を備える。

(もっと読む)

増幅回路および光変調器用ドライバ回路

【課題】大振幅出力および広帯域周波数特性を確保することができ、特に光変調器のドライバICに適用可能な増幅回路を提供する。

【解決手段】増幅回路は、入力段トランジスタ11と出力段トランジスタ12とを含み、入力された信号を入力段トランジスタ11および出力段トランジスタ12で増幅して出力する多段増幅部10と、多段増幅部10の出力を、該多段増幅部における出力段トランジスタ12の入力に帰還する帰還部20と、を備える。帰還部20は、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを含み、多段増幅部10の出力を、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを介して出力段トランジスタ12の入力に帰還する。

(もっと読む)

1 - 20 / 84

[ Back to top ]