Fターム[5J500AF07]の内容

Fターム[5J500AF07]に分類される特許

81 - 100 / 248

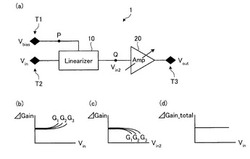

半導体集積回路装置及び送受信システム

【課題】入力信号に対する増幅器の出力信号の利得特性を線形化するために必要な回路の面積を低減できる半導体集積回路装置及び送受信システムを提供する。

【解決手段】半導体集積回路装置は、切り替え可能な複数の第1の利得特性を有し、入力信号に対して前記第1の利得特性を切り替えて中間信号を生成し、第2の利得特性を有する回路に前記中間信号を出力する線形化回路を備え、前記線形化回路は、少なくとも1つの第1の整流素子を有し、前記入力信号を線形化する線形化器と、前記第1の整流素子と逆極性の複数の第2の整流素子と、制御信号に基づき前記複数の第2の整流素子のうち少なくとも1つを選択する第1の切り替え部とを有し、前記線形化器に並列に接続され、前記線形化器による前記入力信号の線形化を抑制する線形化抑制器とを備える。

(もっと読む)

高周波電力増幅器およびその動作方法

【課題】電力増幅電界効果トランジスタのゲート長の依存性による電力利得の変動を軽減する。

【解決手段】高周波電力増幅器は、バイアス制御回路112とカレントミラー接続のバイアストランジスタ516と増幅トランジスタ513と、複製トランジスタ421を有するゲート長モニタ回路101を半導体チップに具備する。513はRF信号を増幅して、516にバイアス制御回路112のバイアス電流が供給される。516、513、421は同一の半導体製造プロセスで形成され、同一のゲート長のばらつきを有する。ゲート長モニタ回路101はゲート長Lに依存した検出電圧Vmonを生成して、検出電圧に従ってバイアス制御回路112がバイアス電流を制御して増幅トランジスタ513のトランスコンダクタンスのゲート長依存性を補償する。

(もっと読む)

電流駆動回路およびそれを用いた発光装置

【課題】高精度な駆動電流を生成可能な電流駆動回路を提供する。

【解決手段】電圧/電流変換回路16は、中間電圧Vmをそれに比例した駆動電流ILEDに変換する。第1抵抗R1は、第1トランジスタM1の一端と接地端子の間に設けられる。第2抵抗R2、第3抵抗R3は、第1抵抗R1と並列な経路に、直列に設けられる。第1演算増幅器OA1は、その第1入力端子に中間電圧Vmが印加され、その第2入力端子に第2抵抗R2と第3抵抗R3の接続点の電圧が印加され、その出力端子が第1トランジスタM1の制御端子と接続される。第1カレントミラー回路CM1は、第1トランジスタに流れる電流を折り返す。第2カレントミラー回路CM2は、第1カレントミラー回路CM1の出力電流を折り返し、駆動電流ILEDを生成する。第2抵抗R2と第3抵抗R3は、その分圧比が調節可能に構成される。

(もっと読む)

エミッタフォロワ型バイアス回路

【課題】GaAs系BiFET(HBT+FET)プロセスを用いた基準電圧発生回路に適した、低い基準電圧で動作できるエミッタフォロワ型バイアス回路を提供する。

【解決手段】エミッタフォロワ型バイアス回路は、増幅段トランジスタTr1,Tr2のベースにバイアス電圧を供給するバイアス回路Bias1,Bias2である。このバイアス回路は、基準電圧を昇圧するデプレションモードFETであるFdb1と、Fdb1により昇圧された基準電圧に応じてバイアス電圧を発生させるエミッタフォロワ回路とを備える。このように基準電圧を昇圧するデプレションモードFETを設けたことで、低い基準電圧で動作できる。

(もっと読む)

誘導コモンモード減結合のあるプッシュプル増幅器

増幅すべき入力信号(e)を出力信号(a)に増幅するためのプッシュプル増幅器が一つの第1の及び一つの第2の増幅素子(1、1’)有する。前記2つの増幅素子(1、1’)のそれぞれが一つの電流放出電極(2、2’)、一つの集電電極(3、3’)、及び一つの電流制御電極(4、4’)を有する。前記増幅素子(1、1’)の前記電流制御電極(4、4’)に、それぞれの入力端子(6、6’)を介して、及び、それぞれの前記入力端子(6、6’)とそれぞれの前記電流制御電極(4、4’)との間に配置されたそれぞれの入力インダクタンス(5、5’)を介して、前記入力信号(e)が供給される。前記集電電極(3、3’)は、それぞれの供給インダクタンス(7、7’)を介して一つの共通の供給電圧(V+)に接続される。前記増幅素子(1、1’)の前記電流放出電極(2、2’)は、それぞれのコンデンサ(8、8’)を介してそれぞれもう一方の前記増幅素子(1’、1)の前記集電電極(3’、3)に接続される。前記電流放出電極(2、2’)は、前記出力信号(a)をピックアップ可能である出力端子(9、9’)に接続される。前記電流放出電極(2、2’)は、それぞれの出力インダクタンス(10、10’)を介して基準電位に接続されている。前記増幅素子(1、1’)の前記供給インダクタンス(7、7’)は、それぞれもう一方の前記増幅素子(1’、1)の前記入力インダクタンス(5’、5)及び前記出力インダクタンス(10’、10)に誘導結合される。  (もっと読む)

(もっと読む)

マルチバンド電力増幅器

【課題】 インピーダンス不整合をなくしたマルチバンド電力増幅器を提供する。

【解決手段】 マルチバンド電力増幅器11の増幅器12,13間には、これらを整合させる段間整合回路14を設ける。また、入力段の増幅器12の入力側に入力段整合回路15を設けると共に、出力段の増幅器13の出力側には出力段整合回路16を設ける。そして、制御回路17は、基地局BSからの周波数設定情報Spによって第1,第2の送信信号TX1,TX2の通信周波数f11〜f1m,f21〜f2nを特定し、この特定した通信周波数f11〜f1m,f21〜f2nに応じて段間整合回路14、入力段整合回路15および出力段整合回路16のインピーダンス値Zm,Zi,Zoを最適な値に調整する。

(もっと読む)

電流源回路及びそれを用いた遅延回路及び発振回路

【課題】簡単な構成でデプレッション型MOSトランジスタの温度特性を補償する電流源回路を提供する。

【解決手段】2つのエンハンスメント型MOSトランジスタQ2、Q3から構成されたカレントミラー回路と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のドレインに接続され、定電流源として機能するデプレッション型MOSトランジスタQ1と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のソースに接続された負の温度特性を有する抵抗と、を含むことを特徴とする。

(もっと読む)

出力回路

【課題】プッシュ側出力トランジスタの駆動回路とプル側出力トランジスタの駆動回路との対称性に優れ、これら出力トランジスタの駆動時における伝達特性の対称性が良好な出力回路を提供する。

【解決手段】電源レールV1と出力端子TOUTとの間に接続されたトランジスタMP1と、出力端子TOUTと電源レールV2との間に接続されたトランジスタMN1と、入力端子に入力される信号と基準電圧との差を増幅するgmアンプAP1と、第1、第2の制御端子及び第1、第2の被制御端子を持ち、電源レールV1とgmアンプAP1の第1の出力端との間に縦積みに接続されたカレントミラー回路CMP1,CMP2と、第1、第2の制御端子及び第1、第2の被制御端子を持ち、電源レールV2とgmアンプAP1の第2の出力端との間に縦積みに接続されたカレントミラー回路CMP1,CMP2とを備える。

(もっと読む)

電力増幅器の有効アクティブ電源インピーダンス修正

電気発生器と非線形負荷との間の相互作用を安定化させるためのシステム、方法、および装置が記述される。一例示的実施形態は、発生器の出力に結合されるインピーダンス要素と、インピーダンス要素に結合される電源とを含む。電源は、通常、インピーダンス要素を介したエネルギー散逸のために生じるようなエネルギー損失を低減させるように、インピーダンス要素に、またはそれにわたって電力を印加する。多くの変形例では、電源は、安定化効果が規定された帯域幅の外において達成されるように、この帯域幅内において動作する。  (もっと読む)

(もっと読む)

利得安定化回路

【課題】 高周波信号が供給されている1パルス期間の間、ハイパワーアンプの利得を一定に保つこと。

【解決手段】 所定の繰り返し周期で間欠的に高周波信号が供給されるハイパワーアンプの利得を一定にする利得安定化回路(100)は、ドレイン電圧(Vdd)が一定の状態で、ハイパワーアンプ(100)のゲート端子に印加されるゲートバイアス電圧を、上記繰り返し周期に同期させて、高周波信号が供給されているパルス期間の間、変動させるゲートバイアス制御回路(120)を備える。それによってハイパワーアンプ(100)のチャンネル温度の変化による利得変動を抑え、ハイパワーアンプ(100)の利得を一定にする。

(もっと読む)

電流電圧変換合成出力装置

【課題】負帰還回路を用いずにDAコンバーターの電流出力を電圧出力に高精度で変換しプッシュプル合成して高品質の信号出力を得る、構成簡易で安価な電流電圧変換合成出力装置。

【解決手段】夫々エミッタ入力・ベース電圧固定(接地)・コレクタ出力動作の第1、第2のトランジスタQ10、Q11と、第1〜第3のカレントミラー回路CM1〜CM3を組み合わせて用いる。 カレントミラー回路CM1、CM2は夫々トランジスタQ10、Q11の各コレクタ出力をカレントミラー電流出力する。カレントミラー回路CM3はカレントミラー回路CM1の出力をカレントミラー電流出力する。カレントミラー回路CM2、CM3の各出力の共通接続点とGND間に、抵抗とコンデンサの並列回路が接続される。DAコンバーターからの互いに極性が逆の電流出力信号を、各トランジスタQ10、Q11のエミッタに入力し、カレントミラー回路CM2、CM3の各出力の共通接続点に電流電圧変換された電圧出力信号を得る。

(もっと読む)

電圧加算回路およびD/A変換回路

【課題】2つのオペアンプの出力端を2つの抵抗を介して接続した構成の電圧加算回路における演算結果の誤差を小さくする。

【解決手段】電圧加算回路50は、2つのオペアンプOP1およびOP2と、オペアンプOP1およびOP2の出力端OUT間に介挿された抵抗raおよびrbとを有する。オペアンプOP1およびOP2の各々の正相入力端IN+には電圧VaおよびVbが与えられ、オペアンプOP1の出力端OUTから電圧VaおよびVbを重み付け加算した電圧Voが出力される。電流供給部51は、オペアンプOP1およびOP2の出力端OUT間に流れる電流と同じ大きさで逆極性の電流をオペアンプOP1の出力端OUTに供給する。

(もっと読む)

D級増幅器

【課題】入力許容電圧の小さな誤差積分値が実装されているD級増幅器を安定的に動作させる。

【解決手段】入力端子101pおよび101nに入力されたPWM入力信号INPおよびINMは、誤差積分器110の正相入力端子111pおよび逆相入力端子111nに接続されたノードVPおよびVMへ入力回路40を介して入力される。入力回路40は、PWM入力信号INPをノードVPに伝達する伝達経路41と、PWM入力信号INMをノードVMに伝達する伝達経路42と、PWM入力信号INPの位相を反転したPWM入力信号/INPをノードVMに伝達する伝達経路43と、PWM入力信号INMの位相を反転したPWM入力信号/INMをノードVPに伝達する伝達経路44とを有する。

(もっと読む)

半導体集積回路装置および電力増幅器

【課題】電力増幅を行う増幅回路のレイアウト面積を低減させながら、トランジスタの熱暴走などを防止し、動作を安定化させる。

【解決手段】パワー段増幅回路4では、ユニットセル81〜8Nに、ベースバラスト抵抗Rb1〜RbNに付加するバイアス回路となるトランジスタQ21〜Q2Nをそれぞれ設けた構成とする。この場合、コントロール電源電圧Vregとトランジスタのエミッタ電圧Ve31の間の電位差は、ベース−エミッタ間電圧Vbeと抵抗Rb1の電圧降下に加えて、トランジスタQ21のベース−エミッタ間電圧Veb31の3つにより支えられ、ベース電流Ib1の増大に伴って、ベース−エミッタ間電圧Vbe31も大きくなり、熱暴走の開始を遅らせることができ、熱暴走の開始電流Icritを増大させることができる。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

周波数変換回路

【課題】変換利得のばらつきを極めて小さく抑制された周波数変換回路を実現する。

【解決手段】入力電圧信号を電流信号に変換するGMアンプ10と、該変換して得られた電流信号をローカル信号でミキシングして周波数変換を行うスイッチング回路部(ミキサ)20と、該周波数変換によって得られた電流信号を電圧信号に変換するIV変換部(IV変換アンプ)30と、GMアンプ10へバイアス電圧を供給するバイアス回路(GM校正回路)40と、を備えGM校正回路40は、GMアンプ10に用いるトランジスタとそのサイズあたりの相互コンダクタンスを同一としたトランジスタを用いたレプリカアンプを内部に有し、該レプリカアンプに、抵抗と第1電流源からの電流との積に相当するDC電圧を入力し、該レプリカアンプからの電流出力が所定値になるように、該レプリカアンプの電圧バイアスを設定し、抵抗の分割点の電圧をGMアンプ10に供給する。

(もっと読む)

差動増幅回路および無線受信機

【課題】消費電流の増大を抑制しつつ、差動増幅回路の線形性と利得の両立を図る。

【解決手段】差動信号Vin、Vinbの一方が入力されるソースフォロア回路を構成する電界効果トランジスタM11と、ソースフォロア回路に直列接続され、差動信号Vin、Vinbの他方が入力されるソース接地回路を構成する電界効果トランジスタM12とを備える。

(もっと読む)

半導体集積回路装置

【課題】回路ゲイン切り替え時における入力端子の入力容量値の変動を低減し、周波数依存性を大幅に改善する。

【解決手段】スイッチ22(0〜N),23(0〜N),24(0〜N)におけるON/OFFの動作制御は、ロジックコントローラから出力される制御信号Ctrl0〜Ctrln,CtrlB0〜CtrlBnによってそれぞれ制御される。スイッチ24(0〜N)は、スイッチ22(0〜N)がON(トランジスタ19(0〜N)がバイアスオフ)する際に、同じタイミングでONとなり、スイッチ22(0〜N)がOFF(トランジスタ19(0〜N)がバイアスオン)する際には、同じタイミングでOFFとなる。トランジスタ24(1〜N)がバイアスオフのときに静電容量素子25(0〜N)が有効になり、回路ゲインを切り換えた時の入力端子INから見た入力容量値Cinの大きな変動を防止することができる。

(もっと読む)

トランスインピーダンスアンプ

【課題】高速信号を処理するトランスインピーダンスアンプの消費電流を低減すること。

【解決手段】差動増幅回路9と、メインTIAコア5及びダミーTIAコア7とを有する。メインTIAコア5は、受光素子1からの電流信号を電圧信号に変換して差動増幅回路9に出力し、ダミーTIAコア7は、基準信号を差動増幅回路9に出力する。ダミーTIAコア7の出力インピーダンスの絶対値は、低周波側では、メインTIAコア5の出力インピーダンスの絶対値よりも高く、高周波側では、メインTIAコア5の出力インピーダンスの絶対値と同様となる。

(もっと読む)

アナログ回路及び半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることを課題の一つとする。

【解決手段】チャネル形成層としての機能を有し、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する酸化物半導体を有する薄膜トランジスタを用いてアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

(もっと読む)

81 - 100 / 248

[ Back to top ]